- •Методичний посібник

- •Правила техники безопасности

- •При выполнении лабораторных работ.

- •Порядок выполнения работы.

- •1. Режим не инвертирующего усилителя – рис. 4.1. Предназначен для усиления сигнала без изменения его фазы. Входное сопротивление схемы в этом режиме очень велико:

- •Порядок выполнения работы.

Порядок выполнения работы.

1. Собрать схему симметричного транзистора мультивибратора по рис. 5.1.

2. При помощи осциллографа наблюдать генерацию схемы при включении питания.

3. Замерить длительность периода колебаний и вычислить частоту при двух различных значениях емкостей С.

4. Зарисовать осциллограммы выходных сигналов при одинаковых и различных емкостях С в коллекторно-базовых цепях транзисторов.

5. Собрать схему несимметричного мультивибратора на цифровых интегральных микросхемах по схеме рис. 5.2.

6. Наблюдать осциллографом генерируемые схемой сигнала при двух различных значениях емкости С.

Произвести замеры длительности периода генерации и вычислить частоту генерации.

7. Зарисовать осциллограммы генерируемых сигналов на выходе схемы.

8. Убедится, что замыкание тумблера S приводит к прекращению генерации.

9. Отключить емкость С и наблюдать высокочастотные колебания мультивибратора. Замерить период колебаний Тм = 1/fм и вычислить время задержки сигнала элементом микросхемы.

Содержание отчета.

Отчет должен содержать:

1. Принципиальные схемы опыта.

2. Тип и параметры используемых транзисторов и микросхем.

3. Тип и основные характеристики используемого осциллографа.

4. Результаты измерения длительности периода и вычисления частоты генерации.

5. Осциллограммы выходных сигналов.

6. Ответы на контрольные вопросы.

Контрольные вопросы.

1. Чем ограничивается величина максимальной частоты генерации мультивибраторов в схеме по

рис. 5.1. и 5.2.?

2. Что такое скважность генерируемых сигналов?

3. Как можно плавно регулировать частоту генерации мультивибратора по рис. 5.1.?

4. Как будет вести себя схема по рис. 5.2. если отключить емкость С?

ЛАБОРАТОРНА РОБОТА № 6.

Исследование интегральных и логических схем и триггеров.

Цель работы: ознакомится на практике с работой некоторых логических схем и триггеров в

интегральном исполнении серии К 561.

Используемое оборудование и аппаратура:

1. Источник питания постоянного тока стабилизированный (5 – 12) В.

2. Цифровые микросхемы К561ЛЕ5, ЛА7, ЛП2, ТМ2, ТВ1, подлежащие исследованию, резисторы 10 – 20 кОм, тумблеры и кнопки.

3. Электронно-лучевой осциллограф или вольтметр постоянного тока с большим входным сопротивлением и пределом измерения, равным напряжению источника питания.

4. Паяльник.

5. Монтажные провода, монтажная плата.

Теоретические сведения.

В лабораторной работе исследуются цифровые логические микросхемы технологии КМОП серии

К561: 2ИЛИ-НЕ (ЛЕ5), 2И-НЕ (ЛА7), исключающие ИЛИ (ЛП2), Д – триггер (ТМ2) и IК – триггер

(ТВ1).

Напряжение питания микросхем этой серии может находится в пределах (13 – 15) В. Входные и выходные сигналы могут иметь только два дискретных значения: Лог.0 (не более 0,2)В и Лог.1 (практически Un). Предельная частота срабатывания микросхем от 1 до 4 МГц соответственно при питании напряжением 3 и 15В. В лабораторной работе сигнал Лог1. на входе микросхемы задается подключением входа к +U, а сигнал Лог.0 – подключением к вертикали. Во избежанием выхода из строя микросхем входы незадействованных элементов микросхемы должны быть подключены к одному из полюсов источника питания.

При работе с микросхемами КМОП технологии следует соблюдать следующие правила. При монтаже микросхемы сначала подключать выводы питания, а потом – логические входы и выходы. Не разрешается подавать сигнал на вход микросхемы, не имеющий напряжения питания. Нельзя оставлять неподключенными входы микросхем. При работе с микросхемами принимать меры для защиты их от статического электричества.

Состояние логических микросхем полностью определяется состоянием сигналов на их входах. Исследование работы микросхем такого типа заключается в задании всех возможных комбинаций состояний логических сигналов на входах микросхемы и определение состояния входа соответствующего каждой комбинации. Для исследуемых двухвходовых логических схем задаются 4 возможных комбинации состояния входных сигналов:

0 0

0 1

1 0

1 1

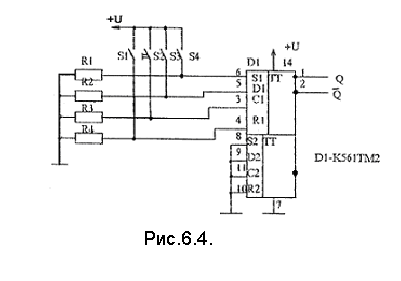

Триггер микросхемы К561ТМ2 содержит два установочных входа R, S, информационный вход D и таковой вход С, а также два парафазных выхода Q, Q. Установочные R, S входы предназначены для установки триггера в одно из 2-ух возможных состояний путем подачи потенциала уровня Лог.1 на один из этих 2-ух входов. Сигнал на тактирующем входе С вызывает установку триггера своим положительным фронтом: триггер устанавливается в одно состояние при наличии Лог.1 на входе D и в другое состояние при наличии Лог 0 на входе D в момент перепада напряжения на тактирующем

входе С. При этом установочные R, S входы являются приоритетными.

I – K триггер микросхемы К651ТВ1 содержит 2 установочных R, S входа, 2 информационных входа

I и K, а также тактирующий вход С. Активностью обладают положительный фронт тактирующего сигнала: Он устанавливает триггер в одно состояние при наличии Лог.1 на входе К. При наличии Лог.1 на обоих входах I и К триггер меняет свое состояние за каждым положительным перепадом тактирующего сигнала.

Порядок выполнения работы.

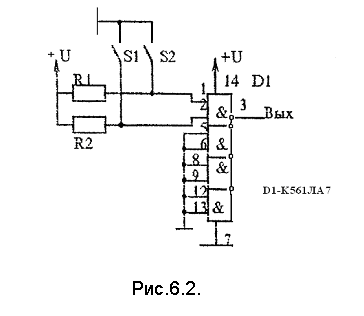

1. Собрать схему по рис. 6.1. Комбинация состояния тумблеров S1, S2, поочередно установить все 4 возможные комбинации входных сигналов элемента 2ИЛИ-НЕ и при вольтметра постоянного тока или электронно-лучевого осциллографа определить состояние выхода элемента, соответствующее каждой из этих комбинаций. Составить таблицу истинности логического элемента 2ИЛИ-НЕ.

2. Сменить микросхему К561ЛЕ5 на К561ЛА7 и проделать аналогичные операции. Составить таблицу истинности логического элемента 2И-НЕ.

3. Установить на монтажную плату микросхему К561ЛП2 и проделать аналогичные операции. Составить таблицу истинности логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ.

4. Собрать схему исследования D – триггера по рис. 6.4. Проверить реакцию триггера на состояние установочных входов R, S и на тактовый сигнал С при различных состояниях информационного входа D. Составить таблицу переходов D – триггера. Таковой сигнал задавать нажатием кнопки S2.

5. Собрать схему исследования I – K – триггера по рис. 6.5. Проверить реакцию триггера на состояние установочных входов R, S и на тактовый сигнал С при различных состояниях информационных сигналов I – K. Составить таблицу переходов I – K – триггера. Таковой сигнал задавать нажатием кнопки S3.

Содержание отчета.

Отчет должен содержать:

1. Принципиальные схемы опытов.

2. Перечень исследуемых микросхем, их основные характеристики.

3. Тип и основные характеристики используемых контрольно-измерительных приборов.

4. Результаты замера величины напряжения питания, уровень Лог.0 и Лог.1 на выходах микросхем.

5. Таблицы истинности исследуемых логических схем и таблицы переходов исследуемых триггеров.

6. Выводы, сравнение D и I – K – триггеров, ответы на контрольные вопросы.

Контрольные вопросы.

1. Как осуществить логическую операцию ИЛИ-НЕ при наличии микросхем И-НЕ?

2. Как будет манятся состояние триггера микросхемы К561ТВ1 при подаче на тактирующий вход С серии прямоугольных импульсов, если на входах R, S, I, K присутствует сигнал Лог.0?

3. Составьте схему симметричного RS триггера из логических элементов И-НЕ?

ЛАБОРАТОРНА РОБОТА № 7

Исследование интегральных счетчиков дешифраторов.

Цель работы: ознакомится с работой двоичного интегрального счетчика и двоично-десятичного дешифратора.

Используемое оборудование и аппаратура:

1. Источник питания постоянного тока стабилизированный (5 – 12) В.

2. Цифровые микросхемы К561ЛА7, К561ИЕ10, К561ИД1, резисторы 10К, 100К, конденсатор

1000 пф, кнопка.

3. Электронно-лучевой осциллограф.

4. Паяльник.

5. Монтажные провода, монтажная плата.

Теоретические сведения.

В

работе исследуется двоичный счетчик

К561ИЕ10.

Счетчик подсчитывает импульсы, поступающие

на вход С.

(см. рис. 7.1.) от генератора импульсов.

Срабатывание счетчика происходит по

заднему фронту входного импульса при

наличии Лог.1 на разрешающем входе Е.

Возможна работа счетчика при наличии

Лог.0 на разрешенном входе Е,

но срабатывание счетчика в этом случае

будет происходить по переднему фронту

входных импульсов. Вход спроса R

является преобладающим по отношению

к другим входам. С целью исключения

выхода из строя микросхемы D2

вход 7

в исходном состоянии через резистор

R2

подключен к общей

цепи нулевого потенциала. На выходе

микросхемы D2

сигналы меняются

по двоичной системе 1

– 2 – 4 – 8 .Таким

образом, емкость этого счетчика составляет

![]()

Где n = 4 – разрядность счетчика.

Дешифратор D3 преобразует двоичный параллельный код, поступающий от счетчика D1 в десятичный код на своем выходе. В каждый момент сигнал существует только на одном из выходов 0, 1,…..9 дешифратора при расшифровки состояний счетчика от 1 до 10. При нахождении счетчика в состояниях от 11 до 16 сигнал на выходах дешифратора D3 отсутствует.

Порядок выполнения работы.

1. Собрать схему по рис. 7.1. Показать ее преподавателю.

2. При помощи электронно-лучевого осциллографа убедится в наличии импульсов на выходе генератора. Заменить частоту этих импульсов.

3. Нажать на кнопку S1 СБРОС и осциллографом убедится в сброшенном состоянии счетчика по наличии потенциалов низкого уровня на всех выходах счетчика при нажатой кнопке.

4. Отпустить кнопку S1. Осциллографом наблюдать динамический сигнал на входах счетчика. Зафиксировать форму и частоту сигнала на выходах всех четырех разрядов.

Убедится, что сигнал сброса является приоритетным.

5. Осциллографом наблюдать динамический сигнал на выходах дешифратора D3. Зафиксировать форму сигнала по отношению к выходным сигналам счетчика.

6. Нарисовать временную диаграмму работы счетчика и дешифратора.

Содержание отчета.

Отчет должен содержать:

1. Принципиальную схему опыта.

2. Тип и основные характеристика используемого осциллографа.

3. Осциллограммы сигналов генератора, счетчика и дешифратора.

4. Выводы, ответы на контрольные вопросы.

Контрольные вопросы.

1. Что надо делать с неиспользуемыми входами микросхемы КМОП технологии?

2. Объясните временную диаграмму дешифратора в схеме рис. 7.1.?

3. Как работают счетчики в коде Джонсона?

4. Нарисуйте схему десятичного счетчика К561ИЕ8?

![]()

ЛАБОРАТОРНАЯ РАБОТА № 8

Исследование двоичного сумматора.

Цель работы: ознакомится с работой интегрального 4-ехразрядного двоичного сумматора.

Используемое оборудование и аппаратура:

1. Источник питания постоянного тока стабилизированный (5 – 12) В.

2. Электронно-лучевой осциллограф или вольтметр постоянного тока с большим внутренним сопротивлением.

3. Паяльник.

4. Монтажные провода, монтажная плата.

Теоретические сведения.

Сумматоры двоичных чисел являются основой арифметических вычислительных схем. Исследуемая интегральная микросхема К561ИМ1 – это сумматор двух четырехразрядных двоичных чисел. Сумматор имеет 4 пары входов АО, ВО – А3, В3, на которые подаются два 4-ехразрядных слова А и В. От предшествующего по разрядности сумматора на выход Свх можно принимать сигнал переноса. Структурно микросхема содержит 4 полных одноразрядных сумматора и схему ускоренного переноса. Такая структура повышает быстродействие многоразрядных арифметических схем, состоящих из нескольких микросхем ИМ1. Микросхема имеет 4 выхода SO – S3 результатов суммирования в разрядах и вход переноса Свых.

Логика работы одноразрядного сумматора поясняется нижеследующей таблицей состояний:

|

Входы |

Выходы |

|||

|

А |

В |

Свх |

S |

Cвых |

|

0 0 0 0 1 1 1 1 |

0 0 1 1 0 0 1 1 |

0 1 0 1 0 1 0 1

|

0 1 1 0 1 0 0 1 |

0 0 0 1 0 1 1 1 |

Микросхемы ИМ1 позволяют строить сумматоры на любое количество разрядов путем последовательного соединения по сигналам переноса С: выход предыдущего на вход последующего разряда. В самом младшем разряде сумматора вход Свх микросхемы подключается к низкому уровню напряжения.

Порядок выполнения работы.

1. Получить от преподавателя значения 4-разрядных двоичных кодов, подлежащих суммированию.

2. Подключить входы микросхемы (рис. 8.1) в соответствии с заданными кодами. Показать схему преподавателю.

3. Включить питание и при помощи осциллографа или высокоомного вольтметра определить состояние выходов SO – S3, Свых. Измерение провести при двух значениях входного сигнала переноса Свх: «Лог.0» и «Лог.1».

4. Зафиксировать результаты в таблице.

Содержание отчета.

Отчет должен содержать:

1. Принципиальную схему опыта применительно к заданным кодам суммируемых чисел.

2. Тип и основные характеристики используемого осциллографа или вольтметра.

3. Описание назначение всех выводов исследуемой микросхемы.

4. Таблицу результатов исследования.

5. Объяснение полученных результатов, ответы на контрольные вопросы.

Контрольные вопросы.

1. Что такое схема усиленного переноса в сумматоре?

2. Нарисуйте схему 8-разрядного сумматора на микросхемах К561ИМ1?

3. О чем свидетельствует появление сигнала на выходе Свых микросхемы ИМ1?

ЛАБОРАТОРНАЯ РАБОТА №9.

Исследование однофазного двухполупериодного выпрямителя

с фильтром

Цель работы: экспериментальное исследование характеристик мостового выпрямителя переменного тока с различными видами сглаживающих фильтров, освоение методики исследования и расчета выпрямителя.

Используемое оборудование и аппаратура :

1. Миллиамперметр постоянного тока,

2. Вольтметр постоянного и переменного тока,

3. Электронно-лучевой осциллограф,

4. Исследуемый выпрямитель и фильтры,

5. Электрический паяльник,

6. Монтажные провода.

Теоретические сведения.

Основными электрическими характеристиками выпрямителя переменного тока являются:

1. среднее значение выпрямленного тока в нагрузке Id,

2. среднее значение выпрямленного напряжения Ud,

3. вторичное напряжение трансформатора U2,

4. первичное напряжение U1,

5. коэффициент трансформации n = U1/U2,

6. мощность нагрузки Pd = Ud Id,

7. действующее значение тока вторичной обмотки I2,

8. действующее значение тока первичной обмотки I1,

9. расчетное значение мощности вторичной обмотки S2,

10. расчетное значение мощности первичной обмотки S1,

11. типовая мощность трансформатора Sт,

12.

коэффициент полезного действия

![]() ,

,

13. амплитуда основной гармоники выпрямленного напряжения Ud1m,

14. коэффициент пульсации по основной гармонике q1,

15. ток через винтель Ia,

16. амплитуда обратного напряжения на винтеле Uвm,

17. частота пульсаций по основной гармонике fn1,

18. внешняя характеристика – зависимость Ud = f (Id).

Для исследуемой двухполупериодной мостовой схемы выпрямления с активной нагрузкой характерны следующие выражения для основных характеристик.

Среднее значение выпрямленного напряжения в зависимости от вторичного напряжения трансформатора:

![]()

![]()

![]()

Соответственно:

![]()

![]()

![]()

Коэффициент трансформации трансформатора:

![]()

Амплитуда пульсации первой (основной) гармоники выпрямленного напряжения при отсутствии фильтра.

![]()

Коэффициент пульсаций по первой гармонике

![]()

Частота пульсаций основной гармоники

![]()

где f = 50 Гц – частота питающей сети

Максимальное обратное напряжение на вентиле:

![]()

![]()

![]()

Средний ток через каждый вентиль:

![]()

![]()

Действующее значене тока во вторичной обмотке трансформатора:

![]()

где Rн – сопротивление активной нагрузки.

Ток первичной обмотке трансформатора:

![]()

![]()

Амплитуда обратного напряжения на вентиле:

![]()

![]()

Амплитуда прямого тока вентиля:

![]()

Мощности первичной и вторичной обмоток, а следовательно, и расчетная мощность трансформатора:

![]() т

т![]()

Порядок выполнения работы.

Собрать схему выпрямителя по рис 9.1, используя детали и приборы, выданные преподавателем. После проверки схемы преподавателем подать напряжение на первичную обмотку трансформатора. При полностью введенном Rн~ произвести замеры и зафиксировать характеристики выпрямителя: Ud, Id, осциллограммы U2, Ud и напряжение на одном из диодов выпрямительного моста.

Меняя Rн_ снять внешнюю характеристику выпрямителя Ud = f(Id) без сглаживающего фильтра.

Подключить емкость Сф1 сглаживающего фильтра и повторить все измерение при двух различных значениях Сф (рис 9.2).

Подключить LC сглаживающий фильтр, содержащий досель Lф и ранее используемую емкость Сф (рис 9.3.). Повторить замеры.

Содержание отчета.

Отчет должен содержать:

1. Принципиальную схему исследуемого выпрямителя,

2. Перечень используемых измерительных приборов и их основные характеристики,

3. Таблицу результатов замера,

4. Графики внешних характеристик выпрямителя без фильтра и с различными сглаживающими фильтрами,

5. Осциллограммы выпрямительного напряжения без фильтра и с фильтрами,

6. Выводы по результатам исследований, ответы на контрольные вопросы.

Контрольные вопросы.

1. Сравните двухполупериодную мостовую схему выпрямителя со схемой с средней точкой вторичной обмотки трансформатора?

2. В каких случаях используют последовательное соединение диодов в схемах выпрямителя?

3. Почему увеличивается выпрямительное напряжение при подключении сглаживающего фильтра?

ЛАБОРАТОРНАЯ РАБОТА №10

Исследование полупроводниковых стабилизаторов напряжения.

Цель работы: экспериментальное определение характеристик полупроводниковых параметрического

и компенсационного интегрального стабилизатора напряжения постоянного тока.

Используемое оборудования и аппаратура:

1. Источник постоянного напряжения величиной (8 – 10) В,

2. Исследуемое параметрический и компенсационный стабилизатор,

3. Миллиамперметр, постоянного тока,

4. Вольтметр постоянного тока – 2шт.,

5. Паяльник,

6. Монтажные провода.

Теоретические сведения.

Наиболее простой схемой стабилизации напряжения является схема параметрического стабилизатора на базе стабилизатора – рис. 10.1. Работа стабилизатора описывается выражением:

![]()

где Uст = Uн = const.

При этом ток Iст через стабилизаторы должен находится в пределах Iст min – Iст max,допускаемых стабилизатором.

Стабилизатор поддерживает стабильное напряжение на выходе при изменении Uвх и (или) Rн.

Коэффициент стабилизации по напряжению:

![]()

где

![]() Uвх

и

Uвх

и

![]() Uн

– изменения входного напряжения и

напряжения на нагрузке, а Uвх

и Uн

– номинальное

значение входного и выходного напряжения.

Uн

– изменения входного напряжения и

напряжения на нагрузке, а Uвх

и Uн

– номинальное

значение входного и выходного напряжения.

Коэффициент стабилизации параметрического стабилизатора не превышает 50.

Технические параметры исследуемого стабилизатора Д815А

-номинальное напряжение стабилизации 5,6 В,

-минимальный ток стабилизации 1400мА,

-максимальный ток стабилизации

-разброс напряжения стабилизации от 5,0 до 6,2 В,

-температурный коэффициент напряжения стабилизации 0,045/К

-рассеиваемая мощность 8 Вт.

Более высокими коэффициентами стабилизации обладают компенсационные стабилизаторы, представляющие собой системы автоматического регулирования (рис 10.2.). В последнее время промышленностью освоен широкий ассортимент компенсационных стабилизаторов напряжения в интегральном исполнении. Условие нормальной работы таких стабилизаторов является надежные Uвх и Iн в пределах оговоренных в паспортных данных микросхемы.

Технические параметры интегрального комплексного стабилизатора КР142ЕН5Г с фиксированным значением Uст:

-

номинальное напряжение стабилизации 6 В,

-

разброс напряжений стабилизации от 5,8 до 6,2 В,

-

максимальный выходной ток 2000мА,

-

коэффициент нестабильности по напряжению не более 0,05/ В,

-

коэффициент нестабильности по току 2 А,

-

температурный коэффициент напряжения стабилизации 0,03. К,

-

минимальное падение напряжения на стабилизаторе 2,5 В,

-

диапазон входных напряжений (0,5 – 15,0) В,

-

рассеиваемая мощность 10 Вт.

Порядок выполнения работы.

1. Собрать схему параметрического стабилизатора на стабилитроне по рис.10.1.

Меняя сопротивление нагрузки при помощи R~ снять внешнюю характеристику схемы

Uст = f (Iн).

2. Собрать схему комплексного стабилизатора по схеме рис. 10.2.

Меняя сопротивление нагрузки Rн ~ снять внешнюю характеристику Uст = f (Iн).

Содержание отчета.

Отчет должен содержать:

1. Принципиальные схемы стабилизаторов, подвергаемых исследованию.

2. Технические характеристики используемых стабилизаторов и микросхемы.

3. Перечень используемых приборов и их технические характеристики.

4. Таблицу результатов замера.

5. Графики внешних характеристик стабилизаторов.

6. Выводы по работе, ответы на контрольные вопросы.

Контрольные вопросы.

1. Можно ли соединять стабилитроны последовательно и параллельно?

2. Как изменится ток через стабилитрон в схеме рис. 10.1. если разорвать цепь нагрузки?

3. Как вычислить мощность, рассеиваемую на стабилитроне в схеме рис. 10.1. и на микросхеме DA в схеме рис. 10.2.?

ЛАБОРАТОРНАЯ РАБОТА № 11.

Исследование схемы сравнения кодов.

Цель работы: ознакомится с работой интегральной схемы сравнения двух двоичных кодов.

Используемое оборудование и аппаратура:

1. Источник питания постоянного тока стабилизированный (5 – 12) В.

2. Микросхема К561ИП2.

3. Электронно-лучевой осциллограф или вольтметр постоянного тока с большим внутренним сопротивлением.

4. Монтажная плата, соединительные провода.

Теоретические сведения.

Сравнение

чисел, выраженных в двоичном коде,

является широко распространенной

операцией в технике преобразования

цифровых сигналов. Исследуемая в работе

микросхема К561ИП2

является схемой сравнения двух 4 – ех

разрядных двоичных чисел А

и В

по логике «больше-меньше-равно». Задание

логики сравнение осуществляется по

входам управления Е![]() ,

Е =,

Е

,

Е =,

Е![]() путем подачи потенциала низкого уровня

на один из выбранных входов и потенциала

низкого уровня на другие, не используемые

входы. Так, на рис. 11.1. показано включение

микросхемы для сравнения чисел по логике

«равно». В этом случае информационным

входом является выход А

= В, на котором

появится сигнал высокого уровня, если

все заряды сравниваемых чисел будут

равны между собой: АО

= ВО, А1 = В1, А2 = В2, А3 = В3.

путем подачи потенциала низкого уровня

на один из выбранных входов и потенциала

низкого уровня на другие, не используемые

входы. Так, на рис. 11.1. показано включение

микросхемы для сравнения чисел по логике

«равно». В этом случае информационным

входом является выход А

= В, на котором

появится сигнал высокого уровня, если

все заряды сравниваемых чисел будут

равны между собой: АО

= ВО, А1 = В1, А2 = В2, А3 = В3.

На

рис. 11.2. показано включение микросхемы

для сравнения чисел по логике «больше».

В этом случае информационным входом

является выход А![]() В,

на котором появится сигнал высокого

уровня, если многоразрядное число А

будет больше

числа В.

В,

на котором появится сигнал высокого

уровня, если многоразрядное число А

будет больше

числа В.

Установка сравниваемых чисел осуществляется по входам А(К1) (0, 1, 2, 3) и В(К2) (0, 1, 2, 3) путем подачи сигналов «Лог.0» или «Лог.1».

Путем каскадного соединения нескольких микросхем можно произвести сравнение нескольких чисел с количеством разрядов больше 4-ех, используя управляющие входы Е.

Порядок выполнения работы.

1. Собрать схему по рис. 11.1. Показать ее преподавателю.

2. Установить равенство сравниваемых чисел путем соединения точек В, С схемы. При этом коды обоих чисел будут равны 0000. При помощи осциллографа убедится в наличии «Лог.1» на входе А = В.

3. Соединить точку С схемы с точкой А. При этом код числа А будет равен 1000, а числа В – 0000, т.е. число А станет больше числа В. Убедится что «Лог.1.» с выходом А = В исчезла.

4. Переключить микросхему на сравнение чисел по логике «больше» как показано на рис. 11.2.

5.

Меняя значение младшего разряда числа

А

убедится, что сигнал «Лог.1» на выходе

А![]() В

появляется только если значение числа

А

станет больше числа В.

В

появляется только если значение числа

А

станет больше числа В.

Содержание отчета.

Отчет должен содержать:

1. Принципиальную схему опыта.

2. Тип и основные характеристики используемого осциллографа или вольтметра.

3. Описание назначения всех выходов микросхемы.

4. Ответы на контрольные вопросы.

Контрольные вопросы.

1. Нарисуйте схему определения равенства двух 12-ти разрядных двоичных чисел?

2. Нарисуйте схему фиксации кода 01101 в 5-тиразрядном двоичном цифровом сигнале?

ЛИТЕРАТУРА.

1. Забродин Ю.С. «Промышленная электроника». – М : Высшая школа, 1982

2. «Основы промышленной электроники» Под ред. В.Г. Герасимова. – М : Высшая школа, 1986.

3. Исаков Ю.А. и др. «Основы промышленной электроники» - К : Техника. 1976.

4. Краснопрошина А.А.. Скаржепа В.П.. Кравец П.И. «Электроника та микросхематехника»

- К : Высшая школа 1989.

5. Криштафович А.К., Трифонюк В.В. «Основы промышленной электроники» М : Высшая школа 1989.

6. Шило В.Л. «Популярные цифровые микросхемы» М : Радио и связь 1988.

7. Гранитов В.И. «Физика полупроводников и полупроводниковые приборы» М : Советское радио, 1977

8. «Применение интегральных микросхем». Под ред. А. Уильямса. Перевод с англ. М : Мир, 1987.

9. «Интегральные микросхемы». Справочник. Под ред. Б.В. Тарабрина. М : Энергоатомиздат, 1985.

10. Иванов В.И., Аксенов А.И. Юшин А.М. «Полупроводниковые оптоэлектронные приборы». Справочник. М : Энергоатомиздат, 1989.

11. «Полупроводниковые приборы». Справочник. Под ред. А.В. Голомедова. – М : Радио и связь, 1983.

12. Щербаков В.И. Грездов Г.И. «Электронные схемы на операционных усилителях». – К : Техника 1983.

13. «Источники питания радиоэлектронной аппаратуры». Справочник. Под ред. Г.С. Найвельта – М : Радио и связь, 1985.

14. «Источник вторичного электропитания». Справочное пособие. Под ред. Ю.И. Конева. – М : Радио и связь, 1983.

15. Фолкенберри Л. «Применение операционных усилителей и линейных ИС. – М : Мир, 1985.