Лекция 2

Многообразие архитектур компьютерных систем для высокопроизводительных вычислений

После предварительного знакомства с тематикой высокопроизводительных систем понятно, что достижение высокой эффективности вычислительных программ зависит от многих факторов: архитектуры компьютера, его аппаратных особенностей, компиляторов, с помощью которых создается программа, алгоритма. Например, имея в распоряжении компьютер с огромным числом параллельных или векторных процессоров, но, не сумев распараллелить задачу или представить в виде векторных операций, никакого ускорения можно не получить. В нашу задачу входит рассмотреть эти составляющие и проанализировать их вклад в эффективность высокопроизводительных вычислений.

Начнем с изучения архитектурных особенностей. Прежде всего, все процессоры можно разделить на универсальные процессоры и спецпроцессоры. Процессоры, построенные специально для решения узкого класса задач, с учетом особенностей таких этих задач, как номенклатура необходимых операций, строение и объем памяти. Так, например, спецпроцессор может содержать аппаратную реализацию операции saxpy (single A*X+Y) или операцию ска-

лярного умножения векторов ∑ai bi , аналого-цифрового преобразования сигналов или

генераторы случайных чисел и т.д. В универсальном процессоре те же операции выполняются обычным образом, по разработанной пользователем программе. При этом спецпроцессоры на узком классе задач могут достигать очень высокой производительности.

Вкачестве примеров можно привести спецпроцессоры фирм Analog Devises (ADSP), Texas Instruments и др., прекрасно реализующие задачи преобразования Фурье, обработки аналоговых сигналов.

Если рассматривать процессоры с точки зрения параллелизма на уровне операций (Instruction-Level Parallelism), то здесь выделяют две основных архитектуры: суперскалярную и VLIW (Very Large Instruction Word). Скалярным называется процессор, содержащий один конвейер. Суперскалярным процессором называют процессор, в котором более одного конвейера. В настоящее время даже "обычные" процессоры, как правило, относятся к этому классу. Процессоры, начиная Pentium, являются суперскалярными (Pentium –два конвейера, Pentium Pro – Pentium III и Celeron содержат по три конвейера, а Pentium IV – четыре конвей-

ера [2]). Особенность супперскалярных процессоров в рамках рассматриваемого параллелизма в том, что программа не несет никакой информации о возможном распараллеливании команд [1]. Задачу распараллеливания и организации конвейеризации должна решать аппаратура процессора.

Вподходе VLIW команды процессора состоят из полей, каждое из которых отвечает за свою операцию и, таким образом [1], уже в потоке команд заложено, какие устройства процессора будут участвовать в команде. Для компьютеров с VLIW-процессором компилятор должен выявлять параллелизм К таким процессорам можно отнести процессоры компьюте-

ров AP-120B (фирма Floating Point Systems, 1976), Multiflow, Cydra.

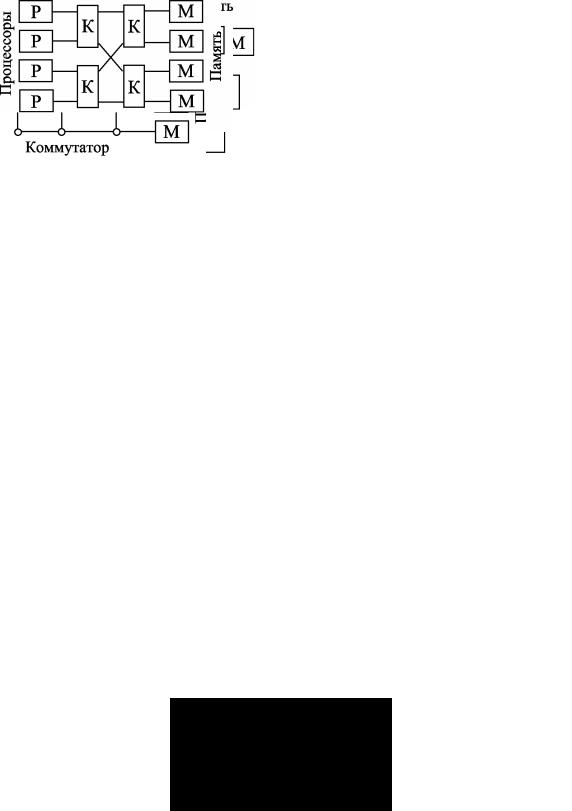

Следующий признак, по которому можно классифицировать высокопроизводительные компьютеры – это связь процессора с памятью. Параллельные системы по этому признаку можно разделить на два больших класса: системы с разделяемой памятью и системы с распределенной памятью. В первом классе несколько процессоров используют одну общую память. Этот класс компьютеров называют SMP (Symmetric Multi Processors). Ко второму классу относятся компьютеры, процессоры которых работают со своими собственными памятями. Схематично рассматриваемые архитектуры показаны на рис. 2.1 и 2.2.

Для SMP-компьютеров нет необходимости в специальной коммуникационной среде для обмена данными между процессорами и процессами. Обмен осуществляется через общую память. Все процессоры SMP-компьютера имеют равноправный доступ к памяти и, по-

2

этому, один процессор может записать данные в определенную ячейку памяти, а другой с такой же скоростью считать эти данные. Для обеспечения равноправного доступа к общей памяти используются различные схемы и системы арбитража. Самой простой схемой соединения нескольких процессоров с общей памятью является общая шина.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис.2.2 – Система с распределенной памятью |

||||

|

Рис. 2.1 – MP-система |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 2.3 – Система с общей шиной |

Рис. 2.4 – Система с коммутатором |

|

Суть этой схемы в том, что все процессоры системы и их общая память подключены к общей шине, объединяющей каналы управления доступом к данным и каналы передачи данных. Главным недостатком систем с общей шиной является то, что число процессоров, подключаемых к общей шине, не может быть большим. Это связано с тем, что нагрузочная способность общей шины ограничена, с ростом числа процессоров растет и время задержки обращения к памяти. Таким образом, говорят, что архитектура систем с общей шиной имеет плохую масштабируемость. Под масштабируемостью подразумевают способность системы к увеличению числа параллельных процессоров. Но при малом количестве процессоров, простота такой архитектуры является преимуществом.

Другая схема – использование матричного коммутатора (рис. 2.4). В этой схеме память разделяют на независимые блоки, которые соединяют с процессорами через коммутатор. При этом коммутатор может соединить любой процессор с любым блоком памяти. Вместе с этим преимуществом схема с коммутатором имеет недостаток, заключающийся в большом объеме необходимого оборудования. В системе с N процессорами и N блоками памяти коммутатор должен иметьN × N переключателей.

Рис. 2.5. Система с омега-сетью

Высокопроизводительные вычислительные системы и параллельное программирование. Кудерметов Р.К.

3

Для уменьшения числа переключателей применяют схемы с каскадными переключателями. На рис. 2.5 показана схема, которая построена на коммутаторах 2×2. Эта схема называется омега-сетью [1]. Для соединения N процессоров с N блоками памяти необходимо (N log2 N )/ 2 коммутаторов 2×2, что, конечно, меньше по сравнению с N ×N , однако в этой схеме задержка при обращении к памяти больше, чем у предыдущей схемы. Вообще же существует множество разновидностей схем на коммутаторах n×m, известны коммутатор Клоза (C. Clos), баньян-сети, дельта сети. Существуют и другие схемы соединения процессоров с памятью в системах SMP.

Для соединения между процессорами в системах с распределенной памятью могут использоваться выше приведенные схемы, т.е. общая шина, коммутаторы, сети. Кроме того, имеются и другие схемы соединений. Так, процессоры можно расположить в виде линейки, кольца или звезды (рис. 2.6 а, б, в). Будем называть схемы соединения процессорных узлов топологиями.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

а |

|

|

|

|

|

б |

|

|

|

|

|

в |

Рис. 2.6 – Системы с топологиями линейка (а), кольцо (б) и звезда (в)

Идеальной топологией по быстродействию и соответствию алгоритмам задач следует считать полносвязную топологию, при которой каждый процессорный узел имеет прямую связь с любым другим процессорным узлом системы (рис. 2.7 а). Для такой топологии требуется реализовать N (N −1)/ 2 связей. Это очень большие затраты оборудования, поэтому на

практике такие системы не строят. Наиболее распространенными топологиями является двумерная решетка (рис. 2.7 б), двумерный тор (рис. 2.7 в). На основе топологии двумерная решетка построен компьютер Intel Paragon c процессорами i860, а для топологий двумерного и трехмерного торов фирма Dolphin Interconnect Solutions выпускает специальное оборудование, называемое SCI (Scalable Coherent Interface). Интерфейс SCI позволяет строить параллельные вычислительные системы на обычных компьютерах. Этот интерфейс мы будем рассматривать подробнее, поскольку по нему принят стандарт ANSI/IEEE Std 1596-1992 и его развивают многие фирмы, в том числе HP, Sun, IBM.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

б |

|

в |

a |

Рис. 2.7 – Системы с топологиями: а - полносвязная, б – решетка, в - тор

На рис. 2.8 приведена схема соединений процессоров в компьютере BBN Butterfly. Максимальное число процессоров в этом компьютере может достигать 256.

Высокопроизводительные вычислительные системы и параллельное программирование. Кудерметов Р.К.

4

Рис.2.8 – Система коммутации процессоров компьютера BBN Butterfly

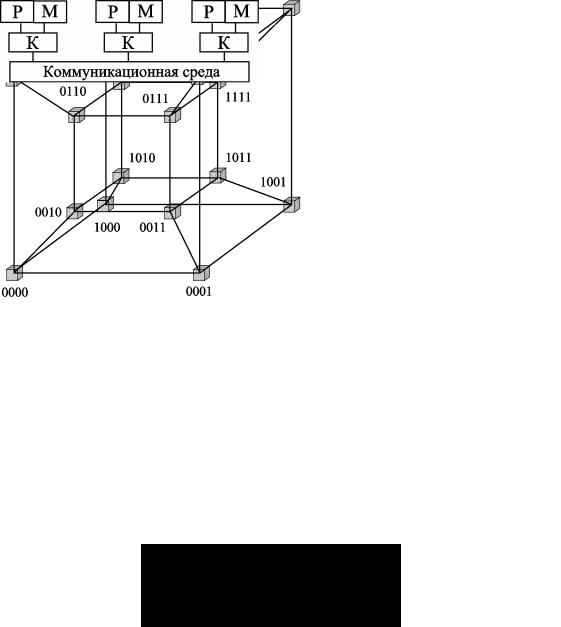

Интересной топологией коммуникационной среды являются n -мерные кубы или гиперкубы. В системах гиперкуб каждый процессор имеет соединения с n ближайшими соседями, и, таким образом, число процессоров, которое может объединять такая среда равно N =log2 n . Максимальное расстояние между узлами n -мерного куба равно n . На рис. 2.9

приведены схемы 3- и 4-х мерных гиперкубов. Особенностью таких топологий является то, что для выбора направления обмена, необходимо изменить лишь один разряд бинарного обозначения узла. Такая нумерация называется схемой кода Грея и очень для вычисления направления обмена с помощью параметрических функций, как было реализовано в языке Parallaxis для параллельной системы MASPAR [4]. К наиболее известным компьютерам с топологией гиперкуб можно отнести Cosmic Cube, созданный в 1983 г. на процессорах Intel 8086, iPSC – на процессорах Intel 80286, nCube/ten фирмы NCUBE Corporation, состоящий из 1024 узлов.

С точки зрения взаимодействия процессоров с памятью мы выделили два больших класса архитектур – системы с разделяемой памятью и системы с распределенной памятью. Каждая из этих архитектур, как мы отметили, имеет свои преимущества и недостатки. При программировании удобно иметь общее адресное пространство и не задумываться, где расположены данные. С этой целью была разработана архитектура многопроцессорных систем с единым адресным пространством, которая носит название Non Uniform Memory Access (NUMA).

Основная идея этой архитектуры в том, что процессоры осуществляют доступ к памяти через специальный контроллер. Если запрашиваемые данные расположены в локальной памяти, т.е. памяти, принадлежащей данному узлу, то обращение выполняется к локальной

Высокопроизводительные вычислительные системы и параллельное программирование. Кудерметов Р.К.

5

памяти, если данные находятся в локальной памяти другого узла, то контроллер памяти делает запрос. Схема архитектуры NUMA показана на рис. 2.10. Конечно, время доступа к локальной памяти своего узла значительно меньше времени доступа к локальной памяти удаленного узла. Однако существуют различные алгоритмы оптимизации размещения данных, позволяющие сократить общее время обращения к памяти. Например, в системе BBN Butterfly, которая относится с классу NUMA-компьютеров, время обращения к локальной памяти 2 мкс, а к удаленной - 6 мкс.

|

|

|

|

|

|

|

|

|

a |

|

б |

Рис.2.9 – Топологии типа гиперкуб: а - 3-куб, б - 4-куб

Но с развитием архитектуры NUMA возникла неожиданная проблема, связанная с использованием кэш-памяти. Если для обычного компьютера кэш-память значительно ускоряет обработку данных и в настоящее время кэш является обязательным компонентом компьютеров, то для NUMA-архитектуры кэш мешает организации единого адресного пространства. Действительно, если измененные данные в одном из узлов параллельной системы еще находятся в его кэш-памяти, то для другого узла они недоступны, пока из кэша эти данные не будут перенесены в основную память узла. Отметим, что такая проблема существует и для компьютеров с разделяемой памятью SMP. Проблему, связанную с необходимостью согласования кэш-памятей процессорных узлов называют проблемой кэш-когерентности.

Рис.2.10 – Архитектура NUMA

В связи с указанной проблемой разработаны различные аппаратные и алгоритмические способы обеспечения кэш-когерентности. Например, алгоритмы MESI и DASH, аппаратура SCI, Memory Channel. Архитектуры, поддерживающие кэш-когерентность получили назва-

ние ccNUMA (cache coherent NUMA).

Высокопроизводительные вычислительные системы и параллельное программирование. Кудерметов Р.К.