- •Переключатели показаны в режиме выборки

- •Сравнение разрешающей способности

- •И времени преобразования типовых ацп

- •Последовательного приближения

- •С однополярным источником питания

- •Конвейерного ацп

- •Показана работа с задержкой на 2 тактовых цикла

- •Подключение входа с коммутируемым конденсатором

- •Cигма-дельта ацп

- •Sigma-delta ацп первого порядка

- •Резюме по sigma-delta ацп

Резюме по sigma-delta ацп

Изначально превосходная линейность

Избыточная дискретизация снижает требования к аналоговому антиалайзинговому фильтру

Идеальны для микросхем со смешанными сигналами, не требуют подгонки параметров

Не требуют устройств выборки-хранения

Дополнительные возможности: встроенные усилители с программируемым усилением, аналоговые фильтры, автокалибровка

Встроенные программируемые цифровые фильтры (AD7725: ФНЧ, ФВЧ, полосовой, режекторный)

В настоящее время ограничения по частоте дискретизации позволяют использовать данные АЦП для измерений, в голосовых и звуковых приложениях, но технология полосовых сигма-дельта АЦП может изменить ситуацию

Скорость переключения аналогового мультиплексора ограничена временем установления внутреннего фильтра. Предполагается использование одного сигма-дельта АЦП на один канал.

Рис. 3.21

Параллельные (Flash) АЦП

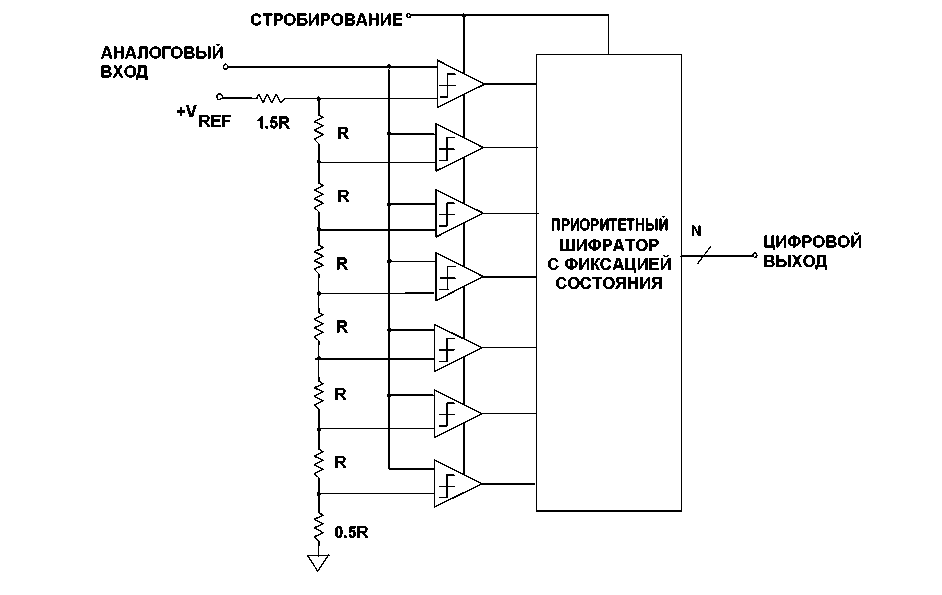

Параллельные АЦП (Flash АЦП) являются самым быстрым типом АЦП, использующим большое количество компараторов, работающих параллельно. N-разрядный параллельный АЦП состоит из 2N резисторов и 2N–1 компараторов, размещенных, как это показано на рис.3.22. На каждый компаратор подается опорное напряжение, значение которого для соседних точек отличается на величину, соответствующую одному младшему значащему разряду (LSB) (более старшие разряды — в верхних по схеме элементах). При фиксированном входном напряжении все компараторы, размещенные на схеме ниже некоторой точки, имеют входное напряжение выше опорного напряжения. На их логическом выходе присутствует "1". У всех же компараторов выше этой точки опорное напряжение больше входного, и их логический выход установлен в "0". Поэтому 2N–1 выходов компаратора ведут себя аналогично ртутному термометру, и выходной код такого АЦП иногда называют «кодом термометра». В действительности, было бы непрактично выводить 2N–1 линий данных наружу, поэтому они преобразуются шифратором в N-разрядный двоичный код.

ПАРАЛЛЕЛЬНЫЙ

(FLASH)

АЦП

Рис. 3.22

Входной сигнал подается на все компараторы сразу, поэтому "выход термометра" имеет задержку по отношению к входному сигналу, равную задержке только одного компаратора и N-разрядного кодера. Это соответствует задержке нескольких логических элементов, так что процесс преобразования осуществляется очень быстро. Но такая архитектура предполагает использование большого числа резисторов и компараторов, имеет ограничение по максимальной разрешающей способности и, чтобы обеспечить высокое быстродействие, каждый компаратор должен иметь довольно высокий уровень потребления энергии. Следовательно, к проблемам параллельных АЦП относятся ограниченная разрешающая способность, высокий уровень рассеивания энергии вследствие большого количества высокоскоростных компараторов (особенно на частотах дискретизации больших, чем 50 MSPS) и относительно большие размеры кристалла (и потому — высокая стоимость). Кроме того, для питания быстрых компараторов необходимым током смещения, цепочка опорных резисторов должна иметь низкое сопротивление, чтобы этот источник давал весьма большие токи (> 10 мА).

На практике реализуются преобразователи до 10-разрядов, но обычно параллельные АЦП имеют разрешающую способность, соответствующую 8-разрядам. Их максимальная частота дискретизации может достигать 1 ГГц при ширине полосы пропускания по уровню полной мощности более 300 МГц.

Как упоминалось ранее, полоса пропускания по уровню полной мощности не обязательно равна полосе, соответствующей полной разрешающей способности. Идеальный компаратор параллельного преобразователя имеет хорошие характеристики и по постоянному, и по переменному току. Поскольку синхронизирующий строб подается на все компараторы одновременно, параллельный преобразователь автоматически реализует схему выборки-хранения на своем входе. На практике существуют различия в задержках компараторов и другие рассогласования по переменному току, которые вызывают

уменьшение эффективного числа разрядов (ENOB) на высоких входных частотах. Это происходит потому, что скорость нарастания сигналов непосредственно на входах сопоставима со временем преобразования компаратора.

Вход параллельного АЦП непосредственно подключается к большому количеству компараторов. Каждый компаратор имеет изменяющуюся в зависимости от напряжения емкость перехода, и наличие этой емкости, зависящей от сигнала, приводит в большинстве параллельных АЦП к уменьшению эффективного числа разрядов (ENOB) и к большим искажениям на высоких входных частотах.

Добавление одного разряда к общей разрешающей способности параллельного преобразователя требует удвоения количества компараторов! Это ограничивает практическую разрешающую способность высокоскоростных параллельных преобразователей до 8 разрядов, так как при более высоких разрешающих способностях слишком велико выделение тепла.

В 10-разрядном АЦП AD9410 с быстродействием 200 MSPS для минимизации числа предварительных усилителей в компараторах преобразователя, а также для уменьшения мощности (1,8 Вт), используется метод, называемый интерполяцией. Метод иллюстрируется на рис.3.23.

ИНТЕРПОЛИРУЮЩИЙ FLASH АЦП УМЕНЬШАЕТ КОЛИЧЕСТВО ПРЕДВАРИТЕЛЬНЫХ УСИЛИТЕЛЕЙ ВДВОЕ

Рис. 3.23

Предварительные усилители (обозначены "A1", "A2" и т.д.) представляют собой каскады с низким коэффициентом усиления gm, ширина полосы пропускания которых пропорциональна обратным токам дифференциальных пар. Рассмотрим случай положительного пилообразного входного сигнала, который первоначально меньше

опорного напряжения V1 усилителя А1. По мере того, как значение входного сигнала приближается к V1, значение дифференциального выхода А1 приближается к 0 (т.е. A = A) в точке переключения компаратора. Сигнал с выхода A1 подается на дифференциальный вход триггера 1. Пока входные сигналы остаются положительными, выход А также сохраняется положительным, а выход B становится отрицательным. Получаемая в результате интерполяции точка переключения соответствует A = B. Пока входной сигнал остается положительным, третья точка переключения определяется условием B = B. Эта новая архитектура уменьшает входную емкость АЦП и, таким образом, минимизирует ее изменение под действием входного сигнала и связанные с этим искажения. УВХ на входе модели AD9410 улучшает ее линейность по переменному току.

Конвейерные (Subranging, Pipelined) АЦП

Хотя целесообразность построения параллельных АЦП с высоким разрешением (большим, чем 10-разрядов) вызывает сомнения, такие АЦП часто используются в качестве подсистем конвейерных (subranging) АЦП (иногда называемых полупараллельными (half-flash)АЦП), которые обладают значительно более высокой разрешающей способностью (до 16-разрядов).

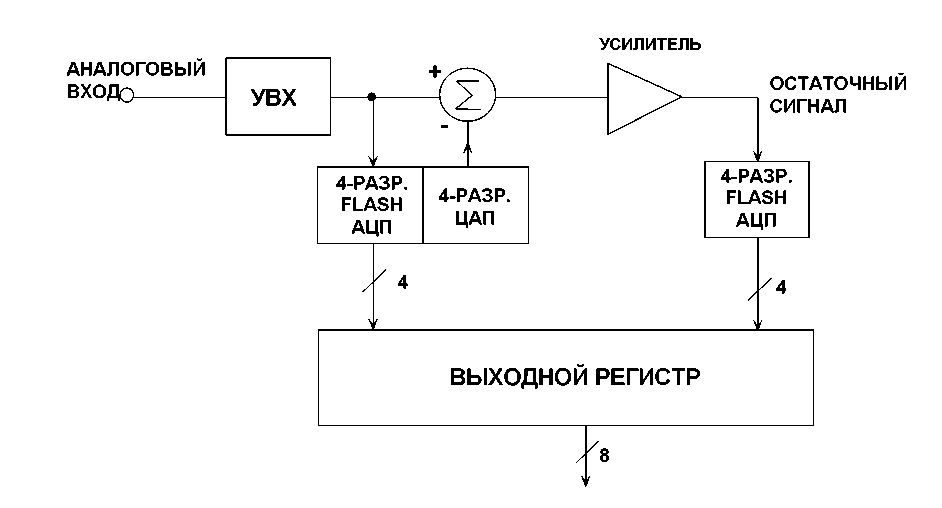

Блок-схема 8-разрядного конвейерного АЦП на основе двух параллельных 4-разрядных АЦП показана на рис.3.24. Учитывая широкую распространенность 8-разрядных параллельных преобразователей с высокими частотами дискретизации, пример такого преобразователя мы используем для иллюстрации концепции. Процесс преобразования осуществляется в два этапа. Первые четыре старших разряда (MSB) оцифровываются первым параллельным АЦП (обладающим точностью выше 8 разрядов), и двоичный выходной 4-разрядный код подается на 4-разрядный ЦАП (также обладающий точностью выше 8 разрядов). Выходной сигнал с ЦАП вычитается из сохраненного аналогового входного сигнала, и результат вычитания (остаток) усиливается и подается на второй параллельный АЦП. Затем выходные сигналы двух 4-разрядных параллельных преобразователей объединяются в один 8-разрядный выходной код. Если динамический диапазон остаточного сигнала не точно заполняет динамический диапазон второго параллельного преобразователя, возникает нелинейность и, возможно, потеря кода.

8-РАЗРЯДНЫЙ

КОНВЕЙЕРНЫЙ

АЦП

Рис. 3.24

Современные конвейерные АЦП используют методы, называемые цифровой коррекцией, для устранения проблем, связанных с архитектурой, представленной на рис.3.24. Упрощенная блок-схема 12-разрядного конвейерного АЦП с цифровой коррекцией (DCS) представлена на рис.3.25. Представленная архитектура подобна той, что используется в 12-разрядном АЦП AD6640 с быстродействием 65MSPS. Обратите внимание, что 6-разрядный и 7-разрядный АЦП используются для получения выходного кода в 12 разрядов. Данные АЦП не являются параллельными АЦП, но используют архитектуру усилителей модуля (magnitude-amplifier, MagAmp™), которая вскоре будет описана.

Если в преобразовании первой ступени нет ошибок, 6-разрядный остаточный сигнал, поданный на 7-разрядный АЦП с суммирующего усилителя, никогда не превысит половину диапазона 7-разрядного АЦП. Избыточный динамический диапазона второго АЦП, совместно с логикой исправления ошибки (обычно это просто полный сумматор), используются для исправления в выходных данных большинства ошибок, свойственных традиционным преобразователям с конвейерной архитектурой без коррекции. Важно обратить внимание, что 6-разрядный ЦАП должен иметь точность, соответствующую не менее чем 12-разрядам, потому что при цифровой коррекции не исправляются ошибки ЦАП. На практике вместо "двоичного" ЦАП часто используются ЦАП типа "термометр" или полностью декодирующие ЦАП, имеющие на каждый уровень один коммутатор тока (63 коммутатора в случае 6-разрядного ЦАП). Этим гарантируется высокая дифференциальная и интегральная линейность и минимизируются переходные процессы, вызванные коммутацией.

12-РАЗРЯДНЫЙ

65MSPS

КОНВЕЙЕРНЫЙ

АЦП

С

ЦИФРОВОЙ

КОРРЕКЦИЕЙ

ОШИБОК

AD6640

Рис. 3.25

УВХ-2 хранит сигнал с выхода УВХ-1 до тех пор, пока выполняется преобразование первой ступени, максимизируя, таким образом, производительность. УВХ-3 ограничивает значение ложного сигнала (glitch) по остаточному сигналу, таким образом, давая возможность осуществить полный цикл преобразования сигнала 7-разрядным АЦП (6- и 7-разрядные АЦП в AD6640 являются поразрядными АЦП, построенные по архитектуре MagAmp, которые требуют большего времени установки, чем параллельные АЦП).

Такой метод многоступенчатого преобразования иногда упоминается как конвейерная обработка. Дополнительные регистры сдвига, подключенные последовательно с цифровыми выходами АЦП первой ступени, гарантируют, что, когда их выводы объединяются в логике коррекции ошибки, они оказываются синхронизированными по времени с последними 7 разрядами второго АЦП. Поэтому конвейерный АЦП имеет специфическое число тактовых циклов ожидания результата, или конвейерную задержку, связанную с выходными данными. Передний фронт тактового импульса дискретизации (отсчета N) используется для синхронизации выходного регистра, но данные, которые появляется по фронту этого тактового импульса, соответствует отсчету N - L, где L — число тактовых циклов конвейерной задержки. В AD6640 конвейерная задержка выполняется в два тактовых цикла.

Схема коррекции ошибки, описанная выше, рассчитана на исправление ошибок, допущенных при первом преобразовании. Ошибки внутреннего усиления АЦП, смещения и линейности корректируются, пока остаточный сигнал находиться в пределах динамического диапазона АЦП второй ступени. Эти ошибки не будут затрагивать линейности передаточной характеристики всего АЦП. Но ошибки конечного преобразования становятся ошибками общей функции передачи всего АЦП. Ошибки линейности или усиления ЦАП и усилителя остаточного сигнала не корректируются и проявятся как нелинейность или немонотонность в общей функции передачи всего АЦП.

Мы рассмотрели пока только двухступенчатые конвейерные АЦП, поскольку они являются самыми простыми для анализа. Но нет причины останавливаться на двух ступенях. Трех- и четырехступенчатые конвейерные АЦП являются весьма обычной продукцией и могут быть реализованы самыми разными способами, как правило — с цифровой коррекцией ошибок.

Упрощенная блок-схема 12-разрядного CMOS АЦП AD9220 с быстродействием 10MSPS, однополярным питанием и потребляемой мощностью 250 мВт представлена на рис.3.26. АЦП AD9221 (1,25 MSPS, 60 мВт) и AD9223 (3MSPS, 100 мВт) имеют идентичную архитектуру, но работают с более низким энергопотреблением и на более низких частотах дискретизации. Это четырехступенчатая конвейерная архитектура с дополнительным разрядом, использующимся для коррекции ошибки на второй, третьей и четвертой ступенях. Благодаря конвейерной архитектуре, эти АЦП имеют три тактовых цикла конвейерной задержки (см. рис.3.27).

Рис. 3.26

12-РАЗРЯДНЫЕ КОНВЕЙЕРНЫЕ CMOS АЦП AD9220/9221/9223

КОНВЕЙЕРНАЯ ЗАДЕРЖКА АЦП AD9220/9221/9223

Рис. 3.27 Каскадные АЦП (BIT-PER-STAGE, последовательные)

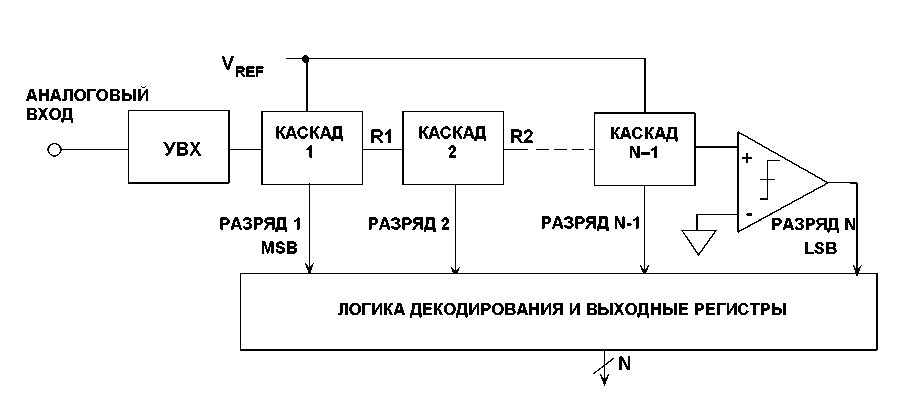

Для выполнения аналого-цифрового преобразования существуют различные архитектуры, использующие принципы последовательного преобразования. В действительности, конвейерный АЦП с одним разрядом на ступень и без коррекции ошибок может рассматриваться как АЦП последовательного счета. На рис.3.28 представлена общая концепция. УВХ хранит значение входного сигнала в течение цикла преобразования. Существует N ступеней, каждая из которых имеет одноразрядный цифровой выход и выход остаточного сигнала. Остаточный сигнал каждой ступени является входным сигналом для следующей ступени. Как показано на рисунке, последний разряд является просто выходным сигналом компаратора.

ПОСЛЕДОВАТЕЛЬНЫЕ АЦП (BIT-PER-STAGE)

Рис. 3.28

ОДИН

КАСКАД

ПОСЛЕДОВАТЕЛЬНОГО

АЦП

Рис. 3.29

На рис.3.29 показан каскад для выполнения одного однобитового преобразования. Каскад состоит из усилителя с коэффициентом усиления 2, компаратора и одноразрядного ЦАП. Предположим, что данный каскад являет собой первую ступень АЦП. Старший значащий разряд (MSB) – это разряд полярности входного сигнала, определяемой компаратором, который также управляет одноразрядным ЦАП. Выходной сигнал одноразрядного ЦАП суммируется с сигналом на выходе усилителя, который имеет коэффициент усиления 2. Результирующий остаточный сигнал подается на следующую ступень. Для лучшего понимания работы схемы на графике показан остаточный сигнал для случая входного линейно нарастающего пилообразного напряжения, размах которого соответствует полному диапазону АЦП от –VR до +VR. Обратите внимание, что полярность остаточного сигнала определяет значение выхода двоичного разряда следующей ступени.

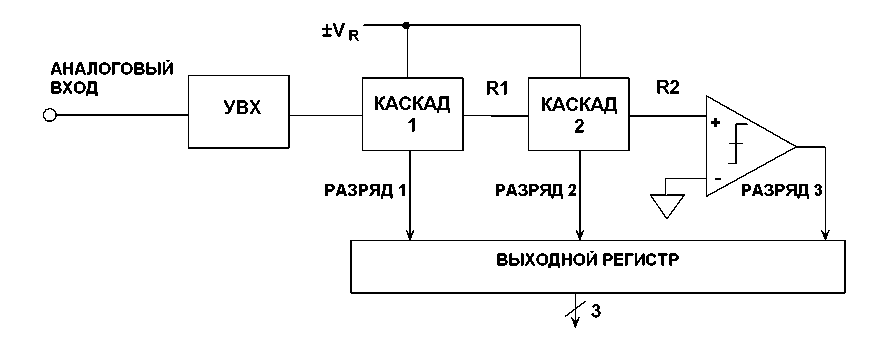

Упрощенный 3-разрядный последовательный двоичный АЦП представлен на рис.3.30 Графики остаточных сигналов, соответствующие выходам различных ступеней, представлены на рис.3.31. Как и в предыдущем случае, рассматривается вариант входного линейного пилообразного напряжения, размах которого соответствует диапазону от –VR до +VR. Каждый остаточный выходной сигнал имеет разрывы, которые соответствуют точкам смены состояния компараторов и переключения ЦАП. Основной проблемой такой архитектуры является наличие разрывов (скачкообразных изменений) формы выходных остаточных сигналов различных ступеней. Необходимо предусмотреть адекватное время установки для окончания соответствующих переходных процессов во всех промежуточных ступенях и на входе компаратора последней ступени. Поэтому перспективы использования этой архитектуры для работы на высоких частотах дискретизации весьма неутешительны.

3-РАЗРЯДНЫЙ ПОСЛЕДОВАТЕЛЬНЫЙ АЦП С ДВОИЧНЫМ ВЫХОДОМ

ФОРМА ВХОДНОГО И ОСТАТОЧНОГО СИГНАЛОВ 3-РАЗРЯДНОГО ПОСЛЕДОВАТЕЛЬНОГО АЦП

Рис. 3.31

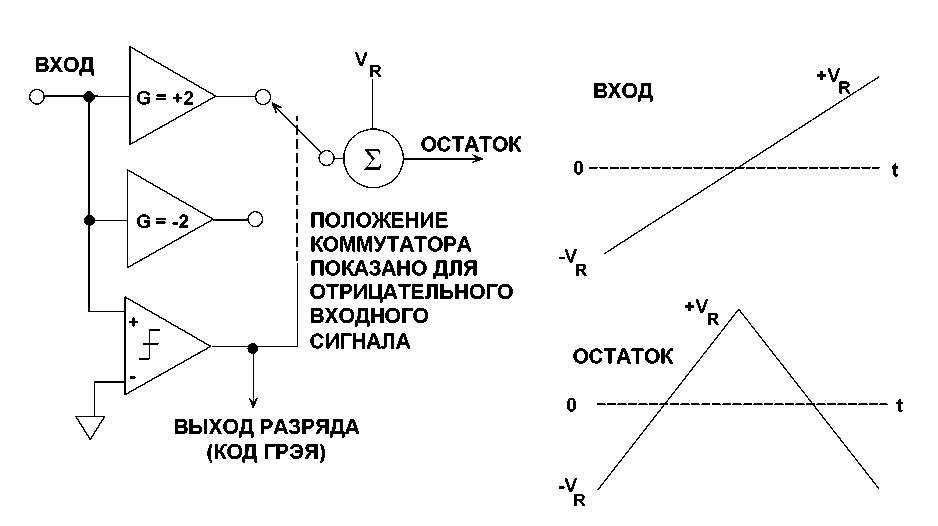

Намного более совершенная архитектура АЦП последовательного счета, основанная на усилителях абсолютной величины (усилители модуля (magnitude amplifiers) или просто MagAmps™), была разработана Ф. Д. Вальдхауэром (F.D.Waldhauer), Приложение 21. Эта схема часто упоминается, как последовательная схема Грея (serial-Gray) (так как выходное кодирование осуществляется кодом Грея) или поворачивающий (folding) преобразователь (Приложения 22, 23, 24). Функциональная схема основной ступени вместе с ее передаточной функцией представлены на рис.3.32. Принимается, что входной сигнал ступени является линейным пилообразным напряжением, размах которого соответствует диапазону от –VR до +VR. Компаратор выявляет полярность входного сигнала и

формирует выходной разряд для данной ступени в виде кода Грея. Компаратор также определяет, должно ли общее усиление ступени быть равным +2 или -2. Опорное напряжение VR суммируется с выходом коммутатора для генерации остаточного сигнала, который подается на следующую ступень. Полярность остаточного сигнала определяет выходной разряд следующей ступени вновь в виде кода Грея. Передаточная функция поворачивающей (folding) ступени также представлена на рис.3.32.

ЭКВИВАЛЕНТНАЯ СХЕМА КАСКАДА MAGAMP

Рис. 3.32

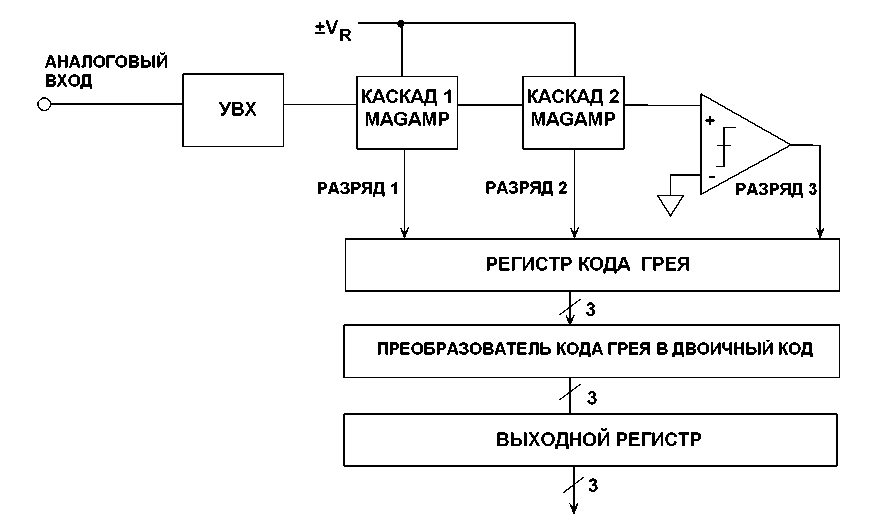

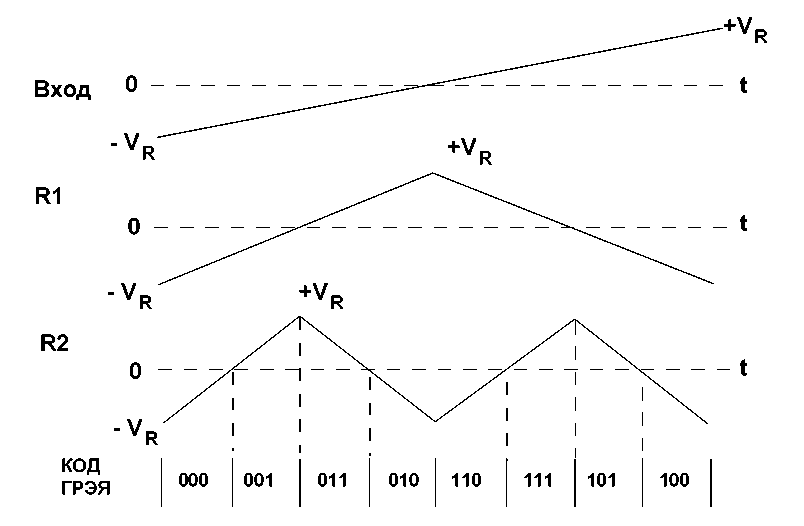

3-разрядный поворачивающий (folding) MagAmp АЦП представлен на рис.3.33, а диаграммы соответствующих остаточных сигналов изображены на рис.3.34. Как и в случае двоичного АЦП с пилообразной формой остаточных сигналов, значение кода Грея для следующей ступени определяется полярностью выходного остаточного сигнала предыдущей ступени. Полярность входного сигнала первой ступени определяет старший значащий разряд кода Грея; полярность выхода R1 — второй разряд кода Грея, полярность выхода R2 — третий разряд кода Грея. Обратите внимание, что, в отличие от двоичного импульсного АЦП, ни одна из ступеней данной архитектуры не дает перепада значения остаточного сигнала. Это делает данную архитектуру перспективной для работы на высоких частотах дискретизации.

Основой функционирования этой архитектуры на высоких скоростях является применение поворачивающей (folding) ступени. Ранние применения данной архитектуры (см. Приложения 22, 23, 24) для генерации поворачивающей функции передачи использовали дискретные операционные усилители с диодами в контуре обратной связи. Современные интегральные схемы реализуют требуемую функцию передачи, управляя коэффициентом усиления по току при разомкнутой обратной связи, что может быть реализовано с более высоким быстродействием. Полностью дифференциальные ступени (включая УВХ) также обеспечивают высокую скорость, более низкие искажения и дают поворачивающие (folding) ступени, обладающие 8-разрядной точностью, не требуя лазерной подстройки тонкопленочного резистора (см. Приложения 25, 26, 27).

БЛОК-СХЕМА 3-РАЗРЯДНОГО АЦП MagAmp™

Рис. 3.33

ФОРМА ВХОДНОГО И ОСТАТОЧНЫХ СИГНАЛОВ 3-РАЗРЯДНОГО АЦП MAGAMP

Рис. 3.34

Использование архитектура MagAmp может быть расширено до скоростей дискретизации, в которых ранее доминировали параллельные (flash) преобразователи. Двойной 8-

разрядный АЦП AD9288-100 с быстродействием 100 MSPS представлен на рис.3.35. Первые пять разрядов (код Грея) получены из пяти дифференциальных MagAmp ступеней. Дифференциальный остаточный выход пятой ступени MagAmp управляет 3-разрядным параллельным преобразователем вместо одиночного компаратора. Выходной код Грея пяти ступеней, построенных по архитектуре MagAmps, и выходной двоичный код 3-разрядного параллельного АЦП хранятся в регистре, затем все данные преобразуются в двоичный код и помещаются в выходной регистр.

ФУНКЦИОНАЛЬНАЯ СХЕМА ДВОЙНОГО 8-РАЗРЯДНОГО

Рис. 3.35

100 MSPS АЦП AD9288-100