- •МАТЕМАТИЧЕСКАЯ ЛОГИКА

- •Булевы функции

- •Три важнейшие интерпретации булевых функций

- •Что такое переключательная схема?

- •Основные задачи теории релейно- контактных схем

- •Синтез и анализ схемы

- •Функции проводимости F некоторых

- •Функции проводимости F некоторых

- •Примеры

- •Примеры

- •Примеры

- •Пример. Упростить переключательные схемы

- •Логические схемы

- •Логические элементы

- •Логические элементы

- •Логические элементы компьютера

- •Логические элементы компьютера

- •Составление схем

- •Пример. Построим два варианта логических схем

- •Задача Судейская коллегия, состоящая из 3 человек, выносит решение большинством голосов. Построить логическую

- •Спомощью логических элементов НЕ, И, ИЛИ можно реализовать (собрать как из конструктора) типовые

- •Построение логических схем по заданной таблице истинности

- •Пример. По заданной таблице истинности записать логическую функцию, упростить ее и построить логическую

- •Схема, построенная по неупрощенной логической функции

- •3. Составить схему, работа которой задана таблицей истинности:

- •ПОСТРОЕНИЕ ТАБЛИЦЫ ИСТИННОСТИ И ЛОГИЧЕСКОЙ ФУНКЦИИ ПО ЗАДАННОЙ ЛОГИЧЕСКОЙ СХЕМЕ

- •Триггер (англ. trigger – защёлка)

- •Триггер

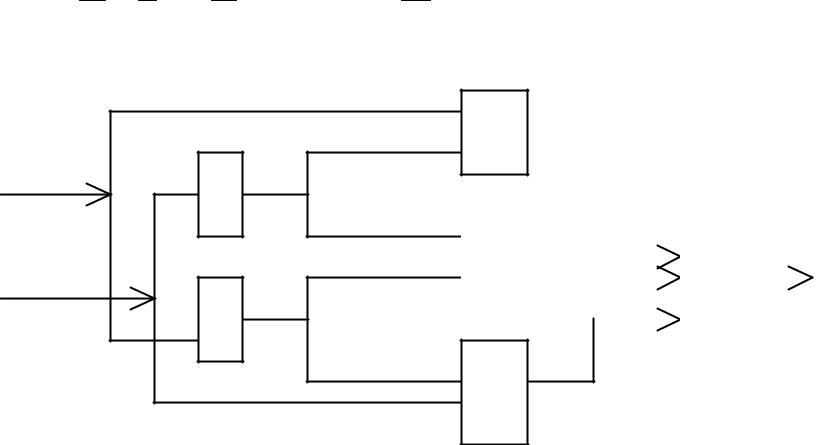

- •Регистр – устройство, состоящее из последовательности триггеров. Предназначен для хранения многоразрядного двоичного числового

- •Полусумматор – реализует суммирование одноразрядных двоичных чисел без учета переноса из младшего разряда.

- •Полусумматор

- •Схема полусумматора двоичных чисел

- •Сумматор для двух одноразрядных чисел

- •Сумматор

- •Многоразрядный сумматор

- •Спасибо за внимание!!!

- •Построение булева выражения по логической схеме

- •Проверьте равносильность следующий переключательных схем

- •Пример. Упростить переключательные схемы

- •4. Упростим переключательные схемы

- •Пример. Упростить переключательные схемы

- •Найти F проводимости следующих переключательных схем

- •ЗАДАНИЕ

- •Задачи.

Спомощью логических элементов НЕ, И, ИЛИ можно реализовать (собрать как из конструктора) типовые функциональные узлы (блоки) ЭВМ:

триггерысумматорышифраторырегистрысчетчикидешифраторы

Чтобы понять, как работает интересующее нас устройство, необходимо понять логику его работы, т.е. найти соответствие между входными и выходными сигналами, для этого:

составить таблицу истинности

по таблице записать логическую функцию

построить логическую схему

Построение логических схем по заданной таблице истинности

I. Выписывается таблица истинности функции.

II.По данной таблице определяется логическая функция (формула) с помощью метода совершенная

дизъюнктивная нормальная форма (СДНФ)

III. По упрощенной логической функции строится логическая схема.

Пример. По заданной таблице истинности записать логическую функцию, упростить ее и построить логическую схему.

x  y

y  F 0

F 0  0

0  1 0

1 0  1

1  1 1

1 1  0

0  1 1 1 0

1 1 1 0

x |

|

y |

1. Запишем конъюнкцию для |

y |

каждой строки, где значение |

||

x |

|

функции = 1. Переменные, |

|

x |

y |

|

значения которых равны 0, |

|

|

|

запишем с отрицанием. |

2. Объединив полученные конъюнкции дизъюнкцией, получим следующую логическую функцию.

F(X Y) (X Y) (X Y)

3.Упростим: F (X Y) (X Y) (X Y) X (X Y)

4. По полученной |

|

|

|

|

|

|

НЕ |

|

|

|

|

|

|

X |

|

|

|

|

|

|

|

|

|

F |

|||

функции |

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

1 |

||||

|

|

|

|

|

|

|

|

|

|

|

|||

построим |

|

|

|

|

|

|

& |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|||

логическую |

|

|

НЕ |

|

|

|

|

|

|

|

|

||

Y |

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|||||

схему: |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Схема, построенная по неупрощенной логической функции

F (X Y) (X Y) (X Y)

x |

y |

&

|

|

|

|

|

|

|

& |

|

|

|

1 |

|

F |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

&

3. Составить схему, работа которой задана таблицей истинности:

A |

B |

C |

F(A,B,C) |

а) Составим логическую формулу схемы: |

|||||

F (А В С) (А В |

С ) |

(А В С) |

|||||||

0 |

0 |

0 |

0 |

||||||

0 |

0 |

1 |

0 |

б) Упростим полученную формулу: |

|

|

|||

0 |

1 |

0 |

0 |

F (А В С) (А В С ) (А В С) |

|||||

0 |

1 |

1 |

0 |

(А В С) (А В) (С С) (А В С) (А В) |

|||||

1 |

0 |

0 |

0 |

||||||

А (В (В С) |

А (В С) |

||||||||

1 |

0 |

1 |

1 |

||||||

1 |

1 |

0 |

1 |

в) по упрощенной |

A B C |

А (В С) |

|||

1 |

1 |

1 |

1 |

|

|

|

|

||

(минимизированной) |

0 |

0 |

0 |

0 |

|||||

|

|

|

|

функции составим |

0 |

0 |

1 |

0 |

|

|

|

|

|

логическую схему: |

|||||

|

|

|

|

0 |

1 |

0 |

0 |

||

A |

|

|

& |

|

|||||

|

|

|

0 |

1 |

1 |

0 |

|||

B |

|

|

|

F Правильность |

1 |

0 |

0 |

0 |

|

|

|

1 |

|

полученной формулы |

1 |

0 |

1 |

1 |

|

C |

|

|

можно проверить |

||||||

|

|

1 |

1 |

0 |

1 |

||||

|

|

|

сопоставлением |

||||||

|

|

|

|

||||||

|

|

|

|

таблиц истинности по |

1 |

1 |

1 |

1 |

|

|

|

|

|

последним столбцам. |

|

|

|

|

|

ПОСТРОЕНИЕ ТАБЛИЦЫ ИСТИННОСТИ И ЛОГИЧЕСКОЙ ФУНКЦИИ ПО ЗАДАННОЙ ЛОГИЧЕСКОЙ СХЕМЕ

Задание. Запишите логическую функцию, описывающую состояние схемы, составьте таблицу истинности:

1 |

2 |

|

4 |

|||||

x |

|

|

|

|

|

|

|

|

|

|

|

& |

|

|

1 |

|

|

|

|

|

|

|

|

F |

||

y |

|

|

|

|

|

|

|

|

|

|

|

3 |

|

|

|

|

|

|

|

|

|

|

|

|

||

z |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Для записи функции необходимо записать значения на выходе каждого элемента схемы:

1. |

x |

y |

2. |

x |

|

3. |

z |

|

4. |

(x |

y) z Следовательно |

|

|

|

Таблица истинности: |

|||

x y z |

x |

x y |

z |

(x y) z |

||

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

получится функция: F (x y) z

Триггер (англ. trigger – защёлка)

Триггер – это логическая схема, способная хранить 1

бит информации (1 или 0). Строится на 2-х элементах ИЛИ-НЕ или на 2-х элементах И-НЕ.

set, установка

S

1

1

1

1

R

reset, сброс

вспомогательный

выход

|

|

|

|

|

|

|

|

|

|

|

|

Q |

|

|

|

S R Q |

|

||

|

|

|

|

|

Q |

||||

|

|

|

|

|

|

0 |

0 |

Q |

|

|

|

|

|

|

|

Q |

|||

|

обратные связи |

0 |

1 |

0 |

1 |

||||

|

|

|

|

|

|||||

|

|

Q |

|

1 |

0 |

1 |

0 |

||

|

|

||||||||

|

основной |

1 |

1 |

0 |

0 |

||||

|

выход |

|

|

|

|

||||

режим

хранение

сброс

установка 1

запрещен

Триггер

Триггер имеет

два входа:

S (set –установка) и

R (reset – сброс) и

два выхода Q (прямой) и

НЕ Q (инверсный)

Входы |

Состояние |

|

S |

R |

Q |

0 |

0 |

Q |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

Недопустимо |

S(1) |

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

0 Q |

||||||

|

|

|

ИЛИ |

|

|

НЕ |

||||

1 |

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|||

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

|

|

|

0 |

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|||||||

|

|

ИЛИ |

|

НЕ |

|

|

|

||||

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

Q |

|

R |

||||||

|

|

|

||||

|

|

|

|

|

В обычном состоянии на входы триггера подан сигнал «0» и триггер хранит «0». Для записи «1» на вход S (set – установочный) подается сигнал «1». При последовательном рассмотрении прохождения сигнала по схеме видно, что триггер переходит в это состояние и будет устойчиво находиться в нем и после того, как сигнал на входе S исчезнет. Триггер запомнил «1», т.е. с выхода триггера Q можно считывать «1».

Чтобы сбросить информацию и подготовиться к приему новой, на вход R (сброс) подается сигнал «1», после чего триггер возвратится к исходному  «нулевому» состоянию.

«нулевому» состоянию.

Регистр – устройство, состоящее из последовательности триггеров. Предназначен для хранения многоразрядного двоичного числового кода, которым может быть представлять и адрес, и команду и данные

|

Q |

|

|

|

|

|

|

Q |

Q |

|

|

|

|

|

|

Q |

Q |

|

|

|

|

|

|

Q |

Q |

|

|

|

|

|

|

Q |

Q |

|

|

|

|

|

|

|

Q |

Q |

|

|

|

|

|

|

Q |

Q |

|

|

|

|

|

|

Q |

Q |

|

|

|

|

|

|

Q |

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

0 |

|

|

|

|

|

|

|

1 |

|

|

|

|

|

1 |

|

|

|

|

|

0 |

|

|

|

|

|

0 |

|

|

|

|

|

1 |

|

|

|

|

|

|

|

0 |

|

|

|||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

RS |

|

|

|

|

|

R S |

|

|

|

|

|

R S |

|

|

|

|

|

RS |

|

|

|

|

|

|

R S |

|

|

|

|

|

RS |

|

|

|

|

|

R S |

|

|

|

|

|

R |

|||||||||||||||||||||||||||||||

S |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||||||||

1 |

|

|

0 |

|

|

|

|

0 0 |

|

|

|

|

1 0 |

|

|

|

|

1 0 |

|

|

|

|

0 0 |

|

|

|

|

0 0 |

|

|

|

|

1 0 |

|

|

|

|

0 0 |

|

|||||||||||||||||||||||||||||||||||||||||||

Число триггеров в регистре называется разрядностью компьютера, которая может быть равна 8, 16, 32, 64.

Полусумматор – реализует суммирование одноразрядных двоичных чисел без учета переноса из младшего разряда.

Слагаемые |

Перенос |

|

А |

В |

P |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

А  B 0

B 0  0 0

0 0  1 1

1 1  0 1 1

0 1 1

Сумма |

P A & B |

|

|

|

|

||||

S |

Значения S будут |

|

|

|

|

||||

0 |

соответствовать сумме, если |

||||||||

результат логического сложения |

|||||||||

1 |

|||||||||

умножить на инверсный перенос. |

|||||||||

1 |

Тогда |

S (A B) & |

|

|

|

|

|||

0 |

|

(A & B) |

|

|

|||||

AvB |

A&B |

|

|

(A B) & |

|

|

|||

|

A & B |

(A & B) |

|||||||

0 |

0 |

1 |

|

0 |

|

|

|

||

1 |

0 |

1 |

|

1 |

|

|

|

||

1 |

0 |

1 |

|

1 |

|

|

|

||

1 |

1 |

0 |

|

0 |

|

|

|

||