dsd1-10 / dsd-04=Ermak / DSD4 / DSD4_l4_new

.docЛекция 4.

-

Состав и характеристики библиотек стандартных логических ячеек, блоков ввода-вывода. Синтезаторы блоков ЗУ.

Состав типовой библиотеки стандартных логических ячеек.

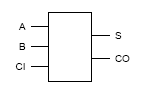

ADDF, ADDFH, ADDH – логические двоичные сумматоры с цепями переноса

AND2, AND3, AND4 – двух, трех и четырех входовые элементы И

AOI21, AOI211, AOI22, AOI221, AOI222, AOI2BB1, AOI2BB2, AOI31, AOI32, AOI33 – элементы на базе И и ИЛИ-НЕ

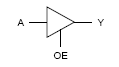

BUF, CLKBUF, CLKINV – буферы сигналов, тактовой частоты и инверторы

![]()

DFF, DFFHQ, DFFN, DFFNR, DFFNS, DFFNSR, DFFR, DFFRHQ, DFFS, DFFSHQ, DFFSR, DFFSRHQ, DFFTR – D триггеры

DLY1, DLY2, DLY3, DLY4 (0.5, 1, 3, 7 ns) – элементы задержки

![]()

EDFF, EDFFTR – D триггеры с сигналом разрешения

HOLD – элементы удержания линии в последнем состоянии перед отключением от нее всех источников сигналов (переходов в Z - состояния)

INV - инвертор

![]()

JKFF, JKFFR, JKFFS, JKFFSR – JK триггеры

MX2, MX4, MXI2, MXI4 - мультиплексоры

NAND2, NAND2B, NAND3, NAND3B, NAND4, NAND4B, NAND4BB – И-НЕ

![]()

NOR2, NOR2B, NOR3, NOR3B, NOR4, NOR4B, NOR4BB – ИЛИ-НЕ

OAI21, OAI211, OAI22, OAI221, OAI222, OAI2BB1, OAI2BB2, OAI31, OAI32, OAI33 – элементы на базе ИЛИ-И

OR2, OR3, OR4 – двух, трех и четырех входовые элементы ИЛИ

RSLAT, RSLATN – RS триггеры

SDFF, SDFFHQ, SDFFN, SDFFNR, SDFFNS, SDFFNSR, SDFFR, SDFFRHQ, SDFFS, SDFFSHQ, SDFFSR, SDFFSRHQ, SDFFTR, SEDFF, SEDFFHQ, SEDFFTR – триггеры для реализации схем с сканирующем путем

TBUF, TBUFI – буферы с третьим состоянием

TIEHI, TIELO – элементы задания логической единицы и логического нуля

TLAT, TLATN, TLATNR, TLATNS, TLATNSR, TLATR, TLATS, TLATSR, TTLAT - защелки

XOR2 – исключающее ИЛИ

В документации описывающей характеристики библиотечных элементов включают следующие разделы:

-

Физическая спецификация (Physical specifications)

-

Электрическая спецификация (electrical specifications)

-

Коэффициенты снижения номинальных параметров (derating factors)

-

Расчет задержки элементов (propagation delay calculation)

-

Временные ограничения (timing constraints)

-

Методику расчета потребления (power calculation)

-

Расчет требуемой эффективной ширины шин питания (Power-rail strapping)

Физическая спецификация содержит основные параметры используемого технологического процесса и ограничений на проектирование топологии (шаг сетки).

Электрическая спецификация – описывает допустимые параметры по напряжению питания и температуре

Коэффициенты снижения номинальных параметров – используются для расчета по заданным формулам статических и динамических параметров элементов.

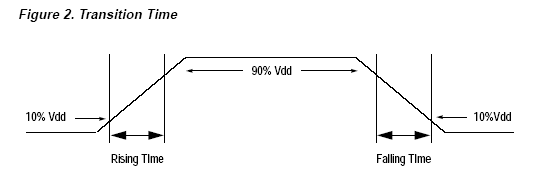

Расчет задержки элементов – методика и задание уровней сигналов по которым осуществляют измерение динамических параметров элементов, таких как:

-

Задержка распространения сигнала

-

Время нарастания и спада сигнлала

-

Требуемое, минимальное время предустановки данных на входе триггера до прихода активного фронта тактовой частоты

-

Требуемое, минимальное время удержания данных на входе триггера после прихода тактовой частоты

-

Требуемое, минимальное время предустановки сигналов сброса и предустановки до прихода активного фронта тактовой частоты

-

Минимальная ширина импульсов

Расчет общей задержки осуществляется по следующей формуле:

Помимо стандартных логических ячеек библиотека содержит специальные элементы:

-

Antenna-Fix Cell – элемент представляющий собой обратно смещенный диод предназначенный для защиты элементов от повреждения статическим разрядом возникающем на длинных проводниках в процессе изготовления.

-

Fill Cells FILL1, FILL2, FILL4, FILL8, FILL16, FILL32, FILL64 – элементы заполнения пустот между элементами в топологии устройства для обеспечения технологичности (непрерывность каналов и шин питания).

-

Low-Power (XL) Cells – ячейки с минимальной нагрузочной способностью.

Минимальная информация о ячейках состоит из (Пример):

1. Имя ячейки (Cell Name) - DFF

2. Описание ячейки (Cell Description) – D триггер работающий по переднему фронту

3. Функциональность (Functions)

4. Графическое представление элемента (Logic Symbol)

5. Размер ячеек (Cell Size)

6. Функциональная схема (Functional Schematic)

7. Потребляемая мощность (AC Power)

8. Задержка переключения (Delay) и нагрузочная способность (Drive Strength)

10. Временные ограничения (Timing Constraints)

11. Емкость выводов (Pin Capacitance)

Расчет средней потребляемой мощности осуществляется по следующей формуле:

![]()

где x – количество входов, Ein – энергия переключения i-го входа (мкВт/МГц), fin – частота переключения i-го входа (МГц), y – количество выходов элемента, Con – емкость внешней нагрузки на i-м выходе (пФ), Vdd = 2.5В, fon – частота переключения i-го выхода (МГц), Eos – энергия связанная с переключением выхода только для последовательных элементов (мкВт/МГц).

Для получения блоков одно- и двух- портового статического ОЗУ, а также блоков ПЗУ используют программные генераторы данных блоков, которые создают все необходимые файлы начиная от документации заканчивая топологическим представлением блока (GDSII, LEF).

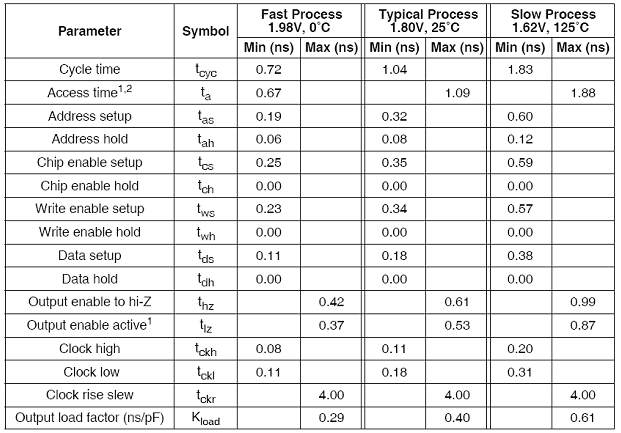

Документация на блоки ОЗУ и ПЗУ содержит разделы аналогичные описанию на стандартные ячейки. Рассмотрим пример блока ОЗУ 64х8.

-

Описание выводов, графическое представление и площадь ОЗУ:

-

Структурная схема синхронного одно- портового ОЗУ

-

Временные диаграммы чтения данных

-

Временные диаграммы записи данных

-

Емкость выводов

-

Временные параметры

-

Потребляемая мощность для различных режимов при частоте 300МГц