- •Contents

- •Preface

- •Related Documents

- •Typographic and Syntax Conventions

- •Introduction to the Virtuoso XL Layout Editor

- •Editing Your Technology File for Virtuoso XL Layout Editor

- •Sample Technology File

- •Virtuoso XL Technology File Requirements

- •Layer Rules

- •Devices

- •Physical Rules

- •Virtuoso XL Rules (lxRules)

- •Compactor Rules

- •Preparing Your Connectivity Source for the Virtuoso XL Layout Editor

- •Placing Design Elements

- •Using Design Variables

- •Netlist Processor Expressions

- •Analog Expression Language Expressions

- •Simulation Design Variables

- •Using One-to-Many Mapping

- •Iterated Instances and Bus Pins

- •Multiplication Factor (mfactor)

- •Series-Connection Factor (sfactor)

- •One-to-Many Assignment with the Update Device Correspondence

- •Using Many-to-Many or Many-to-One Mapping

- •Modifying Many-to-Many or Many-to-One Mapping Between Components

- •Deleting Many-to-Many or Many-to-One Mapping Between Components

- •Using Virtuoso XL Properties

- •Using the lxUseCell Property to Specify Layout Devices to Use

- •Using the lvsIgnore Property to Exclude Schematic Symbols

- •Using the lxlgnoredParams Property to Exclude Device Properties

- •Using the lxRemoveDevice property to Ignore Parasitic Devices

- •Using the lxViewList and lxStopList Properties to Prepare Hierarchical Designs

- •Using the lxCombination Property to Build Complex Devices

- •Preparing Instances and Pins in Your Layout for the Virtuoso XL Layout Editor

- •Preparing Pins for the Virtuoso XL Layout Editor

- •Preparing Pins for Permutability

- •Search Order Variable

- •Syntax

- •Macros

- •Setting the permuteRule Property in the Symbol Master

- •Setting the permuteRule Property in the Device Master

- •Setting the permuteRule Property in the Symbol Instance

- •Setting the permuteRule Property in the Device Instance

- •Setting the permuteRule Property in the Component Description Format

- •Preparing Instances for Hierarchical Connectivity Checking

- •Setting Up Your Desktop

- •Customizing Your Desktop Layout

- •Using Multiple Cellviews

- •Printing to the Command Interpreter Window

- •Changing Display Colors

- •Using Bindkeys

- •Displaying Bindkeys

- •Loading Virtuoso XL Bindkeys

- •Setting Environment Variables

- •Information About Online Forms

- •Layout XL Options Form

- •Introduction to Abutment

- •Abutment Requirements

- •Setting Up Cells for Abutment

- •abutAccessDir

- •abutClass

- •Steps in Auto-Abutment

- •Sample Parameterized Cells Set Up for Abutment

- •Example 1

- •Example 2

- •Creating CMOS Pcells to Use with Abutment

- •autoAbutment Properties

- •The abutMosStretchMat Property

- •abutMosStretchMat Rules for MOS Abutment

- •Example Code Setting MOS Abutment Properties

- •Setting Environment Variables for Abutment

- •Move Together

- •Constraint Assisted

- •Using Device Abutment

- •Generating Your Layout with Virtuoso XL Layout Editor

- •Starting Virtuoso XL from the Schematic

- •Importing a Netlist for a Connectivity Reference

- •Starting Virtuoso XL from the Layout View

- •Connectivity Reference as a Netlist

- •Mapping File Structure

- •Working with Template Files

- •Saving Form Contents

- •Loading Template Files

- •Modifying Templates

- •Loading Template Files

- •Creating Template Files

- •Template File Syntax

- •General Syntax Rules

- •Boundaries Section

- •I/O Pins Section

- •Sample Template

- •Generating a Layout with Components Not Placed (Gen From Source)

- •Moving Components from the Schematic into the Layout (Pick from Schematic)

- •Placing a Group of Schematic Elements Together

- •Placing Individual Components

- •Generating Pins

- •Viewing Unplaced Instances/Pins

- •Viewing in Place

- •Manually Abutting Devices Using Pick from Schematic

- •Cloning Components

- •Cloning

- •Troubleshooting

- •Cloning Using Multiple Cellviews

- •Using Correspondence Points

- •Information About Online Forms

- •Add Correspondence Pairs Form

- •Cloning Form

- •Correspondence Pairs Form

- •Import XL Netlist Form

- •Layout Generation Options Form

- •Open File Form

- •Pick from Schematic Form

- •Remove Correspondence Components Form

- •Set Pin Label Text Style Form

- •Startup Option Form

- •Template File Form

- •Editing Your Layout with Virtuoso XL Layout Editor

- •Identifying Incomplete Nets

- •Moving Objects Manually in the Virtuoso XL Layout Editor

- •Moving Objects Using Move Options

- •Setting the Move Form to Appear Automatically

- •Aligning Objects

- •Post Selecting Devices

- •PreSelecting Devices

- •Swapping Components

- •Permuting Component Pins

- •Permuting Pins Manually

- •Checking Permutation Information

- •Using Device Locking

- •Using Automatic Spacing

- •Using Interactive Device Abutment

- •Setting Component Types

- •About Component Types

- •MOS Transistor Stacking and Folding Parameters

- •Modifying a Component Type

- •Using Transistor Chaining

- •Using Transistor Folding

- •Controlling the Folding Grid

- •Folding Transistors

- •Adding Instances to a Layout

- •Adding Pins to a Layout

- •Assigning Pins to a Net

- •Maintaining Connectivity When Editing a Flattened Pcell

- •Information About Online Forms

- •Assign Nets Form

- •Edit Component Types Form

- •Move Form

- •Set Transistor Folding Form

- •Show Incomplete Nets Form

- •Stretch Form

- •Virtuoso XL Alignment Form

- •Using the Virtuoso Custom Placer

- •Overview

- •Main Features

- •Place Menu Command Summary

- •Other Commands Used with the Virtuoso custom placer

- •Placement Styles

- •Setting Up the Virtuoso XL Layout Editor for Placement

- •Identifying the Placement Translation Rules

- •Setting Cadence Design Framework II Environment Variables

- •Setting Environment Variables for the Virtuoso Custom Router and Placer

- •Setting MOS Chaining and Folding Parameters

- •Abutting Standard Cells

- •Using Auto-Abutment During Placement

- •Placement Constraints

- •Constraint Manager Geometric Constraints

- •Pin Placement Constraints

- •Constraint Limitations

- •Placement Parameters and Component Types

- •MOS Transistor Chaining and Folding Parameters

- •Pin Placement

- •Assigning Pins to an Edge

- •Assigning Pins to a Fixed Position

- •Railing Pins

- •Loading the Template File

- •Assigning Spacing Between Pins

- •Saving Pin Placement to a Template File

- •Partitioning the Design

- •Creating a Partition

- •Loading the Template File

- •Saving Partitions to a Template File

- •Setting Placement Planning

- •Assisted CMOS Placement

- •Choose Component Types Form

- •Running the Virtuoso Custom Placer

- •Prerequisites to Placement

- •Running the Virtuoso Custom Placer: Initial Placement

- •Stopping the Placer

- •Running Load Balancing Service (LBS)

- •Troubleshooting Placement Results

- •Running the Virtuoso Custom Placer: Detailed Placement

- •Showing Congestions

- •Information About Forms

- •Auto Placer Form

- •Partitioning Form

- •Choose Component Types Form

- •Pin Placement Form

- •Load Template File Form

- •Placement Planning Form (Assisted CMOS)

- •Placement Planning Form (Assisted Standard Cell)

- •Placement Planning Form (Assisted Mixed CMOS/Standard-Cell)

- •Preparing Your Design for Routing in the Virtuoso XL Layout Editor

- •Understanding Connectivity

- •Pseudo-Parallel Connections

- •Selecting Layers

- •Changing Layers

- •Connecting Nets

- •Creating Paths

- •Connecting Nets with Path Stitching

- •Connecting Nets with Design Shapes

- •Checking Connectivity with Flight Lines

- •Checking Connectivity with Markers

- •Finding Markers

- •Explaining Markers

- •Deleting Single Markers

- •Deleting All Markers

- •Using the Virtuoso Compactor on a Routed Design

- •Overview

- •Main Features

- •Wire Editing Commands

- •Virtuoso Custom Router to Virtuoso XL Command Mapping

- •Prerequisites

- •Rule Information

- •Net Connectivity Information

- •Routing Area Boundary

- •Enabling Wire Editing

- •Toggling Between Virtuoso XL and Wire Editing Enabled

- •Loading ASCII Rules Files

- •The Wire Editing Environment

- •Status Banner

- •Preview Wires and Routing Aids

- •Mouse Button Behavior

- •Using Environment Variables

- •Routing Paths

- •Routing a Single Path

- •Routing Multiple Paths

- •Preventing and Checking Design Rule Violations

- •Interactive Checking

- •Same Net Checking

- •Checking Regions

- •Checking Route and Pin Violations

- •Routing Options and Styles

- •Matching Path Width and Pin Widths

- •Matching Path Width and Pin Widths for Multiple Paths

- •Gathering Bus Wires

- •Spacing for Gathered Bus Wires

- •Overriding Bus Spacing

- •Rotating the Bus Cursor

- •Cycling the Control Wire

- •Allowing Redundant Wiring

- •Allowing Orthogonal Jogs

- •Route To Cursor

- •Allow Floating Nets

- •Connecting Multiple Component Pins

- •Pushing Routes and Components

- •Routing Shielded Nets

- •Routing Tandem Layer Pairs

- •Using Vias

- •Changing Layers and Adding Vias

- •Using Vias Patterns on Multiple Paths

- •Legal Via Sites

- •Rotating Vias

- •Pseudo Vias

- •Editing Routed Connections

- •Stretching Paths and Vias

- •Splitting and Stretching Paths

- •Copying Routes

- •Using Critic Wire

- •Compacting Paths Using Pull

- •Displaying Reports

- •Displaying Routing Status Reports

- •Displaying Network Reports

- •Displaying Component Reports

- •Displaying Net Reports

- •Creating Rules Reports

- •Search Reports

- •Saving Reports

- •Setting Constraints

- •Using the Virtuoso Constraint Manager

- •Using .do Files

- •About the Forms

- •Add Via Form

- •Check Routes Form

- •Create Path Form

- •Find File Form

- •Layout

- •Reports Form

- •Route Options Form

- •Save As Form

- •Search Form

- •Split Form

- •Via Pattern Pop-up

- •Reports

- •Route Status Report Window

- •Network Report Window

- •Instance Report Window

- •Net Report Window

- •Rules Report Window

- •Setting Environment Variables

- •Troubleshooting

- •Finding Design Elements (Probing)

- •Probing Hierarchical Designs

- •Removing Probes

- •Exiting the Probe Command

- •Showing the Options Form

- •Checking Shorts and Opens

- •Comparing Design Elements and Parameters (Checking against the Connectivity Source)

- •Information About Online Forms

- •Probe Options Form

- •Updating Design Data in Virtuoso XL

- •Updating Layout Parameters

- •Updating Schematic Parameters

- •Updating Device Correspondence

- •Creating Device Correspondence

- •Needed Mode

- •Computer Aided Mode

- •Updating the Connectivity Reference

- •Changing the Device (Instance) View

- •Information About Online Forms

- •Change Instance View Form

- •Create Device Correspondence

- •Problems with the Interface

- •Invalid Markers from Previous Software Versions

- •Options Form Does Not Appear

- •Virtuoso XL Performance Is Slow

- •Problems with Editing

- •Components Move Slowly

- •Extra Probes Appear

- •Layout Generation Options Form Does Not Keep Values from the Last Entry

- •Parameters Not Updated

- •Schematic Not Editable

- •Warning to Update Your Design Appears at Startup

- •Problems with Connectivity

- •Connections Not Made

- •Incomplete Nets Command Does Not Recognize Connected Pins and Nets

- •Markers for Nonexistent Overlaps and Shorts Appear

- •Path Ends Not Accepted

- •Placement and Routing Do Not Run

- •Virtuoso XL Does Not Recognize Physical Vias

- •Moving Software Executables To a New Location

- •Environment Variables

- •Virtuoso XL Layout Editor

- •alignApplySeparation

- •alignApplySpacings

- •alignDirection

- •alignLayer

- •alignMethod

- •alignSelectionMode

- •alignSeparation

- •allowRotation

- •autoAbutment

- •autoArrange

- •autoPermutePins

- •autoSpace

- •checkTimeStamps

- •ciwWindow

- •compTypeRefLibs

- •constraintAssistedMode

- •createBoundaryLabel

- •crossSelect

- •extractEnable

- •extractStopLevel

- •globalPlacement

- •ignoredParams

- •ignoreNames

- •incNetCycleHilite

- •incNetHiliteLayer

- •infoWindow

- •initAspectRatio

- •initAspectRatioOption

- •initBoundaryLayer

- •initCreateBoundary

- •initCreateInstances

- •initCreateMTM

- •initCreatePins

- •initDoFolding

- •initDoStacking

- •initEstimateArea

- •initGlobalNetPins

- •initIOLabelType

- •initIOPinLayer

- •initIOPinName

- •initPinHeight

- •initPinMultiplicity

- •initPinWidth

- •initPrBoundaryH

- •initPrBoundaryW

- •initSymbolicPins

- •initUtilization

- •layoutWindow

- •lswWindow

- •lxAllowPseudoParallelNets

- •lxDeltaWidth

- •lxFingeringNames

- •lxGenerationOrientation

- •lxGenerationTopLevelOnly

- •lxInitResetSource

- •lxStackMinimalFolding

- •lxStackPartitionParameters

- •lxWidthTolerance

- •maintainConnections

- •mfactorNames

- •mfactorSplit

- •moveAsGroup

- •openWindow

- •optimizePlacement

- •paramTolerance

- •pathProbe

- •pathPurposeList

- •pathSwitchLayer

- •pathSwitchPurpose

- •preserveTerminalContacts

- •probeCycleHilite

- •probeDevice

- •probeHiliteLayer

- •probeInfoInCIW

- •probeNet

- •probePin

- •rowGroundLayer

- •rowGroundName

- •rowGroundWidth

- •rowPowerLayer

- •rowPowerName

- •rowPowerWidth

- •rowSupplyPosition

- •rowSupplySpacing

- •rowMOSSupplyPattern

- •rowSTDAllowFlip

- •rowSTDSupplyPattern

- •rulesFile

- •runTime

- •saveAs

- •saveAsCellName

- •saveAsLibName

- •saveAsViewName

- •schematicWindow

- •setPPConn

- •sfactorNames

- •sfactorParam

- •showIncNetEnable

- •stopList

- •templateFileName

- •traverseMixedHierarchies

- •updateReplacesMasters

- •updateWithMarkers

- •vcpConductorDepth

- •vcpKeepoutDepth

- •viewList

- •Wire Editor

- •allowFloatingNets

- •allowJogs

- •allowRedundantWiring

- •autoAdjustLength

- •autoShield

- •busOverride

- •busOverrideValue

- •busWireSpacing

- •busWireSpacingType

- •checkCornerCorner

- •checkCrosstalk

- •checkLength

- •checkLimitWay

- •checkMaxProcessWireWidth

- •checkMaxStackViaDepth

- •checkMaxTotalVia

- •checkMinMaskEdgeLength

- •checkMinProcessWireWidth

- •checkMiter

- •checkNetOrder

- •checkOffManGridPin

- •checkOffWireGridPin

- •checkPinSpacing

- •checkPolygonWire

- •checkProtected

- •checkReentrantPath

- •checkRegion

- •checkSameNet

- •checkSegment

- •checkStub

- •checkUseLayers

- •checkUseVias

- •checkWireExtension

- •doFile

- •enableBusRouting

- •enableTandemPair

- •gatherBusWires

- •inaccessiblePin

- •interactiveChecking

- •matchPinWidth

- •matchPinWidthValue

- •matchWireWidth

- •multiplePinsConnection

- •pinLargerMaxProcessWidth

- •pinSmallerMinProcessWidth

- •pushComponent

- •pushRouting

- •routeAsManyAsPossible

- •routeToCursor

- •routeToCursorStyle

- •sameNetChecking

- •showTimingMeter

- •showTimingOctagon

- •snapToPinOrigin

- •useDoFile

- •useRulesFile

- •viaAssistance

- •viaPattern

- •Private Environment Variables

- •Virtuoso XL Command Quick Reference

- •Using Spice and CDL For Netlist Driven Layout Generation

- •Introduction

- •Specifying Spice Designs

- •Cell Creation Rules

- •Character Considerations

- •Spice Statements

- •File Level Statements

- •Statements Allowed at File Level or within a Subckt Cell or a Top Level Cell

- •Statements Allowed within a Subckt Cell or a Top Level Cell

- •Spice Design Example

- •CDL Design Example

- •Parameter Resolution

- •Parameter Levels

- •Resolving Parameters

- •Putting the Rules Together (Examples)

- •Parameter Scaling

- •Complete ibuf Example Results

- •Virtuoso XL .do File Commands

- •Rule Hierarchy

- •circuit

- •Syntax

- •Example

- •Syntax

- •Example

- •limit

- •Syntax

- •Example

- •rule

- •Syntax

- •Example

- •Syntax

Virtuoso XL Layout Editor User Guide

Using the Virtuoso Custom Placer

(partition partition1

(shape rectangle ((5.300000 3.050000) (13.500000 10.600000))) (cell /P4)

(cell /P6) (cell /P7) (cell /P2)

(cell /P12)

)

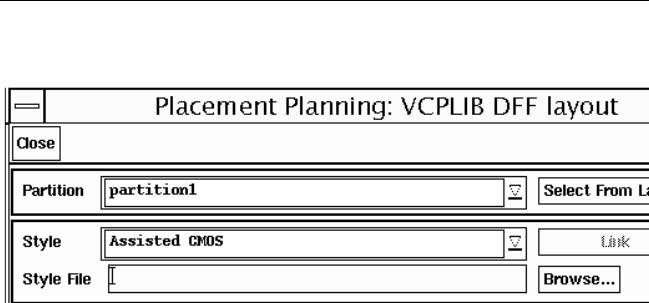

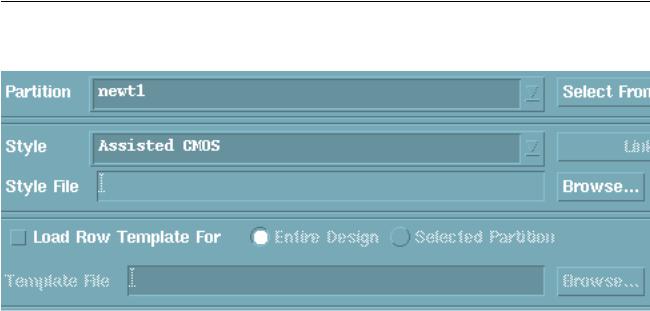

Setting Placement Planning

You define where in the layout you want to place transistors and other design elements with the Place – Placement Planning command and the Placement Planning form.

Note: Before you can set the placement planning, you or the library developer must first define thecomponent types for placement. Components that have types assigned to rows can only be placed in these rows.

There are two row definition modes for the Placement Planning form:Assisted and UserDefined.

■The assisted mode automates typical styles of MOS and standard cell placement

December 2002 |

287 |

Product Version 5.0 |

Virtuoso XL Layout Editor User Guide

Using the Virtuoso Custom Placer

■The user-defined mode offers greater flexibility but less automation and supports both transistorand cell-level placement

Assisted CMOS Placement

The Assisted CMOS row definition mode helps you define rows that fit your area budget. You can change the independent design variables that constrain the row shapes and observe their effect on area utilization and folded transistor widths.

Limitations

The component-assisted mode restricts the placement style to the most typical arrangements. There are a few limitations that are not present in the user-defined row definition mode:

■All rows must be horizontal or vertical

■All rows have the same width and span the entire placement region

Note: Row width can vary if the region is polygonal.

■Each row contains either NMOS or PMOS devices but not both and not any other component types

■The number of N and P rows is the same

■There is a regular arrangement of alternating N and P rows that follows one of these patterns:

NP

PN

December 2002 |

288 |

Product Version 5.0 |

Virtuoso XL Layout Editor User Guide

Using the Virtuoso Custom Placer

NPPN

PNNP

■All rows have the same device alignment relative to the devices in adjacent rows: inside, outside, or center

■Device rotation depends on the row and pattern.

■The rows can extend outside of the boundary/partition

Note: The placer can only place within the boundary/partition

If any of these limitations is not acceptable, you can either

■Define the rows in the user-defined mode

■Define the rows as completely as possible using the component-assisted mode and then refine the definitions in the user-defined mode

■Use assisted mode on either standard cell or MOS, but not both at the same time.

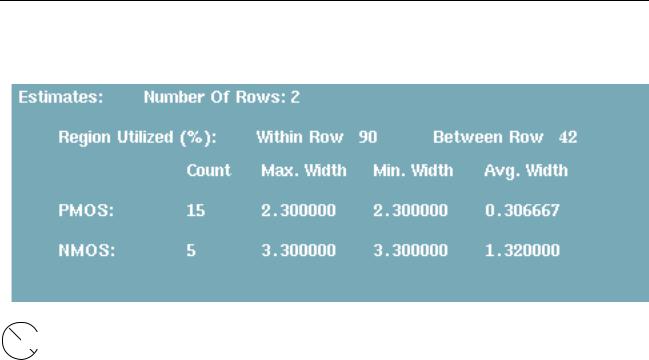

About Calculated Values

For both NMOS and PMOS transistors, the system calculates the number of transistors and the minimum, maximum, and average transistor widths. To update the displayed values, after altering variables, select Calculate Estimate.

The system also calculates the normalized percentage of Within Row and Between Row area utilization for the placement region. (In other words, a value of 100% in the Within Row field means that the entire width of the placement region is used by the devices). If there are too many devices to fit within the placement region, rows may overlap or extend outside the placement region. In this case, one or both of the Region Utilized values at the bottom of the form may be greater than 100%.

Using the Assisted CMOS Mode

To use the Assisted CMOS row definition mode,

1. Choose Place – Placement Planning.

December 2002 |

289 |

Product Version 5.0 |

Virtuoso XL Layout Editor User Guide

Using the Virtuoso Custom Placer

The Placement Planning form appears

2.Specify a partition name.

You can select a partition by clicking on Select From Layout and then clicking in the layout window to select the partition.

3.Change the Style to Assisted CMOS.

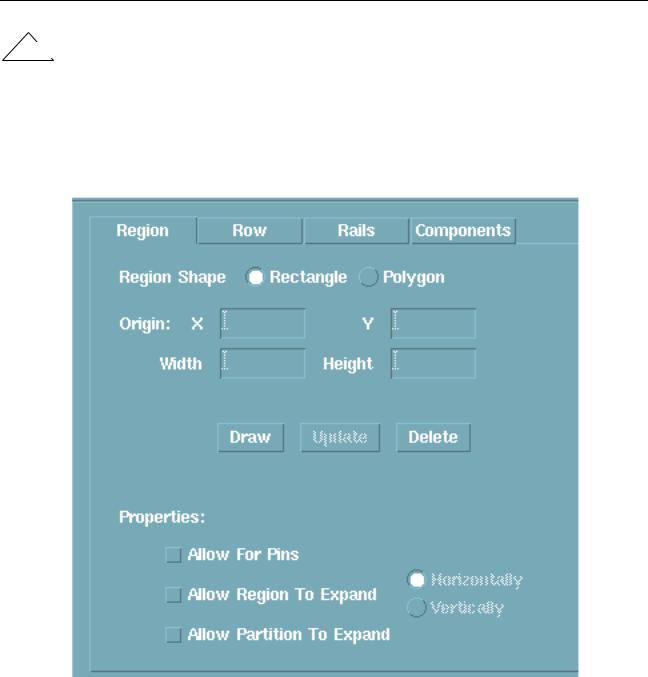

4.Click on Region to;

The placement region should be contained within the partition. For example, you might restrict assisted placement to the lower part of the partition, leaving the upper part available for manual placement. Or, you might leave space around the periphery for routing.

Type the dimensions of the drawing region in the Width and Height fields.

Type the X and Y coordinates of the location where you want the row in the Origin fields.

You can see the X and Y coordinates of the cursor position in the status line at the top of the layout window. If you do not type any coordinates, the new row is placed at the lower left corner of the design boundary.

Specify the placement region manually in the layout window, select Draw and the you are prompted to point at the first corner of the region’s rectangle.

December 2002 |

290 |

Product Version 5.0 |

Virtuoso XL Layout Editor User Guide

Using the Virtuoso Custom Placer

Important

When targeting a partition for assisted row generation, the estimator uses the entire partition area in its calculation.You can optionally specify a region within the partition by using the Draw option. If a region is defined the estimator will use the region area instead of the partition area.

Click Delete to remove the region created by the Draw option.

December 2002 |

291 |

Product Version 5.0 |

Virtuoso XL Layout Editor User Guide

Using the Virtuoso Custom Placer

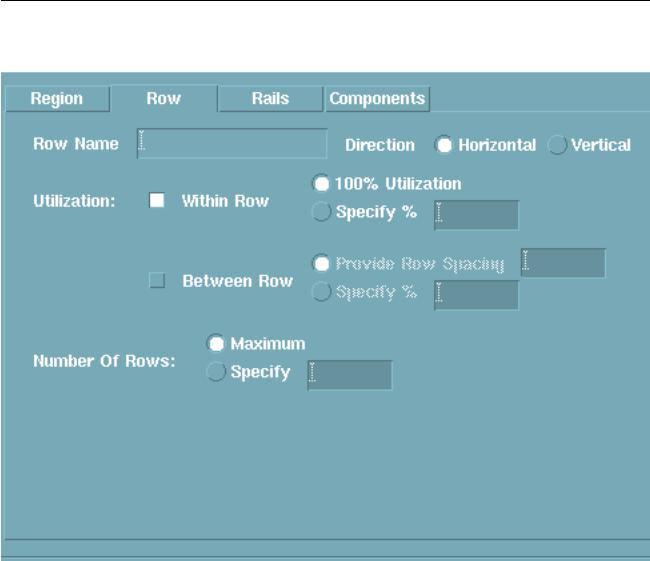

5. Select Row to update the row properties.

Note: If rows are already defined, change the Style to Manual User-Defined and the row information is displayed at the bottom of the Placement Planning form.Click on the row that you want to edit. The Row properties are updated in the Name field.

6. Set the orientation (Direction) of the row(s).

December 2002 |

292 |

Product Version 5.0 |

Virtuoso XL Layout Editor User Guide

Using the Virtuoso Custom Placer

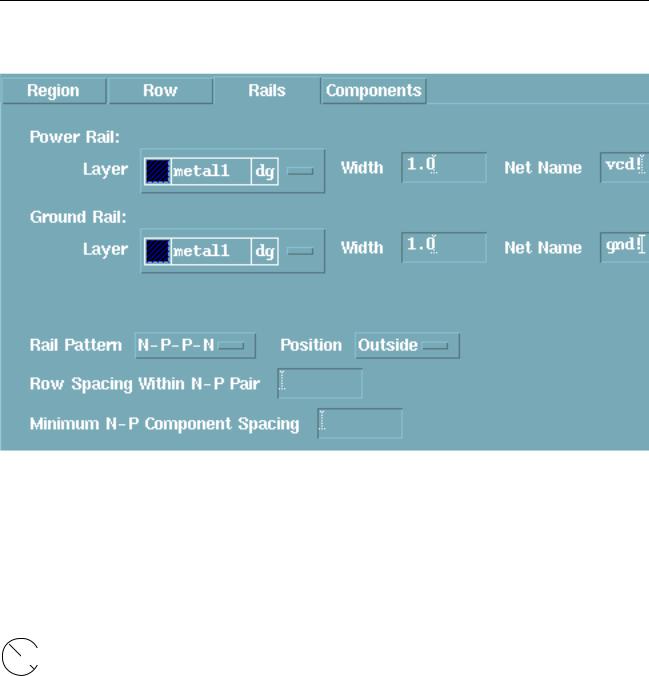

7. In the Rail section of the form;

Choose a layer and type values in the Net Name and Width fields for power and ground.

The layers are valid layers that are not used as vias or contacts.

In the Rail Pattern cyclic field, choose a pattern for the alternating N and P rows.

In the Position cyclic field determines the position of the rail relative to the row(Inside, Outside, or Center).

Caution |

Do not add a u at the end of a value for rail width and spacing rules because the value will be converted to 0.000001. For example, 12u will be converted to 0.012.

To create non-rectangular regions follow the steps below;

1.Select Place-Partitioning and create a partition for the components.

2.Select Place-Placement Planning and change the Style to Assisted CMOS.

December 2002 |

293 |

Product Version 5.0 |

Virtuoso XL Layout Editor User Guide

Using the Virtuoso Custom Placer

3.Select the partition by changing the Partition field to the partition name.

4.Select Draw and you are prompted to draw a region. Create the region inside of the partition.

5.Select Calculate Estimates. The rows are created and the row statistics are displayed at the bottom of the Placement Planning form.

6.Draw another separate region that doesn’t overlap the previous region (area now contains rows) using the Draw option.

7.Select Calculate Estimates. The rows are created and the row statistics are displayed at the bottom of the Placement Planning form.

Note: The final utilization must be calculated by hand using the row statistics from both regions.

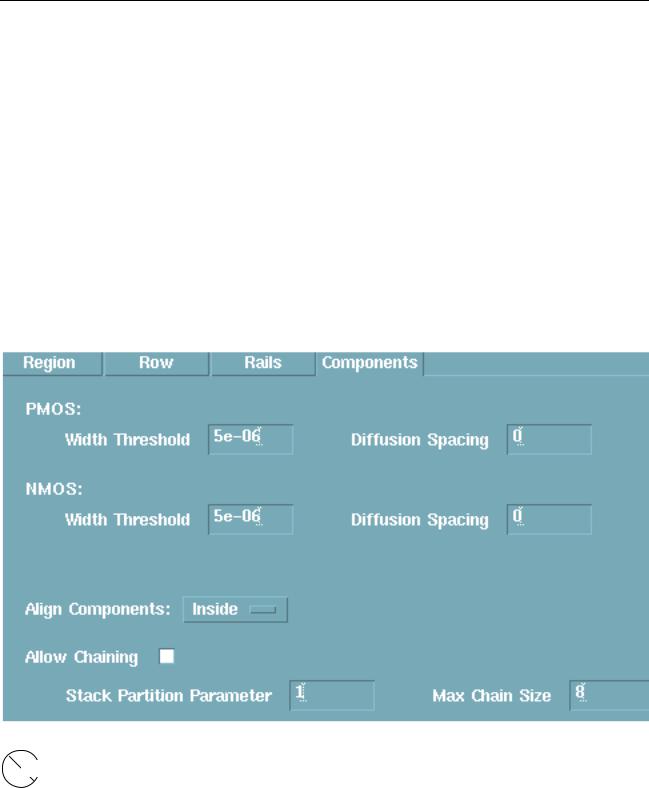

8.In the Component section of the form,

Caution |

Do not add a u at the end of a value for spacing rules because the value will be converted to 0.000001. For example, 12u will be converted to 0.012.

December 2002 |

294 |

Product Version 5.0 |

Virtuoso XL Layout Editor User Guide

Using the Virtuoso Custom Placer

In the Alignment cyclic field, chooseInside, Outside, or Center.

N-row

P-row

N-row

P-row

P-row |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P-row |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P-row |

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

N-row |

|

|

|

|

|

|

|

|

|

|

N-row |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

N-row |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

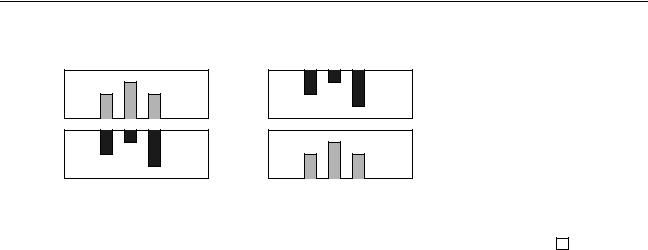

Inside (NPPN pattern) |

Outside (NP pattern) |

|

|

Center |

|||||||||||||||||||

Note: Alignment can be either top, bottom, or center for horizontal rows or right, left, or center for vertical rows.

Set the alignment of the component(s).

Type in the minimum width (Width Threshold) and required diffusion space between components within the row (Diffusion Spacing) for the PMOS and NMOS transistors.

9.To place only the devices for the selected component below the prBoundary select Regenerate All. The Update Layout option at the bottom of the Placement Planning form updates the current layout with the components and deletes existing components. This option is used on a selective basis based on the selected partition and style.

December 2002 |

295 |

Product Version 5.0 |

Virtuoso XL Layout Editor User Guide

Using the Virtuoso Custom Placer

10.Click Calculate Estimate to calculate the row count, area utilization, device count, and device widths.

Caution |

The estimator will design the rows so as to avoid any preplaced components even if they are a part of the estimator computation. You should move these components out of the placement region before invoking the estimator. (needs to be put in for all types of styles)

The system regenerates folded transistors using the new values. The section at the bottom of the form is updated with the percentage of the region utilized and width information about the PMOS and NMOS components.

11.Evaluate the device counts against the need to generate equal numbers of P and N rows. Evaluate the area utilization based on routability considerations. If necessary, change the Number of Rows or PMOS Width Threshold or NMOS Width Threshold for folding. Click Calculate Estimate to update the calculated estimates.

If necessary, redefine the placement region and begin again with Step 4.

Note: After you click Calculate Estimate, if you make extensive changes to device folding and chaining choices (either through automatic layout generation or interactive device folding), the estimates you calculate in Step 10 may become invalid.

Using the Assisted Standard Cell Mode

To use the Assisted Standard Cell row definition mode,

1. Select Place – Placement Planning.

December 2002 |

296 |

Product Version 5.0 |

Virtuoso XL Layout Editor User Guide

Using the Virtuoso Custom Placer

The Placement Planning form appears

2.Change the Style to Assisted Standard-Cell.

3.In the Region section;

Type the dimensions of the row(s) in the Width and Height fields.

Type the X and Y coordinates of the location where you want the row in the Origin field.

You can see the X and Y coordinates of the cursor position in the status line at the top of the layout window. If you do not type in any coordinates, the new row is placed at the lower left corner of the design boundary.

To specify the placement region manually in the layout window, click Draw.

The layout window prompts you to point at the first corner of the region’s rectangle.

December 2002 |

297 |

Product Version 5.0 |

Virtuoso XL Layout Editor User Guide

Using the Virtuoso Custom Placer

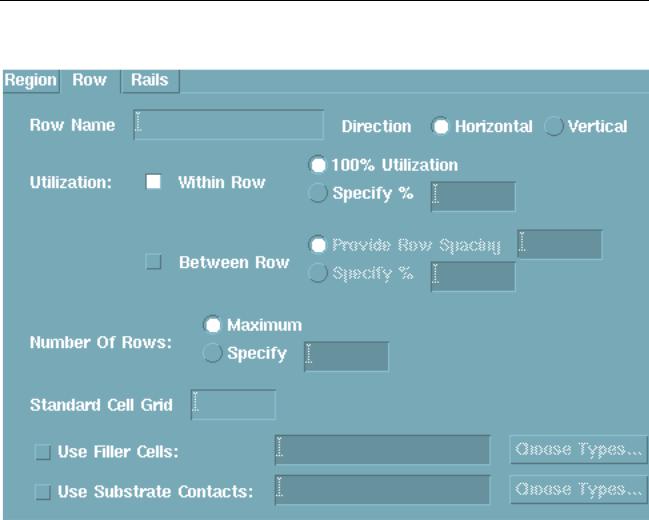

4. In the Row section of the form

Type the name of the row(s) to be designed in the Name field.

Set the orientation (Direction) of the row(s).

If you want to use filler cells that you have defined in the Edit Component Types form between the other cells in the row, click Use Filler Cells and type the names of the

filler cells into the field or clickChoose Types and choose the names of the filler cells from the list that appears in the Choose Component Types form. You must also specify a type when using the Substrate Contacts option. Use STDSUBCONT as the

Component Class.

December 2002 |

298 |

Product Version 5.0 |

Virtuoso XL Layout Editor User Guide

Using the Virtuoso Custom Placer

5. In the Rails section of the form

If applicable, choose a layer and type values in the Net Name and Width fields for power and ground nets.

Caution |

Do not add a u at the end of a value for rail spacing rules because the value will be converted to 0.000001. For example, 12u will be converted to 0.012.

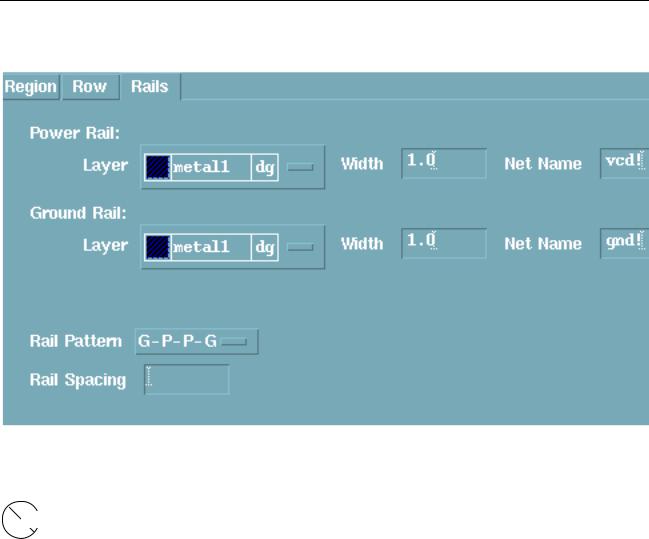

Rail Spacing.for Assisted Standard Cell mode

If no spacing value is supplied, the default behavior is to attach each rail within the row. The top of the power rail would be aligned to the top of the row, the bottom of the ground rail would be aligned to the bottom of the row.

If a spacing value is supplied, the spacing is applied between the two rails generated and centered within the row. For example; if you specify a spacing of 0 the rails will abut at the centerline (or middle) of the row. If a spacing of 2 is specified, there will be a separation of 2 between the upper and lower rail. Spacing of 1 above center and spacing of 1 below the centerline of the row.

December 2002 |

299 |

Product Version 5.0 |

Virtuoso XL Layout Editor User Guide

Using the Virtuoso Custom Placer

Spacing is provided

H |

S/2 |

|

S |

||

|

||

|

S/2 |

Spacing is not provided

H

|

|

|

|

December 2002 |

300 |

Product Version 5.0 |

|

Virtuoso XL Layout Editor User Guide

Using the Virtuoso Custom Placer

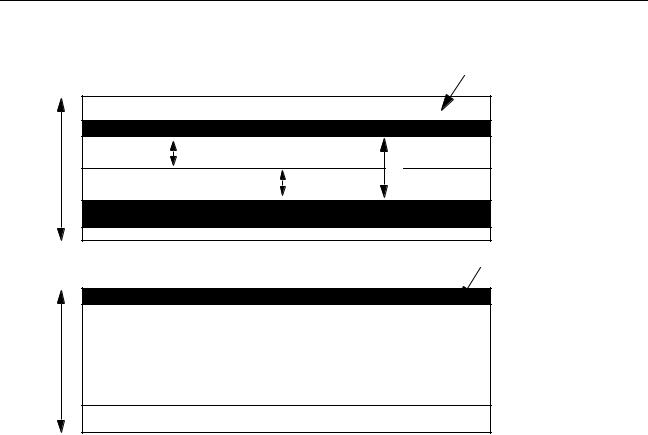

In the Pattern cyclic field, choose a pattern for the alternating ground and powerG( and P) rows.

Vdd

Gnd  PG

PG

Gnd

Vdd  GP

GP

PGGP rails not shared

GND

GP

Vdd

PG

Gnd

GPPG shared rails

6.In the Spacing field, type in the spacing you want between the rails.

7.Click Calculate Estimate to calculate the row count, area utilization, device count, and device widths.

The section at the bottom of the form is updated with the percentage of the region utilized.

If you choose to use the Regenerate All option all standard cells are regenerated once the Update Layout option is invoked. Or you can use the Generate Only Missing Components option and the missing components will be created. Generation/ regeneration only affects standard cells within the chosen partition.

Note: To modify the size of a rail, change the Rail information and then click Calculate

Estimate.

December 2002 |

301 |

Product Version 5.0 |

Virtuoso XL Layout Editor User Guide

Using the Virtuoso Custom Placer

8.Evaluate the device counts against the need to generate equal numbers of PG to GP rows. Evaluate the area utilization based on routability considerations. If necessary, change the Width or Height fields or the Width Threshold for folding. Click Calculate

Estimate to update the calculated estimates.

Note: After you click Calculate Estimate, if you make any changes to row definitions (either through automatic layout generation or interactive device folding), the estimates you calculate in Step 8 will become invalid.

9.Click Apply to save your row definitions.

Manual User-Defined Row-Based Placement

The Manual User-Defined mode for row definition lets you define row boundaries flexibly. For example, you can draw rectangles to delimit individual rows. Use the manual mode for placements above the device level or for MOS device placement styles that are not accommodated in the Assisted MOS mode.

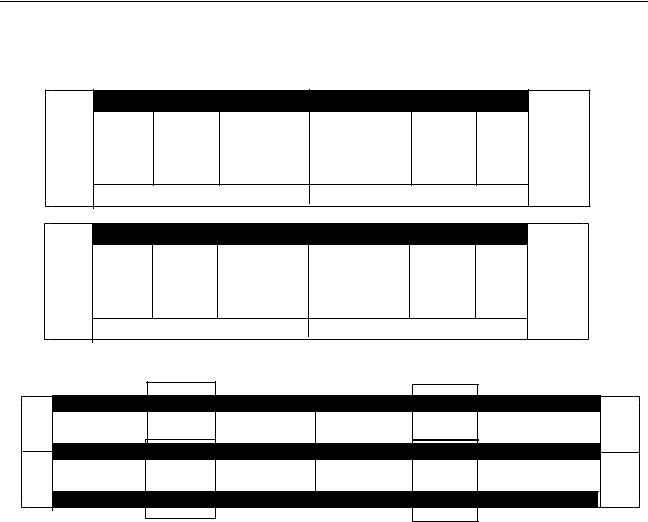

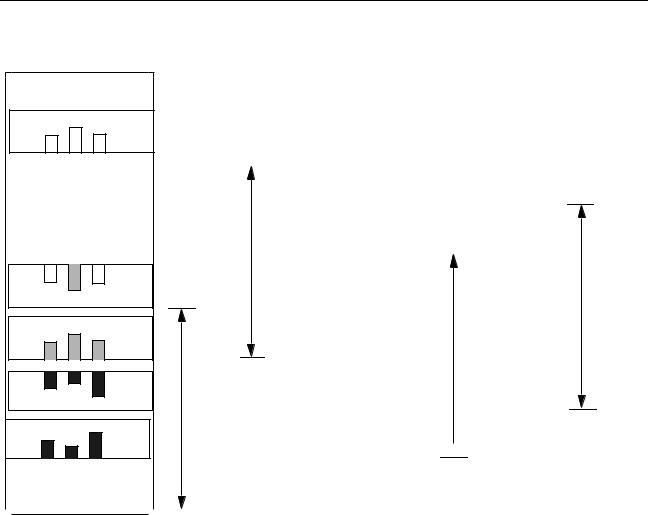

Figure 9-2 on page 302 shows an example of a placement region with four rows. Rows 1 and 2, the lower rows, span only half the placement region. Rows 3 and 4 span the entire placement region.

Figure 9-2 Examples of Rows

Defining Rows Manually

To define rows or columns manually,

1. Select Place – Placement Planning.

December 2002 |

302 |

Product Version 5.0 |

Virtuoso XL Layout Editor User Guide

Using the Virtuoso Custom Placer

The Placement Planning form appears.

2.Change the Style to Manual User-Defined.

3.Select General to define one or more rows.

Type the name of the row(s) to be designed in the Row Name field.

Set the orientation (Direction) of the row(s).

Type the dimensions of the row(s) in the Width and Height fields.

Click Draw and draw the shadow of the row. The row is not created until the Create button is invoked.

Type in the number of rows you want in the Number of Rows to Create field.

If Number of Rows to Create is greater than 1, then this will create an array of rows with the same devices and attributes at a fixed spacing between adjacent rows.

Type the X and Y coordinates of the location where you want the first row in the

Origin field.

You can see the X and Y coordinates of the cursor position in the status line at the top of the layout window. If you do not type in any coordinates, the new row is placed at the lower left corner of the design boundary.

In the Spacing Between Rows field, type the spacing you want between rows.

Caution |

Do not add a u at the end of a value for spacing rules because the value will be converted to 0.000001. For example, 12u will be converted to 0.012.

4.In the Types section on the form,

a.Select Edit and the Choose Component Types form appears

b.Select the component type and click OK. The selected component type appears in the Component Type(s) field.

c.Specify a Component Grid, Reference Point for Type and Row, Offset, and Orientations.

d.Select Create and the component type is displayed in the Types field box.

e.To change any of the component types properties select the component type in the

Types field and change the properties on the form. SelectUpdate and the component type properties are updated.

December 2002 |

303 |

Product Version 5.0 |

Virtuoso XL Layout Editor User Guide

Using the Virtuoso Custom Placer

5.In the Rails section of the form,

a.Specify the Layer, Width, and Net Name of the rail.

b.Change the Reference Point for the Row and Rail to be either Bottom, Top, or

Center.

c.Specify an Offset.

d.Click Add and the rail is displayed in the Rails field.

e.To change any of the rail properties, select the rail in the Rails field and change the properties on the form. Click Update to update the rail with the new properties.

Drawing Rows

You can define rows by drawing them, one at a time, in the layout window. SelectDraw and define the placement region for assisted MOS or cells.

Redefining a Row

Rows are actual database objects you can move and stretch graphically. To graphically edit rows make sure that the Row drawing layer purpose pair is a valid layer and made selectable in the Layer Selection Window (LSW).

You can delete a row either by changing the Style to Manual User-Defined mode. The rows are displayed at the bottom of the Placement Planning form. You can select a row and use the Delete Selected option to delete the selected tows, or graphically selecting the row in the layout window and then deleting it.

Setting Up Power and Ground Rails

You can define arrays of multiple rows in one step to create alternating rows with the same definitions. This arrangement facilitates the layout of power lines.Figure 9-3 on page 305 shows a portion of a buffer array with alternating NMOS and PMOS transistors in columns.

December 2002 |

304 |

Product Version 5.0 |

Virtuoso XL Layout Editor User Guide

Using the Virtuoso Custom Placer

Figure 9-3 Alternating Vertical NMOS and PMOS Rows

N-row

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P-row |

|

|

|

|

NPPN Array Spacing |

|||||||

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|||

P-row |

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

N-row

N-row

NPPN Array Spacing

P-row

P-row

NPPN Array Spacing

NPPN Array Spacing

|

|

|

|

|

|

|

|

|

|

|

|

NPPN Array Spacing |

N-row |

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|||||||

To define the placement style for these eight rows, you define two arrays of components. To define the PMOS rows, follow these steps:

1.Choose Place – Placement Planning.

2.Choose Manual User -Defined.

3.Create the N row as the bottom row.

4.Create the P row above the N row.

5.Create another P row.

6.Create the N row which is on the top.

7.Set Num Of Rows to Create to 2.

The row setup is now complete.

December 2002 |

305 |

Product Version 5.0 |

Virtuoso XL Layout Editor User Guide

Using the Virtuoso Custom Placer

For other arrangements of power lines between rows, you might, for example, need to define arrays of every fourth or eighth row in order to achieve the desired mirroring pattern.

About Horizontal and Vertical Rows

You can define both horizontal and vertical rows for placement. To do this, set the desired direction as you define each row or set of rows.

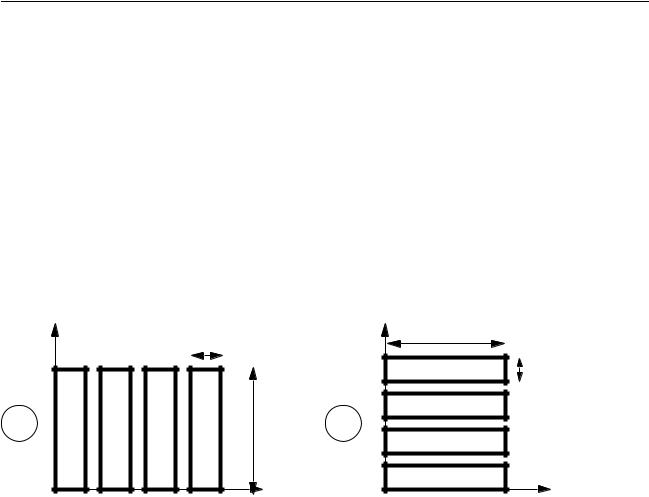

Figure 9-4 on page 306 shows how the Width and Height parameters should be set for horizontal and vertical rows. As this figure illustrates, theWidth is measured along the direction of the rows.

Figure 9-4 Setting Width and Height for Horizontal and Vertical Rows

1

(0,0)

height |

width |

|

|

|

height |

width |

2 |

|

|

|

(0,0) |

1.Row direction is Vertical, Width is 10, Height is 4, Spacing is 2.

2.Row direction is Horizontal, Width is 10, Height is 4, Spacing is 2.

About Device Orientation

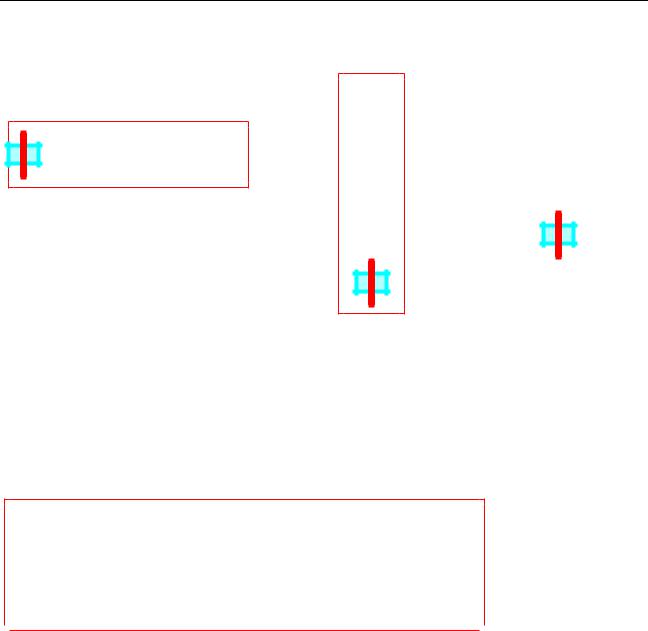

There is no implied rotation of devices in vertical rows. The Orientation value you specify in the Placement Planning form is always relative to the master cell coordinates. Figure 9-5 on page 307 shows the undesired result of placing the same device with orientation R0 (unrotated) in both a horizontal and vertical row.

December 2002 |

306 |

Product Version 5.0 |

Virtuoso XL Layout Editor User Guide

Using the Virtuoso Custom Placer

Figure 9-5 Rotation of Devices in Vertical and Horizontal Rows

Unrotated

Master

About Device Abutment and Orientation

For MOS row placement, diffusion would be abutted along the row direction as shown in

Figure 9-6 on page 307

Figure 9-6 MOS Row with Diffusion Abutted Along the Row Direction

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Unrotated |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

Permitted Orientations in row: R0, R180, MX, MY |

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

Master |

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

The permitted orientations in the example in Figure 9-6 on page 307 would depend on the orientation of the transistor in its master cell. Assuming that the polysilicon shape is vertical in the master cell for the transistor, for a horizontal row the reasonable orientations would be

R0 (unrotated), R180 (rotated 180 degrees), MX (mirrored along the X-axis) and MY (mirrored along the Y-axis). R90 would not be an advisable orientation.

For standard cells, the power and ground rails would run parallel to the row direction, as shown in Figure 9-7 on page 308.

December 2002 |

307 |

Product Version 5.0 |