- •Contents

- •Preface

- •Related Documents

- •Typographic and Syntax Conventions

- •Introduction to the Virtuoso XL Layout Editor

- •Editing Your Technology File for Virtuoso XL Layout Editor

- •Sample Technology File

- •Virtuoso XL Technology File Requirements

- •Layer Rules

- •Devices

- •Physical Rules

- •Virtuoso XL Rules (lxRules)

- •Compactor Rules

- •Preparing Your Connectivity Source for the Virtuoso XL Layout Editor

- •Placing Design Elements

- •Using Design Variables

- •Netlist Processor Expressions

- •Analog Expression Language Expressions

- •Simulation Design Variables

- •Using One-to-Many Mapping

- •Iterated Instances and Bus Pins

- •Multiplication Factor (mfactor)

- •Series-Connection Factor (sfactor)

- •One-to-Many Assignment with the Update Device Correspondence

- •Using Many-to-Many or Many-to-One Mapping

- •Modifying Many-to-Many or Many-to-One Mapping Between Components

- •Deleting Many-to-Many or Many-to-One Mapping Between Components

- •Using Virtuoso XL Properties

- •Using the lxUseCell Property to Specify Layout Devices to Use

- •Using the lvsIgnore Property to Exclude Schematic Symbols

- •Using the lxlgnoredParams Property to Exclude Device Properties

- •Using the lxRemoveDevice property to Ignore Parasitic Devices

- •Using the lxViewList and lxStopList Properties to Prepare Hierarchical Designs

- •Using the lxCombination Property to Build Complex Devices

- •Preparing Instances and Pins in Your Layout for the Virtuoso XL Layout Editor

- •Preparing Pins for the Virtuoso XL Layout Editor

- •Preparing Pins for Permutability

- •Search Order Variable

- •Syntax

- •Macros

- •Setting the permuteRule Property in the Symbol Master

- •Setting the permuteRule Property in the Device Master

- •Setting the permuteRule Property in the Symbol Instance

- •Setting the permuteRule Property in the Device Instance

- •Setting the permuteRule Property in the Component Description Format

- •Preparing Instances for Hierarchical Connectivity Checking

- •Setting Up Your Desktop

- •Customizing Your Desktop Layout

- •Using Multiple Cellviews

- •Printing to the Command Interpreter Window

- •Changing Display Colors

- •Using Bindkeys

- •Displaying Bindkeys

- •Loading Virtuoso XL Bindkeys

- •Setting Environment Variables

- •Information About Online Forms

- •Layout XL Options Form

- •Introduction to Abutment

- •Abutment Requirements

- •Setting Up Cells for Abutment

- •abutAccessDir

- •abutClass

- •Steps in Auto-Abutment

- •Sample Parameterized Cells Set Up for Abutment

- •Example 1

- •Example 2

- •Creating CMOS Pcells to Use with Abutment

- •autoAbutment Properties

- •The abutMosStretchMat Property

- •abutMosStretchMat Rules for MOS Abutment

- •Example Code Setting MOS Abutment Properties

- •Setting Environment Variables for Abutment

- •Move Together

- •Constraint Assisted

- •Using Device Abutment

- •Generating Your Layout with Virtuoso XL Layout Editor

- •Starting Virtuoso XL from the Schematic

- •Importing a Netlist for a Connectivity Reference

- •Starting Virtuoso XL from the Layout View

- •Connectivity Reference as a Netlist

- •Mapping File Structure

- •Working with Template Files

- •Saving Form Contents

- •Loading Template Files

- •Modifying Templates

- •Loading Template Files

- •Creating Template Files

- •Template File Syntax

- •General Syntax Rules

- •Boundaries Section

- •I/O Pins Section

- •Sample Template

- •Generating a Layout with Components Not Placed (Gen From Source)

- •Moving Components from the Schematic into the Layout (Pick from Schematic)

- •Placing a Group of Schematic Elements Together

- •Placing Individual Components

- •Generating Pins

- •Viewing Unplaced Instances/Pins

- •Viewing in Place

- •Manually Abutting Devices Using Pick from Schematic

- •Cloning Components

- •Cloning

- •Troubleshooting

- •Cloning Using Multiple Cellviews

- •Using Correspondence Points

- •Information About Online Forms

- •Add Correspondence Pairs Form

- •Cloning Form

- •Correspondence Pairs Form

- •Import XL Netlist Form

- •Layout Generation Options Form

- •Open File Form

- •Pick from Schematic Form

- •Remove Correspondence Components Form

- •Set Pin Label Text Style Form

- •Startup Option Form

- •Template File Form

- •Editing Your Layout with Virtuoso XL Layout Editor

- •Identifying Incomplete Nets

- •Moving Objects Manually in the Virtuoso XL Layout Editor

- •Moving Objects Using Move Options

- •Setting the Move Form to Appear Automatically

- •Aligning Objects

- •Post Selecting Devices

- •PreSelecting Devices

- •Swapping Components

- •Permuting Component Pins

- •Permuting Pins Manually

- •Checking Permutation Information

- •Using Device Locking

- •Using Automatic Spacing

- •Using Interactive Device Abutment

- •Setting Component Types

- •About Component Types

- •MOS Transistor Stacking and Folding Parameters

- •Modifying a Component Type

- •Using Transistor Chaining

- •Using Transistor Folding

- •Controlling the Folding Grid

- •Folding Transistors

- •Adding Instances to a Layout

- •Adding Pins to a Layout

- •Assigning Pins to a Net

- •Maintaining Connectivity When Editing a Flattened Pcell

- •Information About Online Forms

- •Assign Nets Form

- •Edit Component Types Form

- •Move Form

- •Set Transistor Folding Form

- •Show Incomplete Nets Form

- •Stretch Form

- •Virtuoso XL Alignment Form

- •Using the Virtuoso Custom Placer

- •Overview

- •Main Features

- •Place Menu Command Summary

- •Other Commands Used with the Virtuoso custom placer

- •Placement Styles

- •Setting Up the Virtuoso XL Layout Editor for Placement

- •Identifying the Placement Translation Rules

- •Setting Cadence Design Framework II Environment Variables

- •Setting Environment Variables for the Virtuoso Custom Router and Placer

- •Setting MOS Chaining and Folding Parameters

- •Abutting Standard Cells

- •Using Auto-Abutment During Placement

- •Placement Constraints

- •Constraint Manager Geometric Constraints

- •Pin Placement Constraints

- •Constraint Limitations

- •Placement Parameters and Component Types

- •MOS Transistor Chaining and Folding Parameters

- •Pin Placement

- •Assigning Pins to an Edge

- •Assigning Pins to a Fixed Position

- •Railing Pins

- •Loading the Template File

- •Assigning Spacing Between Pins

- •Saving Pin Placement to a Template File

- •Partitioning the Design

- •Creating a Partition

- •Loading the Template File

- •Saving Partitions to a Template File

- •Setting Placement Planning

- •Assisted CMOS Placement

- •Choose Component Types Form

- •Running the Virtuoso Custom Placer

- •Prerequisites to Placement

- •Running the Virtuoso Custom Placer: Initial Placement

- •Stopping the Placer

- •Running Load Balancing Service (LBS)

- •Troubleshooting Placement Results

- •Running the Virtuoso Custom Placer: Detailed Placement

- •Showing Congestions

- •Information About Forms

- •Auto Placer Form

- •Partitioning Form

- •Choose Component Types Form

- •Pin Placement Form

- •Load Template File Form

- •Placement Planning Form (Assisted CMOS)

- •Placement Planning Form (Assisted Standard Cell)

- •Placement Planning Form (Assisted Mixed CMOS/Standard-Cell)

- •Preparing Your Design for Routing in the Virtuoso XL Layout Editor

- •Understanding Connectivity

- •Pseudo-Parallel Connections

- •Selecting Layers

- •Changing Layers

- •Connecting Nets

- •Creating Paths

- •Connecting Nets with Path Stitching

- •Connecting Nets with Design Shapes

- •Checking Connectivity with Flight Lines

- •Checking Connectivity with Markers

- •Finding Markers

- •Explaining Markers

- •Deleting Single Markers

- •Deleting All Markers

- •Using the Virtuoso Compactor on a Routed Design

- •Overview

- •Main Features

- •Wire Editing Commands

- •Virtuoso Custom Router to Virtuoso XL Command Mapping

- •Prerequisites

- •Rule Information

- •Net Connectivity Information

- •Routing Area Boundary

- •Enabling Wire Editing

- •Toggling Between Virtuoso XL and Wire Editing Enabled

- •Loading ASCII Rules Files

- •The Wire Editing Environment

- •Status Banner

- •Preview Wires and Routing Aids

- •Mouse Button Behavior

- •Using Environment Variables

- •Routing Paths

- •Routing a Single Path

- •Routing Multiple Paths

- •Preventing and Checking Design Rule Violations

- •Interactive Checking

- •Same Net Checking

- •Checking Regions

- •Checking Route and Pin Violations

- •Routing Options and Styles

- •Matching Path Width and Pin Widths

- •Matching Path Width and Pin Widths for Multiple Paths

- •Gathering Bus Wires

- •Spacing for Gathered Bus Wires

- •Overriding Bus Spacing

- •Rotating the Bus Cursor

- •Cycling the Control Wire

- •Allowing Redundant Wiring

- •Allowing Orthogonal Jogs

- •Route To Cursor

- •Allow Floating Nets

- •Connecting Multiple Component Pins

- •Pushing Routes and Components

- •Routing Shielded Nets

- •Routing Tandem Layer Pairs

- •Using Vias

- •Changing Layers and Adding Vias

- •Using Vias Patterns on Multiple Paths

- •Legal Via Sites

- •Rotating Vias

- •Pseudo Vias

- •Editing Routed Connections

- •Stretching Paths and Vias

- •Splitting and Stretching Paths

- •Copying Routes

- •Using Critic Wire

- •Compacting Paths Using Pull

- •Displaying Reports

- •Displaying Routing Status Reports

- •Displaying Network Reports

- •Displaying Component Reports

- •Displaying Net Reports

- •Creating Rules Reports

- •Search Reports

- •Saving Reports

- •Setting Constraints

- •Using the Virtuoso Constraint Manager

- •Using .do Files

- •About the Forms

- •Add Via Form

- •Check Routes Form

- •Create Path Form

- •Find File Form

- •Layout

- •Reports Form

- •Route Options Form

- •Save As Form

- •Search Form

- •Split Form

- •Via Pattern Pop-up

- •Reports

- •Route Status Report Window

- •Network Report Window

- •Instance Report Window

- •Net Report Window

- •Rules Report Window

- •Setting Environment Variables

- •Troubleshooting

- •Finding Design Elements (Probing)

- •Probing Hierarchical Designs

- •Removing Probes

- •Exiting the Probe Command

- •Showing the Options Form

- •Checking Shorts and Opens

- •Comparing Design Elements and Parameters (Checking against the Connectivity Source)

- •Information About Online Forms

- •Probe Options Form

- •Updating Design Data in Virtuoso XL

- •Updating Layout Parameters

- •Updating Schematic Parameters

- •Updating Device Correspondence

- •Creating Device Correspondence

- •Needed Mode

- •Computer Aided Mode

- •Updating the Connectivity Reference

- •Changing the Device (Instance) View

- •Information About Online Forms

- •Change Instance View Form

- •Create Device Correspondence

- •Problems with the Interface

- •Invalid Markers from Previous Software Versions

- •Options Form Does Not Appear

- •Virtuoso XL Performance Is Slow

- •Problems with Editing

- •Components Move Slowly

- •Extra Probes Appear

- •Layout Generation Options Form Does Not Keep Values from the Last Entry

- •Parameters Not Updated

- •Schematic Not Editable

- •Warning to Update Your Design Appears at Startup

- •Problems with Connectivity

- •Connections Not Made

- •Incomplete Nets Command Does Not Recognize Connected Pins and Nets

- •Markers for Nonexistent Overlaps and Shorts Appear

- •Path Ends Not Accepted

- •Placement and Routing Do Not Run

- •Virtuoso XL Does Not Recognize Physical Vias

- •Moving Software Executables To a New Location

- •Environment Variables

- •Virtuoso XL Layout Editor

- •alignApplySeparation

- •alignApplySpacings

- •alignDirection

- •alignLayer

- •alignMethod

- •alignSelectionMode

- •alignSeparation

- •allowRotation

- •autoAbutment

- •autoArrange

- •autoPermutePins

- •autoSpace

- •checkTimeStamps

- •ciwWindow

- •compTypeRefLibs

- •constraintAssistedMode

- •createBoundaryLabel

- •crossSelect

- •extractEnable

- •extractStopLevel

- •globalPlacement

- •ignoredParams

- •ignoreNames

- •incNetCycleHilite

- •incNetHiliteLayer

- •infoWindow

- •initAspectRatio

- •initAspectRatioOption

- •initBoundaryLayer

- •initCreateBoundary

- •initCreateInstances

- •initCreateMTM

- •initCreatePins

- •initDoFolding

- •initDoStacking

- •initEstimateArea

- •initGlobalNetPins

- •initIOLabelType

- •initIOPinLayer

- •initIOPinName

- •initPinHeight

- •initPinMultiplicity

- •initPinWidth

- •initPrBoundaryH

- •initPrBoundaryW

- •initSymbolicPins

- •initUtilization

- •layoutWindow

- •lswWindow

- •lxAllowPseudoParallelNets

- •lxDeltaWidth

- •lxFingeringNames

- •lxGenerationOrientation

- •lxGenerationTopLevelOnly

- •lxInitResetSource

- •lxStackMinimalFolding

- •lxStackPartitionParameters

- •lxWidthTolerance

- •maintainConnections

- •mfactorNames

- •mfactorSplit

- •moveAsGroup

- •openWindow

- •optimizePlacement

- •paramTolerance

- •pathProbe

- •pathPurposeList

- •pathSwitchLayer

- •pathSwitchPurpose

- •preserveTerminalContacts

- •probeCycleHilite

- •probeDevice

- •probeHiliteLayer

- •probeInfoInCIW

- •probeNet

- •probePin

- •rowGroundLayer

- •rowGroundName

- •rowGroundWidth

- •rowPowerLayer

- •rowPowerName

- •rowPowerWidth

- •rowSupplyPosition

- •rowSupplySpacing

- •rowMOSSupplyPattern

- •rowSTDAllowFlip

- •rowSTDSupplyPattern

- •rulesFile

- •runTime

- •saveAs

- •saveAsCellName

- •saveAsLibName

- •saveAsViewName

- •schematicWindow

- •setPPConn

- •sfactorNames

- •sfactorParam

- •showIncNetEnable

- •stopList

- •templateFileName

- •traverseMixedHierarchies

- •updateReplacesMasters

- •updateWithMarkers

- •vcpConductorDepth

- •vcpKeepoutDepth

- •viewList

- •Wire Editor

- •allowFloatingNets

- •allowJogs

- •allowRedundantWiring

- •autoAdjustLength

- •autoShield

- •busOverride

- •busOverrideValue

- •busWireSpacing

- •busWireSpacingType

- •checkCornerCorner

- •checkCrosstalk

- •checkLength

- •checkLimitWay

- •checkMaxProcessWireWidth

- •checkMaxStackViaDepth

- •checkMaxTotalVia

- •checkMinMaskEdgeLength

- •checkMinProcessWireWidth

- •checkMiter

- •checkNetOrder

- •checkOffManGridPin

- •checkOffWireGridPin

- •checkPinSpacing

- •checkPolygonWire

- •checkProtected

- •checkReentrantPath

- •checkRegion

- •checkSameNet

- •checkSegment

- •checkStub

- •checkUseLayers

- •checkUseVias

- •checkWireExtension

- •doFile

- •enableBusRouting

- •enableTandemPair

- •gatherBusWires

- •inaccessiblePin

- •interactiveChecking

- •matchPinWidth

- •matchPinWidthValue

- •matchWireWidth

- •multiplePinsConnection

- •pinLargerMaxProcessWidth

- •pinSmallerMinProcessWidth

- •pushComponent

- •pushRouting

- •routeAsManyAsPossible

- •routeToCursor

- •routeToCursorStyle

- •sameNetChecking

- •showTimingMeter

- •showTimingOctagon

- •snapToPinOrigin

- •useDoFile

- •useRulesFile

- •viaAssistance

- •viaPattern

- •Private Environment Variables

- •Virtuoso XL Command Quick Reference

- •Using Spice and CDL For Netlist Driven Layout Generation

- •Introduction

- •Specifying Spice Designs

- •Cell Creation Rules

- •Character Considerations

- •Spice Statements

- •File Level Statements

- •Statements Allowed at File Level or within a Subckt Cell or a Top Level Cell

- •Statements Allowed within a Subckt Cell or a Top Level Cell

- •Spice Design Example

- •CDL Design Example

- •Parameter Resolution

- •Parameter Levels

- •Resolving Parameters

- •Putting the Rules Together (Examples)

- •Parameter Scaling

- •Complete ibuf Example Results

- •Virtuoso XL .do File Commands

- •Rule Hierarchy

- •circuit

- •Syntax

- •Example

- •Syntax

- •Example

- •limit

- •Syntax

- •Example

- •rule

- •Syntax

- •Example

- •Syntax

Virtuoso XL Layout Editor User Guide

Generating Your Layout with Virtuoso XL Layout Editor

Note: Netlists in the CDL (Circuit Description Language) and SPICE (3f4) format can be imported

3.Choose whether you want to copy the imported netlist file to the destination library, link the imported netlist file to the destination library, or move the imported netlist file to the destination library.

4.In the Library field, type the name of the library in which you want to store the netlist.

5.In the Cell field, type the name of the cell in which you want to store the netlist.

6.In the View field, type the name of the view you want to give the netlist.

To see the libraries, cells, and views in the Library Browser, put the cursor in the Library or Cell or View fields and clickBrowse.

7.Click OK.

Virtuoso XL imports the netlist to the library, cell, and view name you specified. You can now use this netlist as a connectivity reference for a Virtuoso XL design.

Starting Virtuoso XL from the Layout View

To start the Virtuoso XL from a layout window, follow these steps.

1. From the CIW, choose File – Open.

December 2002 |

139 |

Product Version 5.0 |

Virtuoso XL Layout Editor User Guide

Generating Your Layout with Virtuoso XL Layout Editor

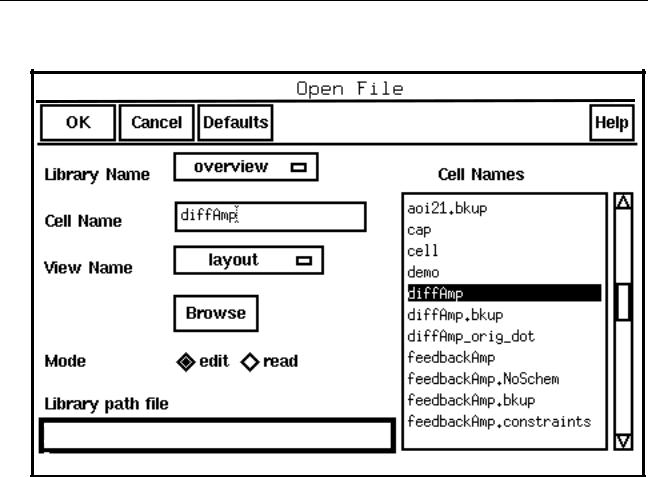

The Open File form appears.

user/mnt2/home/cds.lib

2.In the Library Name cyclic field, choose a library name.

3.In the Cell Name field, type a cell name.

4.In the View Name cyclic field, choose a layout view.

5.Click OK.

The layout view you specified appears.

6.From the layout window, choose Tools – Layout XL.

The default configuration of Virtuoso XL appears: the schematic window, the layout window, the CIW, and the LSW.

Note: Layout XL does not appear in the Tools menu unless the Virtuoso XL software is installed. If you do not see Layout XL in the Tools menu, check with your system administrator.

December 2002 |

140 |

Product Version 5.0 |

Virtuoso XL Layout Editor User Guide

Generating Your Layout with Virtuoso XL Layout Editor

If the layout from which you chose the Layout XL command has no connectivity reference (schematic or netlist) associated with it, the Define Connectivity Reference form appears.

7.Choose one of the following as the connectivity source type.

If there is no connectivity reference for the layout, choose None.

Virtuoso XL is installed, but Virtuoso XL commands requiring information from a connectivity source are disabled. You can at a later time define a connectivity reference by choosing Connectivity – Update – Source.

When you choose None (no connectivity reference), the connectivity model requires that the nets of pins and instance terminals cannot be changed, but the nets of all other shapes can be changed if they connect to a pin or instance terminal.

If the connectivity reference is a schematic, choose Schematic and do one of the following:

-Type the name of the library, cell, and view into Library, Cell, and View fields.

-Click Browse to see what cells are available in the Library Browser, and click on a cell name in the Library Browser.

-Click Sel by Cursor and then click on an open schematic.

You can click Browse to open the Library Browser to find a netlist and click on the netlist name to enter it in the Define Connectivity Reference form.

8. Click OK.

December 2002 |

141 |

Product Version 5.0 |

Virtuoso XL Layout Editor User Guide

Generating Your Layout with Virtuoso XL Layout Editor

Virtuoso XL opens a schematic window showing the schematic you specified.

December 2002 |

142 |

Product Version 5.0 |