Konspekt_lektsy_MPT

.pdfФедеральное государственное бюджетное образовательное учреждение высшего профессионального образования «Национальный исследовательский ядерный университет МИФИ»

Саровский физико-технический институт факультет информационных технологий и электроники

Кафедра №2 «Электроники»

Микропроцессорная техника

КОНСПЕКТ ЛЕКЦИЙ

г.Саров

2011г.

УДК 32.973 П34

В.В. Писецкий «Микропроцессорная техника». Конспект лекций. СарФТИ НИЯУ МИФИ, Саров, 2011 г.

Конспект лекций посвящен изучению различных типов ядер МПС и устройств, применяемых в микропроцессорной технике.

П34 Последний раздел посвящен процессу отладки и инструментарию, используемому для комплексной отладки МПС. Конспект основан на лекциях, читаемым в СарФТИ НИЯУ МИФИ. Рекомендуется студентам, чья специализация связана с разработкой встраиваемых систем и написанию для них программного обеспечения.

©Писецкий В.В. 2011 г.

©СарФТИ НИЯУ МИФИ 2011 г.

2

ОГЛАВЛЕНИЕ |

|

Раздел 1. Виды МПТ-средств, используемых в качестве ядра МПУ. |

6 |

Раздел 2. Функциональная схема МПУ |

21 |

2.1. Адресные пространства и их взаимодействие |

21 |

2.1.1. Параллельные адресные пространства |

22 |

2.1.2. Совмещенные адресные пространства |

23 |

2.1.3. Смешанные адресные пространства |

24 |

2.2. Расширенное адресное пространство. |

26 |

2.2.1. Метод регистровых пар |

28 |

2.2.2. Метод оконного доступа |

29 |

2.2.3. Доступ с помощью сегментных регистров |

31 |

Раздел 3. Структурная схема МПУ. |

33 |

Раздел 4. Блоки питания МПУ |

38 |

4.1. Общие требования |

38 |

4.2. Общие вопросы электропитания и заземления |

39 |

4.3. Гальваническая развязка |

46 |

Раздел 5. Память МПУ. |

49 |

5.1. Память программ МПУ |

49 |

5.1.1. ПЗУ масочного типа |

49 |

5.1.2. ППЗУ |

49 |

5.1.3. УФППЗУ |

50 |

5.1.4. ЭППЗУ |

50 |

5.1.5. Flash-ROM |

51 |

5.2. Память данных |

51 |

5.3. Энергонезависимая память |

52 |

5.3.1. Микросхемы памяти FRAM |

52 |

5.3.2. Микросхемы памяти MRAM |

56 |

Раздел 6. Синтез автоматов |

62 |

6.1. Схемотехническая реализация автомата |

62 |

6.2. Программная реализация автомата |

71 |

6.2.1. Классическая Switch-технология |

71 |

6.2.2. Технология построения программы для микроконтроллера по графу автомата |

75 |

Раздел 7. Шины МПУ. |

80 |

7.1. Шины микропроцессорной системы |

82 |

7.2. Циклы обмена информацией |

87 |

Раздел 8. Системы отладки МПУ |

95 |

8.1. Основные понятия и термины |

95 |

8.2. Процесс отладки МПУ |

99 |

8.3. Функция средств отладки |

102 |

8.3.1. Автоматизация программирования МПУ или разработки ПС. |

102 |

8.3.2. Управление прототипом МПУ при комплексной отладке. |

104 |

8.3.3. Контроль функционирования и регистрации состояния МПУ. |

104 |

8.3.4 Запись отлаженных программных средств в БИС ППЗУ. |

104 |

8.4. МПУ как объект отладки |

105 |

8.5. Требования, предъявляемые к системе отладки |

108 |

8.5.1. Требования невидимости |

108 |

8.5.2. Требования к предоставляемому сервису |

111 |

8.5.3. Требование прозрачности. |

112 |

8.6. Режимы работы отлаживаемых МПУ. |

112 |

8.6.1. Процессор контрольных точек (точек останова) |

112 |

8.6.2. Трассировка. |

113 |

8.6.3. Частичная эмуляция АС. |

114 |

8.7. Инструментальные средства отладки |

115 |

8.7.1. Общие сведения об отладочных средствах |

115 |

8.7.2. Внутрисхемный эмулятор |

119 |

8.7.3. Интегрированная среда разработки |

120 |

8.7.4. Отладочный монитор |

122 |

8.7.5. Эмуляторы ПЗУ |

123 |

8.7.6. Встроенные средства отладки |

125 |

Литература |

128 |

3

СПИСОК ИЛЛЮСТРАЦИЙ |

|

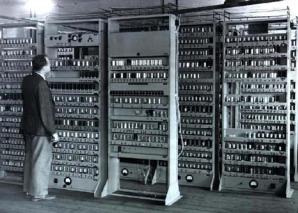

Рис 1.1. Ламповая ЭВМ............................................................................................................................... |

7 |

Рис 1.2. ЭВМ ENIAC .................................................................................................................................. |

9 |

Рис 1.3. ЭВМ IBM-360................................................................................................................................ |

11 |

Рис 1.4. ЭВМ БЭСМ-6 ............................................................................................................................... |

11 |

Рис 1.5. Микропроцессор Intel 4004 ......................................................................................................... |

13 |

Рис 1.6. Микропроцессор Intel 8008 ......................................................................................................... |

14 |

Рис 1.7. Микропроцессор Z80 и первый массовый игровой компьютер ZX Spectrum......................... |

16 |

Рис 1.8. Микропроцессор I8086................................................................................................................ |

16 |

Рис 2.1. Параллельные адресные пространства ресурсов А и В......................................................... |

22 |

Рис 2.2. Совмещенные адресные пространства ресурсов А и В.......................................................... |

23 |

Рис 2.3. Смешанные адресные пространства ресурсов А и В.............................................................. |

24 |

Рис 2.4. Расширенное и непосредственно адресуемое адресные пространства............................... |

27 |

Рис 2.5. Метод регистровых пар в исходном варианте ......................................................................... |

28 |

Рис 2.6. Метод регистровых пар в современном варианте................................................................... |

29 |

Рис 2.7. Метод оконного доступа............................................................................................................. |

30 |

Рис 2.8. Доступ с помощью сегментных регистров................................................................................ |

31 |

Рис 2.9. Вычисление физического адреса с помощью сегментного регистра..................................... |

32 |

Рис 3.1. Пример структурной схемы МПУ............................................................................................... |

33 |

Рис 3.2. Пример структурной схемы ОЭВМ MSP430 ............................................................................. |

35 |

Рис 3.3. Пример структурной схемы ОЭВМ архитектуры MCS-51........................................................ |

36 |

Рис 3.4. Пример структурной схемы ПСНК 8051F020............................................................................ |

37 |

Рис 4.1. Пример протокола включения и выключения блока питания................................................. |

38 |

Рис 4.2. Типовая схема сетевого фильтра блока питания.................................................................... |

40 |

Рис. 4.3. Правильное подключение ПУ ................................................................................................... |

41 |

Рис. 4.4. Появление разности потенциалов при двухпроводном кабеле питания.............................. |

43 |

Рис. 4.5. Подключение незаземленного устройства.............................................................................. |

44 |

Рис 5.1. Кристаллическая решетка BaTiO3 ............................................................................................. |

54 |

Рис 5.2 FRAM ячейка из двух транзисторов и двух конденсаторов...................................................... |

55 |

Рис 5.2 FRAM ячейка на одном транзисторе и конденсаторе............................................................... |

55 |

Рис. 6.1. Функциональная схема автомата Мура................................................................................... |

62 |

Рис. 6.2. Функциональная схема автомата Мили................................................................................... |

62 |

Рис. 6.3. Модификации функциональной схемы автомата Мили......................................................... |

63 |

Рис. 6.4. Преобразованная схема автомата Мура................................................................................. |

63 |

Рис. 6.5. Регистрация автоматом сигналов различной длительности ................................................. |

64 |

Рис. 6.6. Пример цикла с ожиданиями .................................................................................................... |

65 |

Рис. 6.7. Активация автомата по наступлению события........................................................................ |

65 |

Рис. 6.8. Схема автомата Мура с таблицей в ПЗУ................................................................................. |

66 |

Рис. 6.9. Схема автомата Мура с небольшим количеством состояний и выходов............................. |

67 |

Рис. 6.10. Схема автомата Мили с небольшим количеством состояний и выходов........................... |

67 |

Рис. 6.11. Пример: схема автомата......................................................................................................... |

68 |

Рис. 6.12. Пример: Фрагмент графа......................................................................................................... |

69 |

Рис. 6.13. Пример: Заполнение таблицы для состояния № 12............................................................. |

70 |

Рис. 6.14 Вариант реализации управляющего автомата клапана........................................................ |

72 |

Рис. 6.15 Сокращенный вариант реализации управляющего автомата клапана. .............................. |

73 |

Рис. 6.16. Пример графа переходов (рис 14.12 из книги «Switch-технология. Алгоритмизация и |

|

программирование задач логического управления») ............................................................................ |

74 |

Рис. 6.17. Программы, основанные на графе рис.6.16 .......................................................................... |

74 |

Рис. 6.18. Граф рис.6.16 с пронумерованными вершинами.................................................................. |

77 |

Рис. 6.19. Программа, синтезированная по графу рис. 6.18. ................................................................ |

77 |

Рис. 6.20 Фрагмент программы, синтезированной по графу рис. 6.18 с синхронизацией по таймеру |

|

T0. ............................................................................................................................................................... |

78 |

Рис. 6.21. Фрагмент программы, синтезированной по графу рис. 6.18 с синхронизацией по |

|

внешнему сигналу, подключенному к 3 биту порта Р2. ......................................................................... |

79 |

Рис. 2.1. Мультиплексирование шин адреса и данных.......................................................................... |

85 |

Рис. 7.2. Синхронный обмен и асинхронный обмен............................................................................... |

86 |

Рис. 7.3. Цикл чтения на магистрали Q-bus............................................................................................ |

88 |

Рис. 7.4. Цикл записи на магистрали Q-bus. ........................................................................................... |

88 |

Рис. 7.5. Цикл «ввод-пауза-вывод» на магистрали Q-bus. .................................................................... |

90 |

Рис. 7.6. Цикл чтения из УВВ на магистрали ISA. .................................................................................. |

91 |

Рис. 7.7. Цикл записи в УВВ на магистрали ISA. .................................................................................... |

91 |

Рис. 7.8. Временные диаграммы чтения и записи для синхронной демультиплексированной шины. |

|

..................................................................................................................................................................... |

93 |

4

Рис. 7.9. Временные диаграммы чтения и записи для синхронной мультиплексированной шины |

...94 |

Рис 8.1. Система отладки МПУ (общий случай) ..................................................................................... |

96 |

Рис 8.2. Система отладки МПУ (расширенный случай)......................................................................... |

98 |

Рис 8.3. Этапы процесса отладки ............................................................................................................ |

99 |

Рис 8.4. Перераспределение адресного пространства памяти системы (мапмепинг) ..................... |

115 |

Рис 8.5. Структурная схема эмулятора ПЗУ......................................................................................... |

124 |

5

Раздел 1. Виды МПТ-средств, используемых в качестве ядра МПУ.

Для того чтобы понять факт существования множества разнообразных типов вычислительных устройств полезно оглянуться на их историю. Законы развития в вычислительной технике, как и в электронике таковы, что новое схемотехническое решение, новое устройство, полностью заменяющее старое, достаточно быстро вытесняет своего предшественника. Если же замена не полная – у устройства–предшественника имеются функции (или – возможности реализации их), которых нет у устройства–потомка, то устройство предшественник не исчезает бесследно, а продолжает развиваться –

всторону совершенствования своих уникальных возможностей.

Ввычислительной технике принято разделать вычислительную технику на поколения, как и в геологии – на периоды. ЭВМ относят к тому или иному поколению в зависимости от типа основных используемых в ней элементов или от технологии их изготовления.

Ясно, что границы поколений в смысле времени сильно размыты, так как в одно и то же время фактически выпускались ЭВМ различных типов. Для отдельной же машины вопрос о ее принадлежности к тому или иному поколению решается достаточно просто, поскольку история развития производства процессоров практически полностью повторяет историю развития технологии производства электронных компонентов и схем.

Самые первые электронные компьютеры появились в первой половине XX века. Они могли делать значительно больше механических калькуляторов, которые лишь складывали, вычитали и умножали. Это были электронные машины, способные решать

сложные задачи.

6

Использование электроники – взамен механики для расчетов и обработки данных, не главное отличие ЭВМ от их механических предшественников. ЭВМ имели две отличительные особенности, которыми предыдущие машины не обладали.

Одна из них состояла в том, что они могли выполнять

определенную последовательность операций по заранее заданной

программе или последовательно решать задачи разных типов. Другая же особенность - способность хранить информацию в

специальной памяти.

Первый этап (поколение), который может датироваться периодом с 40-х по конец 50-х годов, характерен созданием процессоров с использованием электромеханических реле, памяти на ферритовых сердечниках и вакуумных ламп, на базе которых строились логические элементы.

Рис 1.1. Ламповая ЭВМ

Использование электронной лампы в качестве основного элемента ЭВМ создавало множество проблем. Из-за того, что высота стеклянной лампы – 7 см., машины были огромных размеров. Каждые 7-8 минут одна из ламп выходила из строя, а так как в компьютере их было 15 - 20 тысяч, то для и замены поврежденной лампы требовалось очень много времени. Кроме того, вакуумные лампы требовали подогрева катода, поэтому они выделяли огромное

7

количество тепла, и для эксплуатации такого компьютера требовались специальные системы охлаждения.

Тепло доставляло и другие неудобства – из-за него постоянно окислялись контакты многочисленных разъемов и, как гласят легенды, в комплекте к такой ЭВМ поставлялась киянка (деревянный молоток) – для «отстукивания модулей с целью устранения контактной ошибки».

Другая, родившаяся в те же времена легенда, гласила, что ЭВМ не переносят женщин. Достаточно, якобы, зайти женщине в зал, где установлена машина, чтобы начались сбои. Эта легенда до сих пор популярна в США, где программирование традиционно считается мужской профессией. Самое забавное, что легенда имеет под собой техническое обоснование. Дело в том, что лампа (как и микросхемы КМОП) имеет практически бесконечное входное сопротивление, и, стало быть, чувствительна к помехам от статического электричества. Главный источник статического электричества в быту – длинные волосы и одежда из синтетических тканей, а первую синтетику стали носить именно женщины. Они же тогда и носили длинные прически…

Третья легенда породила термин применяемый сейчас, правда, программистами. Одной из причин частой замены ламп считалась такая: их тепло и свечение привлекали жуков, которые залетали внутрь машины и вызывали короткое замыкание. Соответственно, устранение такого сбоя – «обезжучивание» (Debugs). Разобраться изза чего машина выдала неправильный результат – из-за сигнала, прошедшего «куда не надо» благодаря жучку или из-за некорректной программы было непросто. Отсюда и произошел термин "жучки" (bugs), под которым подразумевают ошибки в программных и аппаратных средствах компьютеров, и название программы Debuger.

Чтобы обслуживать огромный компьютер, нужны были целые бригады инженеров. Устройств ввода в этих компьютерах не было,

8

поэтому данные заносились в память при помощи соединения нужного штекера с нужным гнездом, что также было чревато ошибками.

Рис 1.2. ЭВМ ENIAC

Примерами машин I-го поколения могут служить легендарные

Mark 1, ENIAC, EDSAC.

ENIAC содержала 17468 ламп и более 80000 других компонентов. При работе ENIAC потреблял 150 КВт электроэнергии. Фактически ENIAC представлял собой механический арифмометр, в котором механические части заменены на электронные эквиваленты. Для запоминания каждого 20-разрядного числа требовалось 10 колец из 10 триггеров. На это уходило 100 сдвоенных ламп!

Harvard Mark II, построенный в сентябре 1947 года практически представлял собой большой калькулятор. В качестве памяти, хранившей 50 чисел с плавающей точкой, использовалась схема на реле. На них же было сделано арифметико-логическое устройство. Именно в Harvard Mark II забрался таракан, вызвав сбой при проведении операций с плавающей точкой. Обнаруживший его техник записал в лабораторном журнале: «Сегодня обнаружен первый настоящий баг». К записи он приложил бережно собранные останки насекомого.

Вторым этапом, с середины 50-х до середины 60-х, стало внедрение транзисторов. Транзисторы монтировались уже на печатные платы, монтируемые в стойки. Как и ранее, обычно ЭВМ состояла из нескольких стоек. За счет сокращения длинны внутренних

9

линий связи возросло быстродействие, повысилась надёжность. Отсутствие нитей накала в транзисторах привело к существенному уменьшению энергопотребления машиной.

К середине 60-х годов были созданы более компактные внешние устройства, что позволило фирме Digital Equipment выпустить в 1965 г. первый мини-компьютер PDP-8 размером с холодильник и стоимостью всего лишь около 20 тысяч долларов, что, естественно, не соизмеримо с размерами и стоимостью ЭВМ ENIAC.

Одновременно с процессом замены электронных ламп транзисторами совершенствовались методы хранения информации. Увеличился объем памяти, а магнитную ленту, впервые примененную

вЭВМ первого поколения, начали использовать как для ввода, так и для вывода информации.

Ав середине 60-х годов получило распространение хранение информации на дисках. Существенные изменения в архитектуре компьютеров позволили достичь быстродействия в миллион операций

всекунду!

Примерами транзисторных компьютеров могут послужить "Стретч" (Англия), "Атлас" (США). В то время СССР шел в ногу со временем и выпускал ЭВМ мирового уровня (например - "БЭСМ-6").

Третьим этапом, наступившим в середине 60-х годов, стало использование микросхем.

Первые интегральные схемы (ИС) появились в 1964 году. Появление ИС вызвало подлинную революцию в вычислительной технике. Ведь одна такая микросхема способна заменить тысячи транзисторов. Кроме того, внутри ИС обычно изготавливается целый функциональный блок, заменяющий плату транзисторной ЭВМ. Все связи между отдельными деталями выполнены внутри герметичного корпуса и, следовательно, не подвержены окислению. В наружу же выходит сравнительно небольшое количество входных и выходных

10