Лаба 4_

.docx

Выпишем минимальные ДНФ J2 и K2:

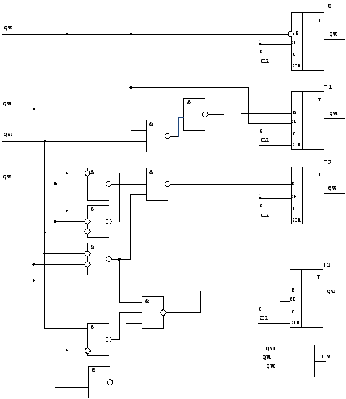

Диаграммы Вейча функций возбуждения J3K3-триггера счетчика:

Зададим значения неизвестных переменных ai и bi.

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

x |

x |

|

|

|

|

x |

x |

0 |

0 |

|

||||||||||||

|

x |

x |

|

|

|

x |

x |

0 |

0 |

|

||||||||||||||

|

|

0 |

1 |

0 |

0 |

|

|

|

|

|

||||||||||||||

|

0 |

0 |

x |

x |

|

|

|

x |

x |

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

Диаграмма J3 |

|

Диаграмма K3 |

|||||||||||||||||||||

Выпишем минимальные ДНФ J3 и K3:

Получим минимальное выражение функции декодирования последнего состояния (TC):

|

|

|

|

|

||

|

|

x |

x |

|

|

|

|

x |

x |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

x |

x |

|

|

|

|

|

|

|

|

|

|

|

|||||

Выпишем минимальную ДНФ TC:

Выходной сигнал переноса CEO для дальнейшего увеличения разрядности двоично-десятичных счётчиков организуется выражением:

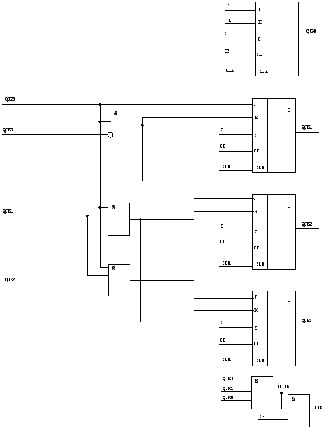

Схема двоично-десятичного счётчика с асинхронным входом предварительной установки в 0, построенного на DV-триггерах.

Схема двоично-десятичного счётчика с асинхронным входом предварительной установки в 0, построенного на JK-триггерах.

Описание триггерной схемы на языке VHDL:

entity counter_1 is

port (

CLR,C,CE: in BIT;

Q: buffer BIT_VECTOR (3 downto 0);

TC: buffer BIT;

CEO: out BIT

);

end counter_1;

architecture counter_1_arch of counter_1 is

begin

process (CLR,C)

begin

if CLR='1' then Q <= "0000";

elsif CE='0' then null;

elsif C'event and C='1' then

case Q is

when "0010" => Q <= "0011";

when "0011" => Q <= "0100";

when "0100" => Q <= "0101";

when "0101" => Q <= "0110";

when "0110" => Q <= "0111";

when "0111" => Q <= "1000";

when "1000" => Q <= "1001";

when "1001" => Q <= "1010";

when "1010" => Q <= "1011";

when "1011" => Q <= "0010";

when others => Q <= "0000";

end case;

end if;

end process;

TC <= Q(3) and Q(0) ;

CEO <= CE and TC ;

end counter_1_arch;

Схема эксперимента, на которой три счётчика могут быть соединены последовательно или параллельно (в зависимости от управляющего сигнала с панели RG1).