- •1 Исходные данные на дипломное проектирование

- •1.2 Анализ исходных данных

- •2 Разработка алгоритма упокс

- •3 Разработка структурной схемы упокс

- •4 Разработка функциональной схемы

- •5 Разработка компонентов упокс

- •5.1 Выбор системы автоматизированного проектирования плис

- •5.2 Специфика конструирования и отладки на плис и sopc.

- •5.3 Алгоритм декодирования синхросигнала

- •5.4 Разработка компонента “Count”

- •5.5 Разработка компонента “gen_Adr”

- •5.6 Разработка компонента “dff”

- •5.7 Разработка компонента “dff_Block”

- •5.8 Разработка компонента “Or”

- •5.9 Разработка компонента “chet_Err”

- •5.10 Разработка компонента “Priemnik”

- •5.11 Разработка компонента “coder”

- •5.12 Разработка компонента “bc”

- •5.13 Разработка компонента “Sborka_Coder”

- •5.14 Расчет тактовой частоты

- •5.16 Программирование плис

- •6 Экономическая часть

- •6.1 Разработка и расчёт сетевого графика

- •6.2 Расчет себестоимости разработки дипломного проекта

- •6.2.1 Общие положения

- •6.2.2 Расчет затрат на основные материалы

- •6.2.3 Расчет затрат на изделия внешней поставки

- •6.2.4 Транспортно-заготовительные расходы

- •6.2.5 Расчет основной заработной платы

- •6.2.6 Расчет резерва на отпуск

- •6.2.7 Расчет средств по статье «Страховых взносов на основную заработную плату»

- •6.2.8 Расчет отчисления на обязательное социальное страхование работников от несчастных случаев на производстве и профессиональных заболеваний

- •6.3 Экономическая эффективность

- •7 Безопасность и экологичность

- •7.1 Анализ основных источников опасности

- •7.2 Требования безопасности к рабочим помещениям

- •7.3Требования безопасности к производственному помещению

- •7.4 Требования к обслуживающему персоналу

- •7.5 Производственная санитария

- •7.6 Дерево событий

- •7.7 Экологичность проекта

- •7.8 Пожарная безопасность при эксплуатации эвм

- •7.9 Оказание первой помощи при поражении электрическим током

- •Перечень сокращений

- •Vhdl - описание компонента “Count”

- •Vhdl - описание компонента “gen_Adr”

- •Vhdl - описание компонента “dff”

- •Vhdl - описание компонента “Or”

- •Vhdl - описание компонента “coder”

5.3 Алгоритм декодирования синхросигнала

5.3.1 Согласно исходным данным на дипломное проектирование, устройство приема и обработки кодированных сигналов должен декодировать синхросигналы двух типов.

Задачей блока декодирования синхросигнала является точное определение (выделение) синхросигнала на информационной линии. Для выделения необходим отсчет временного интервала, 1,5 мкс.

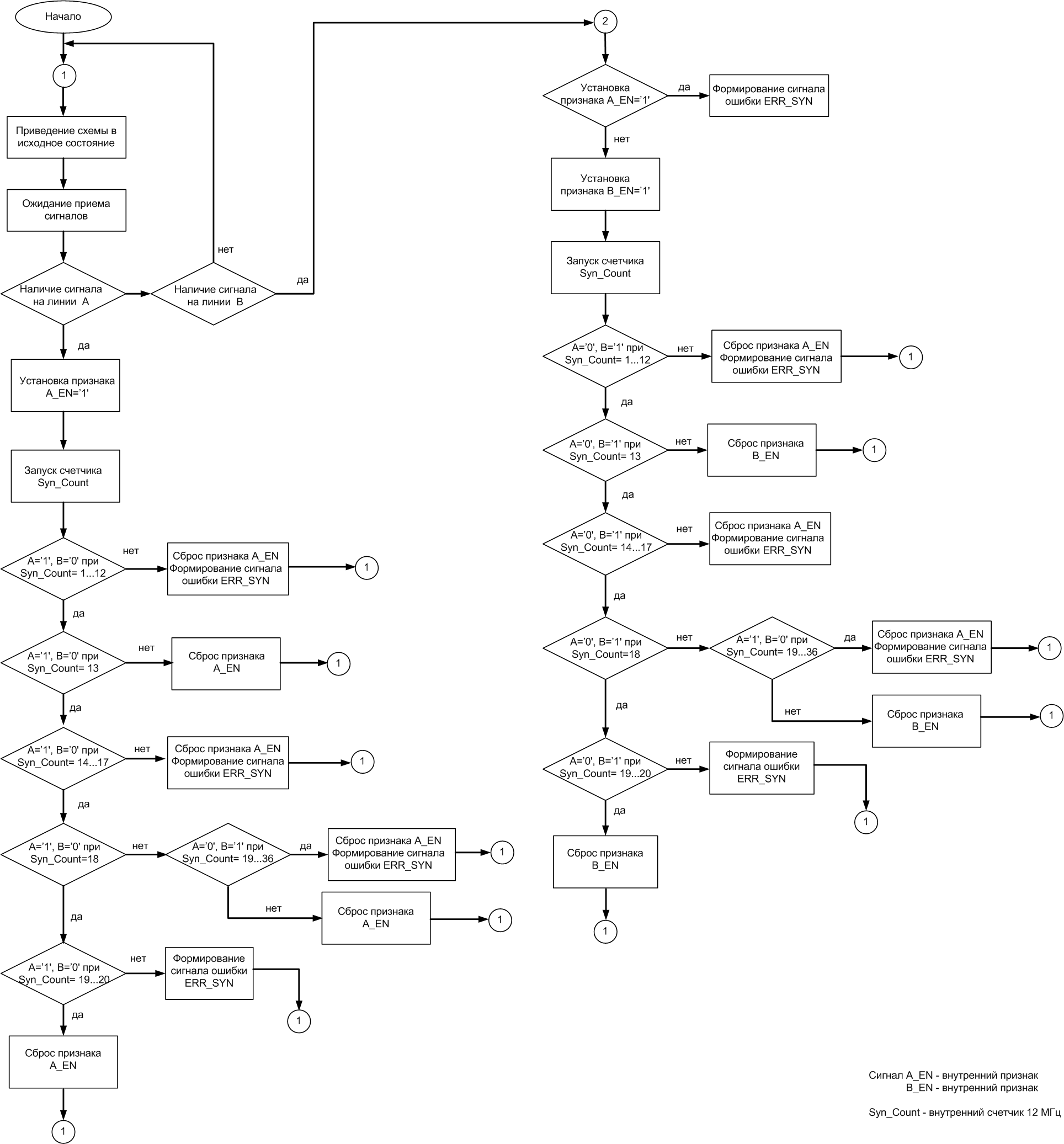

Алгоритм работы блока декодирования синхросигнала представлен на рисунке 5.1. После подачи питания на схему происходит приведение схемы в исходное состояние, после чего схема переходит в режим ожидания появления сигналов на информационных линиях. В случае появления сигнала на одной из линий, устанавливается соответствующий признак сигнала: сигналы A_EN или B_EN переходят в состояние логической ‘1’, после чего по переднему фронту одного из этих сигналов запускается счетчик и схема начинает работу по одной из веток алгоритма. Счет ведется от 1 до 12 с одновременной проверкой наличия информации на линиях “A” и “B”. Если за это время информация изменилась, то формируется признак ошибки со снятием признака сигнала: сигнал ERR_SYN переходит в состояние логической ‘1’, сигналы A_EN или B_EN соответственно в состояние логического ‘0’. При достижении счетчиком Syn_Count значения 13 происходит проверка изменения информации на линиях “A” и “B”. В случае инвертирования информации на линиях происходит сброс признака информации: сигналы “A_EN” или “B_EN” переходят в состояние логического ‘0’, так как принимаемая информация не является синхросигналом. В случае сохранения состояния на информационных линиях продолжается счет до 18 с одновременной проверкой сохранения состояния на информационных линиях “A” и “B” счет продолжается от 19 до 36 с одновременной проверкой состояния сигналов на линиях. При значении счетчика 36 формируется сигнал разрешения декодирования: сигнал “SYN” переходит в состояние логической ‘1’. В противном случае счет продолжается до 24. при изменении состояния на линиях в момент счета формируется сигнал ошибки ERR_SYN, иначе сбрасывается признаки “A_EN” или “B_EN” и схема переходит в режим ожидания.

Рисунок 5.1 – Алгоритм декодирования синхросигнала

5.4 Разработка компонента “Count”

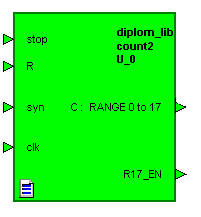

5.4.1 Условное графическое изображение компонента “Count” представлено на рисунке 5.2. Компонент реализован с помощью VHDL-описания.

Рисунок 5.2 – Условное графическое изображение компонента “Count”

5.4.2 VHDL - описания компонента “Count” представлен в приложение А.

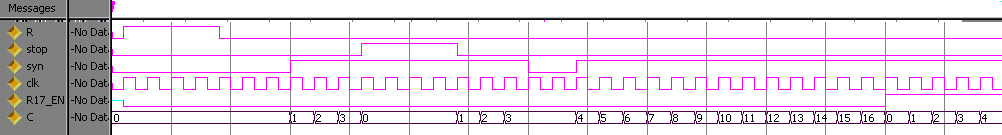

5.4.3 Для моделирования работы компонента была разработана тестовая программа. Результаты моделирования в пакете ModelSim представлены на рисунке 5.3

Рисунок 5.3 – Результаты моделирования компонента “Count”

5.4.4 На основе компонента был произведен синтез логической схемы с помощью пакета LeonardoSpectrum. Синтезированная схема представлена на рисунке 5.4

Рисунок 5.4 – Синтезированная схема компонента “Count”

5.5 Разработка компонента “gen_Adr”

5.5.1 VHDL - описание компонента “GEN_Adr” представлен в приложение Б.

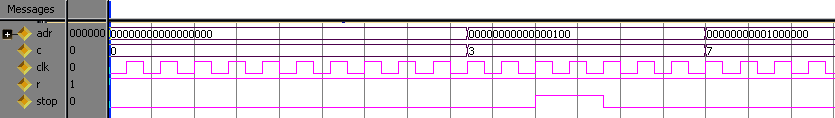

5.5.2 Для моделирования работы компонента была разработана тестовая программа. Результаты моделирования в пакете ModelSim представлены на рисунке 5.5

Рисунок 5.5 – Результаты моделирования компонента “GEN_Adr”

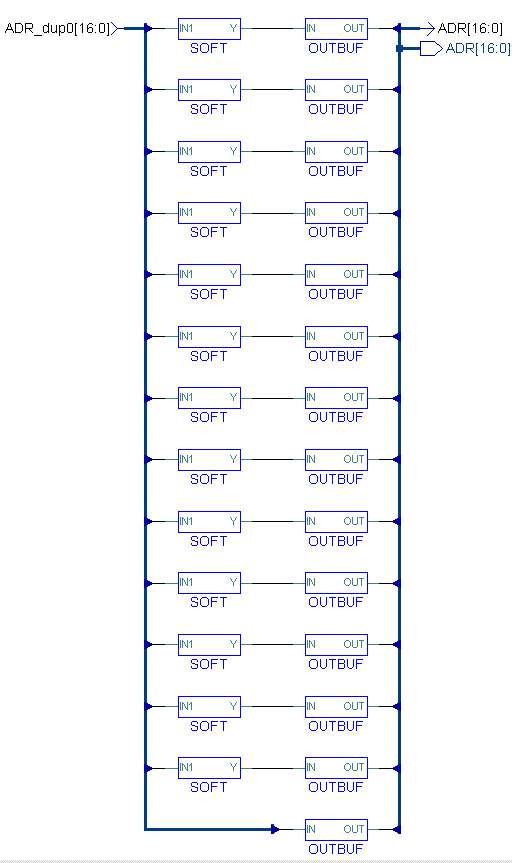

5.5.3 На основе компонента был произведен синтез логической схемы с помощью пакета LeonardoSpectrum. Синтезированная схема изображена на рисунке 5.6

Рисунок 5.6 – Синтезированная схема компонента “GEN_Adr”