ФЕДЕРАЛЬНОЕ АГЕНСТВО СВЯЗИ

Государственное образовательное учреждение

высшего профессионального образования

Московский технический университет связи и информатики

Курсовая работа

по дисциплине

«ВЫЧИСЛИТЕЛЬНЫЕ МАШИНЫ, СИСТЕМЫ И СЕТИ»

Вариант №19.

Курс: 4

Факультет: ЗОТФ

Группа: УИ0751

Студент: Хренков Д. А.

Преподаватель:

Максименко В. Н.

2011 г.

-

Задание на курсовую работу.

I=1; J=9.

Разработать аппаратное и программное обеспечение микропроцессорной системы для управления полуавтоматической установкой для сортировки посылок.

-

Разработать функциональную схему микропроцессорной системы управления технологическим процессом.

-

Разработать программную модель микропроцессорной системы.

-

Разработать принципиальную схему микропроцессорной системы.

-

Разработать алгоритм и программу управления технологическим процессом.

-

Рассчитать быстродействие и объем требуемой памяти программы.

Исходные данные.

|

Величина |

Выражение |

Значение |

|

Тип микропроцессора |

КР1810ВМ86 |

КР1810ВМ86 |

|

Адрес порта ввода |

0Jh |

09h |

|

Адрес порта вывода |

1: 0[J+1]h; 2: 0[J+2]h |

1: 0Ah; 2: 0Bh |

|

Количество датчиков |

N = 20 + 10 x I + 5 x J |

N = 75 |

|

Количество исполнительных элементов |

M = 5 x (I + J) + 3 |

M = 53 |

|

Номер I-го датчика DI |

l = 20 + I |

I = 21 |

|

Номер k-го датчика Dk |

k = 10 + 10 x I + 5 x J |

k = 55 |

|

Номер r-го исполнительного элемента ИЭr |

r = 3 x (I + J) + 3 |

r = 33 |

Алгоритм формирования логического сигнала, подаваемого на исполнительный элемент ИЭr

|

Датчики |

Исполнительный элемент |

|

|

Dl=20+I=21 |

Dk = 10+10xI+5xJ=65 |

ИЭr = 3x(I+J)+3=33 |

|

0 |

0 |

Выключается (лог."0") |

|

0 |

1 |

Включается (лог. "1") |

|

1 |

0 |

Включается с задержкой Т |

|

1 |

1 |

Не изменяется |

Программа DELAY, реализующая задержку на «T» секунд, записана по адресу 2(I+J)h=2Ah.

-

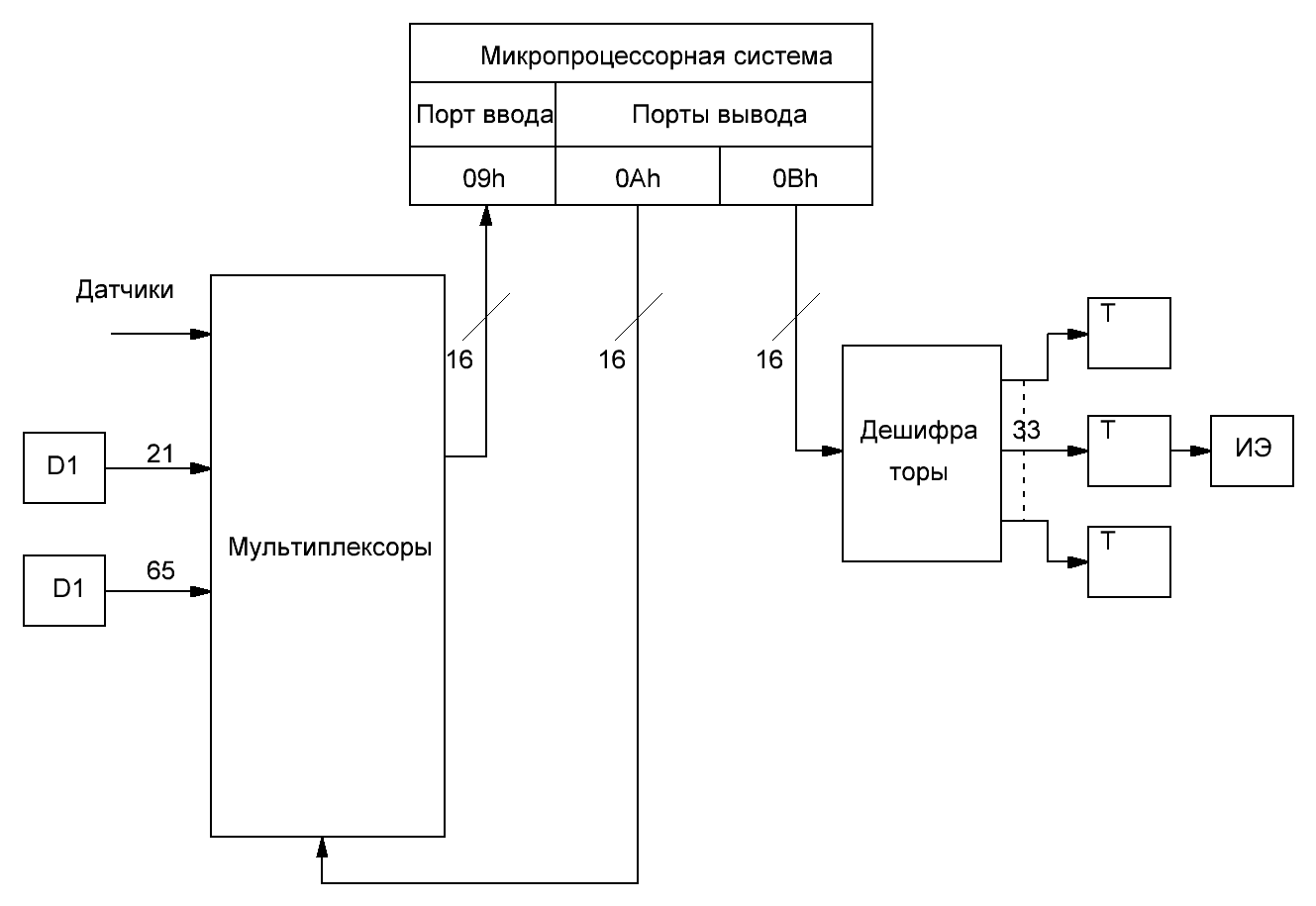

Функциональная схема микропроцессорной системы.

Рис. 1. Функциональная схема микропроцессорного устройства.

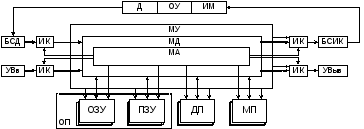

Микропроцессорная система (МПС) содержит в своем составе, по крайней мере, один микропроцессор (МП), один или несколько модулей основной (ОЗУ и ПЗУ) и дополнительной памяти, устройства ввода и вывода, блоки сопряжения (контроллеры) с устройствами ввода и вывода, которые связаны друг с другом с помощью системной магистрали, состоящей, в общем случае, из магистралей (шин) адресов (МА, ША), магистралей (шин) данных (МД, ШД) и магистралей (шин) управления (МУ, ШУ).

ОУ – объект управления,

Д – датчики,

ИМ – исполнительные механизмы,

ИК – информационные контроллеры,

БСД – блок сопряжения с датчиками,

БСИК – блок сопряжения с информационными контроллерами,

ОП – основная память,

ДП – дополнительная память.

ОЗУ МПС обеспечивает чтение и запись информации и реализуется как энергозависимая память, содержимое которой стирается при выключении МПС.

Рис. 2 Структурная схема микропроцессорной системы.

ПЗУ

обеспечивает только чтение информации

и реализуется в виде энергонезависимой

памяти. Контроллеры представляют собой

устройства сопряжения аппаратуры

ввода-вывода с системной магистралью

и реализуют определенный интерфейс.

Магистраль обеспечивает коммуникацию

аппаратных средств МПС и представляет

собой набор проводников и усилителей

сигналов.

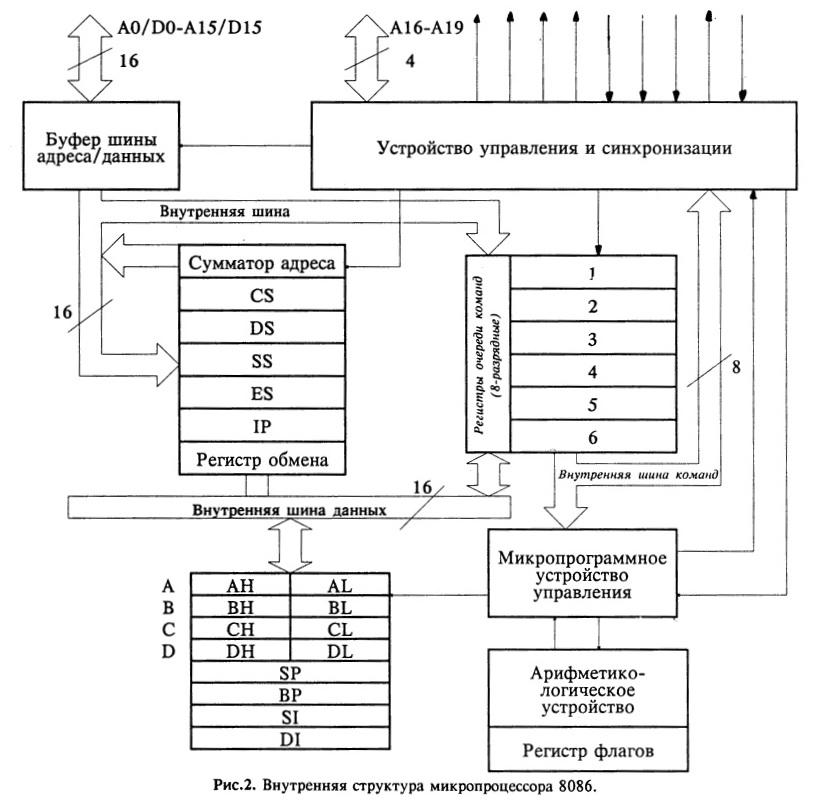

Рис. 3. Структурная схема микропроцессора.