- •Contents

- •Introduction

- •1.1 Scope

- •Figure 1-1: Main system blocks

- •1.2 Summary

- •See Chapter 2, Memory Map.

- •Level sensitive interrupts.

- •Programmed interrupt source available

- •See Chapter 3, Interrupt Controller.

- •Free-running or periodic timer modes.

- •See Chapter 4, Timer.

- •See Chapter 5, Communications Channel.

- •"Wait for Interrupt" Pause mode.

- •See Chapter 6, Remap and Pause.

- •Memory Map

- •2.1 Introduction

- •2.2 Memory Map Base Addresses

- •Interrupt Controller

- •3.1 Introduction

- •Figure 3-1: FIQ and IRQ interrupts

- •3.2 Interrupt Control

- •Figure 3-2: Interrupt Controller Bit Slice

- •3.3 Interrupt Controller Register Descriptions

- •3.5 Interrupt Controller Memory Map

- •Timer

- •4.1 Introduction

- •4.2 Timer Operation

- •Figure 4-1: Timer Block Diagram

- •Figure 4-2: Timer Pre-scale Unit

- •4.3 Timer Register Descriptions

- •4.3.1 Load Register

- •4.3.2 Value

- •4.3.3 Clear

- •4.3.4 Control Register

- •Figure 4-3: Timer Register Bit Positions

- •1—Timer Enabled

- •1—Periodic Timer Model

- •Clock

- •Divided by

- •Stages of

- •Pre-scale

- •Undefined

- •Table 4-1: Bits 3 – 2: Prescale bits

- •4.4 Timer Memory Map

- •Address

- •Read Location

- •Write Location

- •TimerBase

- •Timer1Load

- •Timer1Load

- •TimerBase + 0x04

- •Timer1Value

- •Reserved

- •TimerBase + 0x08

- •Timer1Control

- •Timer1Control

- •TimerBase + 0x0C

- •Reserved

- •Timer1Clear

- •TimerBase + 0x10

- •Reserved

- •Reserved

- •TimerBase + 0x20

- •Timer2Load

- •Timer2Load

- •TimerBase + 0x24

- •Timer2Value

- •Reserved

- •TimerBase + 0x28

- •Timer2Control

- •Timer2Control

- •TimerBase + 0x2C

- •Reserved

- •Timer2Clear

- •TimerBase + 0x30

- •Reserved

- •Reserved

- •Table 4-2: Timer Address Map

- •Communications Channel

- •5.1 Introduction

- •Remap and Pause

- •6.1 Introduction

- •6.2 Pause

- •6.4 Reset Status

- •6.5 Clear Reset Memory Map

- •6.6 Remap and Pause Memory Map

- •Address

- •Read Location

- •Write Location

- •RemapBase

- •Reserved

- •Pause

- •RemapBase + 0x10

- •Identification

- •Reserved

- •RemapBase + 0x20

- •Reserved

- •ClearResetMap

- •RemapBase + 0x30

- •ResetStatus

- •ResetStatusSet

- •RemapBase + 0x34

- •Reserved

- •ResetStatusClear

- •Table 6-1: Remap and Pause Memory Map

Interrupt Controller

3.1Introduction

The interrupt controller provides a simple software interface to the interrupt system. In this specification certain interrupt bits are defined for the basic functionality required in a system design, whilst the remaining bits are available for use by other devices in any particular implementation.

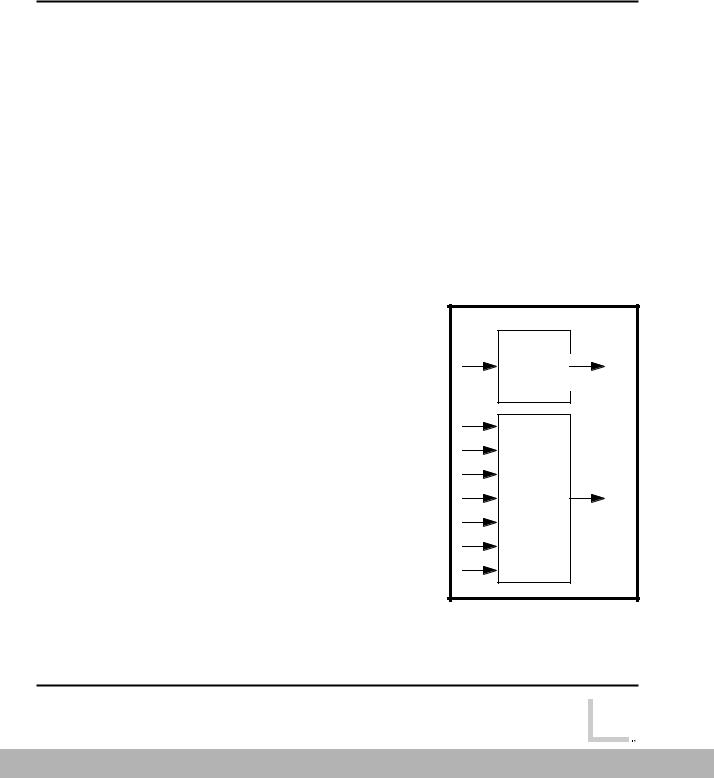

In an ARM system two levels of interrupt are available, FIQ (Fast Interrupt Request) for fast, low latency interrupt handling and IRQ (Interrupt Request) for more general interrupts.

Ideally, in an ARM system, only a single FIQ source would be in use at any particular time. This provides a true low-latency interrupt, as a single source ensures that the interrupt service routine may be executed directly without the need to determine the source of the interrupt. It also reduces the interrupt latency as the extra banked registers, which are available for FIQ interrupts, may be used to maximum efficiency by preventing the need for a context save.

Separate interrupt controllers are used for FIQ and IRQ, the difference is that only a single bit position is defined for FIQ, which is intended for use by a single interrupt source, whilst 32 bits are available in the IRQ controller. A number of methods may be used to extend the IRQ interrupt controller, should more than 32 interrupt source be required.

FIQ

Control

IRQ

Control

Figure 3-1: FIQ and IRQ interrupts

3-2 |

Reference Peripherals Specification |

|

|

|

ARM DDI 0062D |

|

|

|

|

|

|

Open Access

Interrupt Controller

The IRQ interrupt controller uses a bit position for each different interrupt source and bit positions are defined for a software programmed interrupt, a communications channel and timers. Bit 0 is unassigned in the IRQ controller so that it may share the same interrupt source as the FIQ controller.

All interrupt source inputs shall be active HIGH and level sensitive, any inversion or latching required to provide edge sensitivity must be provided at the generating source of the interrupt.

No hardware priority scheme is provided, neither is any form of interrupt vectoring, as these functions can be provided in software.

A programmed interrupt register is also provided to generate an interrupt under software control. This may typically be used to downgrade a FIQ interrupt to a IRQ interrupt.

|

|

Reference Peripherals Specification |

3-3 |

|

|

ARM DDI 0062D |

|

|

|

|

|

Open Access