TsOS / Analog Devices / 08-интерфейс с DSP

.pdf

a

ПОСЛЕДОВАТЕЛЬНЫЙ ИНТЕРФЕЙС МЕЖДУ ЦАП AD5322 И ПРОЦЕССОРОМ ADSP-2189M

ADSP-2189M

75 МГц AD5322 DAC

SCLK  SCLK

SCLK

TFS  SYNC

SYNC

DT  DIN

DIN

ПОСЛЕДОВАТЕЛЬНЫЙ ПОРТ

Рис. 8.22

ОРГАНИЗАЦИЯ ИНТЕРФЕЙСА МЕЖДУ УСТРОЙСТВАМИ АНАЛОГОВОГО ВВОДА-ВЫВОДА, КОДЕКАМИ

И DSP-ПРОЦЕССОРАМИ

Так как большинство приложений цифровой обработки сигналов требует наличия одновременно АЦП и ЦАП, то широкое развитие получили универсальные устройства, интегрирующие функции кодека и портов ввода-вывода на одном кристалле и обеспечивающие простое подключение к стандартным DSP-процессорам. Эти устройства называют аналоговыми оконечными устройствами (далее по тексту – AFE – Analog Front End).

Функциональная схема микросхемы AD73322 показана на рис. 8.23. Данный прибор представляет собой двойной AFE с двумя 16-разрядными АЦП и двумя 16-разрядными ЦАП с возможностью работы с частотой дискретизации 64 кГц. ИС AD73322 разработана для универсального применения, включая обработку речи и телефонию с использованием сигма-дельта АЦП и сигма-дельта ЦАП. Каждый канал обеспечивает отношение сигнал/шум на уровне 77 дБ в пределах голосовой полосы частот.

Каналы АЦП и ЦАП имеют программируемые коэффициенты усиления по входу и выходу с диапазонами до 38 дБ и 21 дБ соответственно. Встроенный источник опорного напряжения допускает использование однополярного питающего напряжения величиной +2.7-5.5 В. Его потребляемая мощность при напряжении питания +3 В составляет 73 мВт.

21

a |

|

|

|

|

СТРУКТУРНАЯ СХЕМА ИС AD73322 – 16-РАЗРЯДНОГО |

||||

КОДЕКА С ЧАСТОТОЙ ДИСКРЕТИЗАЦИИ 64 КГЦ |

||||

|

С ОДНОПОЛЯРНЫМ ПИТАНИЕМ |

|

||

И ПОСЛЕДОВАТЕЛЬНЫМ ИНТЕРФЕЙСОМ |

||||

|

AVDD1 |

AVDD2 |

DVDD |

|

VFBP1 |

|

|

|

SDI |

VINP1 |

Σ∆ АЦП |

|

|

|

VINN1 |

КАНАЛ 1 |

|

|

SDIFS |

VFBN1 |

|

|

|

|

VOUTP1 |

Σ∆ ЦАП |

|

|

SCLK |

VOUTN1 |

КАНАЛ 1 |

|

|

SE |

|

|

|

||

|

|

|

|

|

REFOUT |

И.О.Н. |

|

ПОСЛЕДО- |

|

|

ВАТЕЛЬНЫЙ |

RESET |

||

REFCAP |

|

|||

|

|

ПОРТ |

|

|

VFBP2 |

|

|

|

|

Σ∆ АЦП |

|

|

MCLK |

|

VINP2 |

|

|

||

VINN2 |

КАНАЛ 2 |

|

|

|

VFBN2 |

|

|

|

|

VOUTP2 |

Σ∆ ЦАП |

|

|

SDOFS |

|

|

|

||

VOUTN2 |

КАНАЛ 2 |

|

|

SDO |

|

|

|

||

|

AGND1 |

AGND2 |

DGND |

|

|

Рис. 8.23 |

|

||

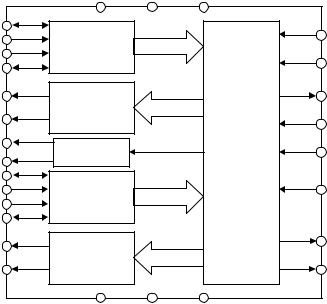

Частота дискретизации кодека может быть запрограммирована на одно из четырех фиксированных значений: 64 кГц, 32 кГц, 16 кГц и 8 кГц при частоте опорного задающего генератора 16.384 МГц. Последовательный порт позволяет легко организовать интерфейс одного или нескольких кодеков, включенных каскадно, со стандартными DSPпроцессорами, имеющимися на рынке, например процессорами семейства ADSP-21XX. Скорость передачи данных по последовательному порту может программироваться, что позволяет осуществлять интерфейс как с быстрыми, так и с медленными DSPпроцессорами. Организация интерфейса кодека с процессором семейством ADSP-218X показана на рис. 8.24. Вывод SE (включение последовательного порта) может управляться от программируемого выхода общего назначения, например FL1, или, в случаях когда не требуется перевод последовательного порта в энергосберегающий режим, на этот вывод может постоянно подаваться высокий уровень через подходящий нагрузочный резистор. Вывод сброса (RESET) может быть соединен с сигналом общего аппаратного сброса системы или может управляться любым программируемым выходом общего назначения.

В режиме программирования данные передаются от DSP-процессора в управляющие регистры микросхемы AD73322 для активации необходимого режима работы. После программирования конфигурации устройства, т.е. после правильной установки различных регистров управления, кодек может выйти из режима программирования и войти в режим передачи данных. Данные от двух АЦП передаются в DSP-процессор двумя блоками, состоящими из 16-ти разрядных слов. Точно так же данные для двух ЦАП передаются от DSP-процессора к микросхеме AD73322 аналогичными способом. Упрощенные временные диаграммы работы последовательного интерфейса показаны на рис. 8.24.

22

a

СХЕМА ИНТЕРФЕЙСА КОДЕКА AD73322 И ПРОЦЕССОРА СЕРИИ ADSP-218x (РЕЖИМ ПЕРЕСЫЛКИ ДАННЫХ)

|

TFS |

|

|

SDIFS |

|

|

ТАКТ.ГЕН. |

|

|

|

|||||||

ADSP-218x |

DT |

|

|

|

SDI |

AD73322 |

16,384 МГц |

|

|

|

|

|

|||||

|

|

|

|

|

CODEC |

|||

DSP SCLK |

|

|

SCLK |

|||||

|

|

|

|

|

||||

DR  SDO

SDO

RFS

SDOFS

SDOFS

FL0  RESET

RESET

FL1  SE

SE

SE

SCLK

SDOFS

SDO |

ОТСЧЕТ АЦП, УСТР-ВО 2 |

ОТСЧЕТ АЦП, УСТР-ВО 1 |

SDIFS

SDI |

ОТСЧЕТ ЦАП, УСТР-ВО 2 |

ОТСЧЕТ ЦАП, УСТР-ВО 1 |

Рис. 8.24

Микросхема AD73422 – это первое изделие в семействе продуктов dspConverter™, которые интегрируют в себе двухканальный кодек (AD73322) и DSP-процессор (52 MIPS ADSP-2185L/86L). Устройство, обладающее полными функциональными возможностями двухканального кодека и DSP-процессора, размещено в небольшом 119-выводном пластмассовом корпусе типа PBGA размером 14×22 мм. Очевидное преимущество такого подхода – экономия площади печатной платы. Используемые АЦП и ЦАП обеспечивают отношение сигнал / шум приблизительно 77 дБ в полосе звуковых частот.

Микросхема AD74222-80 имеет на своем кристалле 80 Кб памяти, сконфигурированной как 16 Кб (24 разряда) ОЗУ программ и 16 Кб (16 разрядов) ОЗУ данных. Встроенное ОЗУ микросхемы AD73422-40 объемом 40 Кб разделено на 8 Кб (24 разряда) памяти программ и 8 Кб (16 разрядов) памяти данных. Режим пониженного энергопотребления обеспечивает низкую потребляемую мощность, необходимую для реализации оборудования с батарейным питанием. Микросхема AD73422 работает при напряжении питания +3 В и рассеивает приблизительно 120 мВт при полнофункциональном режиме работы.

23

a

ОСНОВНЫЕ ОСОБЕННОСТИ ИС

AD73422 dspConverter™

Полный сдвоенный кодек (AD73322) и DSP (ADSP-2185L/86L)

Корпус BGA 14 × 22 мм

Однополярное питание +3 В, потребление 73 мВт Режим пониженного энергопотребления КОДЕК:

Два сигма-дельта-АЦП и ЦАП, 16-разр Частоты дискретизации: 8, 16, 32, и 64 КГц Отношение сигнал/шум 77 dB

DSP:

52 MIPS

Совместим по кодам с ADSP-218x 80 Kб или 40 Kб памяти на кристалле

Рис. 8.25

ОРГАНИЗАЦИЯ ВЫСОКОСКОРОСТНОГО ИНТЕРФЕЙСА

С появлением DSP-процессоров с высокими тактовыми частотами и новыми архитектурными решениями стали возможны анализ и обработка весьма широкополосных сигналов. Программируемость DSP-процессоров делает возможным выполнение различных алгоритмов на тех же самых аппаратных средствах, обеспечивая расширение функциональных возможностей системы. Показанная на рис. 8.26 упрощенная система обеспечивает взаимодействие процессора ADSP-21065L с быстродействующими АЦП и ЦАП посредством использования параллельного интерфейса и внешнего порта DSPпроцессора. Семейство DSP-процессоров SHARC позволяет использовать несколько вариантов взаимодействия АЦП и ЦАП с внешним портом процессора. Данное взаимодействие может быть реализовано с использованием контроллера прямого доступа к памяти (ПДП) DSP-процессора, или программно, с использованием ядра процессора. Использование ПДП не загружает ядро DSP-процессора, что дает возможность ядру продолжать работу (выполнять инструкции программы), в то время как данные читаются и записываются из/во внутреннюю память.

Микросхема AD9201 представляет собой двухканальный 10-разрядный АЦП, работающий с частотой дискретизации 20 МГц, с однополярным питанием в диапазоне от +2.7 В до +5.5 В и рассеиваемой мощностью 215 мВт (при напряжении питания +3В). Параметры прибора AD9201 удовлетворяют требованиям к АЦП, необходимым для многих приложений, например, для реализации высокоскоростных квадратурных каналов телекоммуникационных систем. Наличие входных буферов, внутреннего источника опорного напряжения и мультиплексированных цифровых выходных буферов делает очень простой организацию интерфейса с АЦП AD9201.

ЦАП AD9761 предназначен для совместной работы с АЦП AD9201. Данная микросхема представляет собой двухканальный 10-разрядный ЦАП с частотой дискретизации 20 МГц на канал, работающий от однополярного источника питания с напряжением в диапазоне от +2.7 В до +5.5 В и рассеиваемой мощностью 200 мВт (при напряжении питания +3 В). Встроенный источник опорного напряжения, наличие цифровых буферов и 2-кратная интерполяция делают ЦАП AD9761 весьма полезным при построении передатчиков с квадратурными каналами.

24

a

СХЕМА ИНТЕРФЕЙСА МЕЖДУ АЦП AD9201, ЦАП

AD9761 И ПРОЦЕССОРОМ ADSP-21065L

|

ADSP- |

|

21065L |

|

A0 |

|

D0 - D9 |

|

RD |

|

WR |

СДВОЕННЫЙ |

TCLK |

10-РАЗРЯДНЫЙ |

|

АЦП НА 20 МГЦ |

|

AD9201 |

|

|

|

|

|

|

|

|

|

|

|

AD9761 |

|

ADC |

|

|

|

|

|

DAC |

D0 - D9 |

|

|

|

|

|

D0 - D9 |

CLOCK |

|

|

|

|

|

CLOCK |

|

|

|

|

|

|

|

SELECT |

|

|

|

|

|

SELECT |

|

|

|

|

|||

CHIP-SELECT |

|

|

|

|

|

WRITE |

|

|

|

|

|

||

|

|

|

|

|

||

|

|

|

|

|

|

|

СДВОЕННЫЙ 10-РАЗРЯДНЫЙ ЦАП НА 20 МГЦ

Рис. 8.26

СИСТЕМНЫЙ ИНТЕРФЕЙС ПРОЦЕССОРА DSP

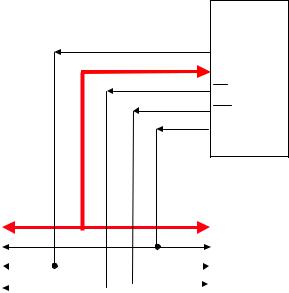

На рис. 8.26 показана упрощенная система на базе процессора ADSP-2189M, использующая полномасштабную модель памяти. Она включает два устройства, работающие через последовательные интерфейсы, 8-разрядную EPROM, внешнюю оверлейную память программ и данных. Возможность программной генерации циклов ожидания позволяет легко подключать быстрый процессор к более медленным периферийным устройствам. Процессор ADSP-2189M также поддерживает четыре внешних прерывания, семь универсальных сигналов ввода-вывода и два последовательных порта. Один из последовательных портов может быть сконфигурирован как источник двух дополнительных сигналов прерывания, один универсальный вход и один универсальный сигнал вывода, что даст в сумме шесть внешних сигналов прерывания, девять каналов ввода-вывода общего назначения при сохранении одного полнофункционального последовательного порта. Процессор ADSP-2189M может также работать в режиме доступа к хост-памяти (host memory mode), который позволяет организовать доступ по всей ширине внешней шины данных, но ограничивает адресацию одним адресным битом. Дополнительные периферийные устройства могут быть подключены в режиме host memory mode при использованием внешних аппаратных средств для генерации и фиксации дополнительных адресных сигналов.

25

a |

|

|

|

|

|

|

|

|

ПРИМЕР СИСТЕМЫ НА БАЗЕ ADSP-2189M. |

||||||||

ПОЛНОМАСШТАБНАЯ МОДЕЛЬ ПАМЯТИ |

||||||||

|

|

ADSP-2189M |

14 |

14 |

22 |

|

|

|

1/2 X CLOCK |

|

CLKIN |

ADDR |

|

|

|||

|

|

|

|

|

||||

|

|

8 |

|

|

|

|||

OR |

|

|

|

|

|

ADDR |

BYTE |

|

CRYSTAL |

|

XTAL |

|

24 |

|

|

|

|

|

|

8 |

|

|

MEMORY |

|||

|

4 |

|

DATA |

|

DATA |

|||

INTERRUPTS |

IRQ x |

|

|

|

|

|||

|

BMS |

|

|

|

CS |

|

||

|

|

|

|

|

|

|

||

GENERAL |

7 |

MODE x |

WR |

|

|

11 |

|

|

PURPOSE IO |

|

|

|

|

I/O SPACE |

|||

|

|

|

|

ADDR |

||||

|

|

|

RD |

|

16 |

|

(PERIPHERALS) |

|

|

|

|

|

|

|

|

DATA |

|

УСТРОЙСТВО |

5 |

SPORT1 |

IOMS |

|

|

|

CS |

2048 LOCATIONS |

С ПОСЛЕДОВА- |

|

|

|

|

|

|||

ТЕЛЬНЫМ |

|

|

|

|

14 |

|

|

|

ИНТЕРФЕЙСОМ |

|

|

|

|

ADDR |

OVERLAY |

||

|

|

|

|

|

24 |

|

||

|

|

|

|

|

|

DATA |

MEMORY |

|

УСТРОЙСТВО |

|

|

|

|

|

|

|

|

5 |

SPORT0 |

PMS |

|

|

|

|

|

|

С ПОСЛЕДОВА- |

|

DMS |

|

|

|

TWO 8K PM SEGMENTS |

||

|

|

|

|

|

||||

ТЕЛЬНЫМ |

|

|

|

|

|

TWO 8K DM SEGMENTS |

||

|

|

CMS |

|

|

|

|||

ИНТЕРФЕЙСОМ |

|

|

|

|

|

|||

|

|

|

|

|

|

|

||

|

|

|

BR |

|

BUS REQUEST/ |

|

|

|

|

|

|

BG |

|

|

|

|

|

|

|

|

|

GRANT/HUNG |

|

|

|

|

|

|

|

BGH |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PWD |

|

POWER DOWN INPUT |

|

|

|

|

|

|

PWDACK |

|

POWER DOWN OUTPUT |

|

|

|

|

|

|

|

Рис. 8.27 |

|

|

|

|

26

a

СПИСОК ЛИТЕРАТУРЫ

1.Steven W. Smith, The Scientist and Engineer’s Guide to Digital Signal Processing, Second Edition, 1999, California Technical Publishing,

P.O. Box 502407, San Diego, CA 92150. Also available for free download at: http://www.dspguide.com or http://www.analog.com

2.C. Britton Rorabaugh, DSP Primer, McGraw-Hill, 1999.

3.Richard J. Higgins, Digital Signal Processing in VLSI, Prentice-Hall, 1990.

27