TsOS / Analog Devices / 08-интерфейс с DSP

.pdfa

активное состояние сигнал выбора памяти DMS (шаг N 3). Это приводит к тому, что дешифратор адреса выдает сигнал выбора (chip select) на периферийное устройство (шаг N 5). После спадающего (переднего) фронта сигнала DMS через промежуток времени tASW процессор переводит в активное нулевое состояние сигнал записи WR (шаг N 4). Длительность импульса WR составляет tWP нс. Данные помещаются на шину данных (D) и удерживаются в течение времени tDW, до перехода сигнала WR в неактивное единичное состояние (шаг N 6). Восходящий (задний) фронт сигнала WR используется для фиксации присутствующих на шине данных (D) во внешнюю параллельную память (шаг N 7). Данные на шине остаются достоверными еще в течение времени tDH после прохождения положительного фронта сигнала WR.

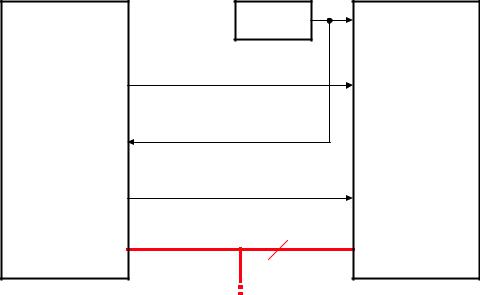

Основные требования по временным параметрам при записи данных в периферийное устройство показаны на рис. 8.10. Главным параметром здесь является длительность строба записи tWP. Для всех периферийных устройств, кроме самых быстрых, придется использовать циклы ожидания, т.к. этим устройствам нужно больше времени для доступа к данным. На рис. 8.11 приведены основные временные характеристики цикла записи процессора ADSP-2189M. Обратите внимание на то, что все они зависят от тактовой частоты процессора.

ОСНОВНЫЕ ТРЕБОВАНИЯ ПРИ ЗАПИСИ В ПЕРИФЕРИЙНОЕ УСТРОЙСТВО (ПУ) ЧЕРЕЗ ПАРАЛЛЕЛЬНЫЙ ИНТЕРФЕЙС

Время декодирования адреса и время включения периферийного устройства не должно превышать время tASW установки процессором адреса и сигнала выбора памяти (0.325 нс минимум для процессора ADSP-2189M)

Для того, чтобы осуществить доступ без режима ожидания, время установления данных не должно превышать tDW (составляет 2.65 нс для процессора ADSP-2189M при работе на частоте 75 МГц), иначе необходимо программно обеспечить режим ожидания или снизить частоту работы процессора

Время удержания входных данных не должно превышать tDH (составляет 2.325 нс для процессора ADSP-2189M при работе на частоте 75 МГц)

Периферийное устройство должно работать при длительности строба WR составляющей tWP (3.65 нс мин. для процессора ADSP-2189M при работе на частоте 75 МГц), иначе необходимо программно обеспечить режим ожидания или снизить частоту работы процессора

Рис. 8.10

11

a

ВРЕМЕННЫЕ ХАРАКТЕРИСТИКИ ПРОЦЕССА ПАРАЛЛЕЛЬНОЙ ЗАПИСИ ДЛЯ ПРОЦЕССОРА ADSP-2189M ПРИ РАБОТЕ НА ЧАСТОТЕ 75 МГЦ

tCK = период тактового сигнала процессора (13.3 нс)

= время установки процессором адреса и сигнала выбора памяти до спадающего (переднего) фронта сигнала записи =

0.25·tCK – 3 нс (минимум)

tDW = время от момента установки данных до восходящего (заднего) фронта сигнала записи = 0.5·tCK – 4 нс + (число циклов ожидания) × tCK

tDH = время удержания данных после восходящего (заднего) фронта сигнала записи = 0.25·tCK – 1 нс

tWP = длительность импульса сигнала записи WR = 0.5·tCK – 3 нс + (число циклов ожидания) × tCK (минимум)

Рис. 8.11

Микросхема AD5340 – это 12-ти разрядный ЦАП, работающий на частоте дискретизации 100 кГц, имеющий параллельный цифровой интерфейс. Данный АЦП питается от однополярного источника питания напряжением +2.5-5.5 В и рассеивает мощность 345 мкВт (при напряжении питания 3 В). В энергосберегающем режиме потребляемая

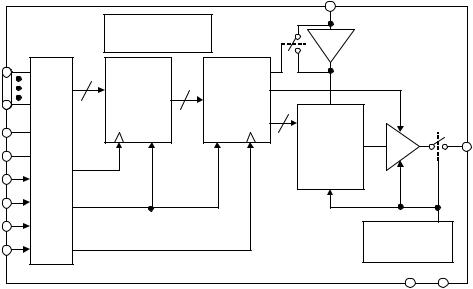

мощность прибора снижается до 0.24 мкВт. ЦАП AD5340 имеет в своем составе выходной буферный усилитель, который способен формировать выходной сигнал в диапазоне значений от нуля до напряжения питания. В ИС AD5340 можно задействовать или отключить встроенный буфер для источника опорного напряжения. В устройстве имеется встроенная схема формирования сигнала сброса при включении питания, гарантирующая нулевое значение сигнала на выходе ЦАП до тех пор, пока в ЦАП не будут записаны корректные данные. Структурная схема ЦАП показана на рис. 8.12. На входе прибора осуществляется двойная буферизация данных. Основные временные характеристики интерфейса между двумя устройствами (ЦАП и DSP) приведены на рис. 8.13. Спецификация временных параметров цикла записи для ADSP-2189M дается для тактовой частоты 75 МГц.

12

a

12-РАЗРЯДНЫЙ ЦАП AD5340 С ЧАСТОТОЙ ПРЕОБРАЗОВАНИЯ 100 КГЦ И ПАРАЛЛЕЛЬНЫМ ВХОДОМ

VREF

|

СХЕМА СБРОСА |

|

|

|

|

ПРИ ВКЛЮЧЕНИИ |

|

AD5340 |

|

|

ПИТАНИЯ |

|

||

|

|

|

|

|

DB11 |

|

|

|

|

DB0 |

ВХОДНОЙ |

РЕГИСТР |

|

|

РЕГИСТР |

ЦАП |

|

|

|

BUF |

ИНТЕРФЕЙС |

ЦАП |

|

|

GAIN |

12 |

БУФ. |

VOUT |

|

РАЗРЯДОВ |

|

|

||

CS |

|

|

|

|

|

|

|

|

|

WR |

СБРОС |

|

|

|

CLR |

|

|

КОНТРОЛЬ |

|

LDAC |

|

|

НАПРЯЖЕНИЯ |

|

|

|

ПИТАНИЯ |

||

|

|

|

||

|

|

|

PD |

GND |

|

Рис. 8.12 |

|

|

|

|

ВРЕМЕННЫЕ ХАРАКТЕРИСТИКИ |

|

||

|

ПАРАЛЛЕЛЬНЫХ ИНТЕРФЕЙСОВ |

|

||

|

ПРОЦЕССОРА ADSP-2189M И ЦАП AD5340 |

|||

Процессор ADSP-2189M (75 МГц) |

ЦАП AD5340 |

|||

|

|

|

|

|

|

tASW (время установки |

t1 (время установки от сигнала CS |

||

|

процессором адреса и сигнала |

|||

|

выбора памяти до переднего |

до WR) = 0 нс мин. |

||

|

фронта WR) = 0.325 нс мин. |

|

|

|

tWP = (длительность импульса WR) |

t3 = (длительность импульса WR) |

|||

|

= 3.65 нс + (число циклов |

= 20 нс мин. |

||

ожидания) × 13.3 нс = 30.25 нс мин. |

|

|

||

|

|

|

|

|

tDW = (время от установки данных |

t4 = (время от установки данных до |

|||

до заднего фронта WR) = 2.65 нс + |

установки сигнала WR) |

|||

(число циклов ожидания) × 13.3 нс |

||||

= 5 нс мин. |

||||

|

= 29.25 нс мин. |

|||

|

|

|

||

tDH (время удержания данных после |

t5 (время удержания данных до |

|||

заднего фронта WR) = 2.325 нс мин |

сигнала WR) = 4.5 нс мин. |

|||

|

|

|

|

|

Примечание:

Добавление 2 циклов ожидания в процессоре ADSP-2189M увеличит время tWP до 30.25 нс и время tDW до 29.25 нс, что превышает величины t3 (20 нс) и t4

(5 нс) соответственно.

Рис. 8.13

13

a

Исследование временных характеристик, изображенных на рис. 8.13, показывает, что для обеспечения совместимости по синхронизации между устройствами потребуется программирование двух циклов ожидания в процессоре ADSP-2189M. Это позволяет увеличить длительность строба записи (WR) до 30.25 нс, что превышает минимально необходимую длительность строба записи в ЦАП AD5340 (20 нс). Минимальное время установления данных в микросхеме AD5340, равное 5 нс, также перекрывается при использовании двух циклов ожидания. Упрощенная схема интерфейса между двумя устройствами показана на рис. 8.14.

Параллельные интерфейсы с другими DSP-процессорами могут быть организованы подобным образом, для чего необходимо подробное изучение временных спецификаций всех соответствующих сигналов каждого из взаимодействующих устройств.

ПАРАЛЛЕЛЬНЫЙ ИНТЕРФЕЙС МЕЖДУ |

||

ЦАП AD5340 И ADSP-2189M |

||

|

ТАКТОВЫЙ |

LDAC |

|

ГЕНЕРАТОР |

|

|

AD5340 |

|

ADSP-2189M |

|

|

75MHz |

|

DAC |

DMS |

|

CS |

IRQ |

|

|

WR |

|

WR |

D |

|

DB0 - DB11 |

Примечания: Используется 2 программных цикла ожидания |

||

|

Тактовые импульсы можно получать от процессора DSP |

|

Рис. 8.14

ОРГАНИЗАЦИЯ ПОСЛЕДОВАТЕЛЬНОГО ИНТЕРФЕЙСА С DSP- ПРОЦЕССОРАМИ

DSP-процессоры, имеющие последовательные порты (например, семейство ADSP-21XX), позволяют организовать простой интерфейс с такими периферийными устройствами, как АЦП и ЦАП. Наличие последовательного порта устраняет необходимость использования больших параллельных шин для подключения АЦП и ЦАП к DSP-процессорам. Чтобы уяснить принцип последовательной передачи данных, мы рассмотрим сначала работу последовательного порта процессоров семейства ADSP-21XX.

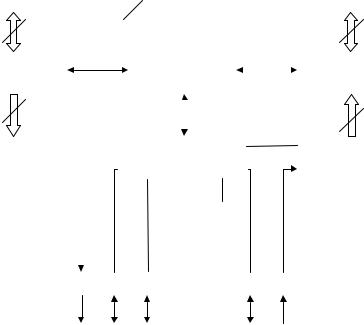

Структурная схема одного из двух последовательных портов процессора семейства ADSP21XX показана на рис. 8.15. Передающий (TX) и принимающий (RX) регистры последовательного порта определены на уровне синтаксиса языка ассемблера процессоров семейства ADSP-21XX и не отображаются в памяти процессора.

14

a

СТРУКТУРНАЯ СХЕМА ПОСЛЕДОВАТЕЛЬНОГО ПОРТА ПРОЦЕССОРОВ СЕМЕЙСТВА ADSP-21xx

|

|

|

|

|

|

ШИНА ДАННЫХ ПАМЯТИ ДАННЫХ (DMD) |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

16 |

|

|

16 |

|

|

|

|

|

16 |

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TXn |

|

|

|

|

|

СХЕМА |

|

|

|

RXn |

|||||

|

РЕГИСТР ДАННЫХ |

|

|

|

|

КОМПАНДЕРА |

|

|

|

|

|

РЕГИСТР ДАННЫХ |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

ДЛЯ ПЕРЕДАЧИ |

|

|

|

|

|

µ ИЛИ A |

|

|

|

|

|

ДЛЯ ПРИЕМА |

|

|

|

|

16 |

|

|

|

|

|

|

|

|

|

|

16 |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

СДВИГОВЫЙ |

|

|

|

ПОСЛЕДОВАТЕЛЬНОЕ |

|

|

|

СДВИГОВЫЙ |

|

|

|||||

|

|

|

|

|

|

|

|

|

||||||||

|

РЕГИСТР |

|

|

|

|

|

|

РЕГИСТР |

|

|

||||||

|

|

|

|

|

УПРАВЛЕНИЕ |

|

|

|

|

|

|

|||||

|

ДЛЯ ПЕРЕДАЧИ |

|

|

|

|

|

|

|

|

ДЛЯ ПРИЕМА |

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Полярность импульсов |

|||

|

|

|

|

|

|

|

ВНУТРЕННИЙ |

|

|

|

|

|||||

|

|

|

|

|

|

|

ГЕНЕРАТОР |

|

|

|

|

TFS и RFS можно |

||||

|

|

|

|

|

|

|

ТАКТОВЫХ |

|

|

|

|

устанавливать |

||||

|

|

|

|

|

|

|

ИМПУЛЬСОВ |

|

|

|

|

программно |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DT |

TFS SCLK |

RFS |

DR |

|||||||||||

Рис. 8.15

ОСОБЕННОСТИ РАБОТЫ ПОСЛЕДОВАТЕЛЬНОГО ПОРТА В ПРОЦЕССОРАХ СЕМЕЙСТВА ADSP-21xx

Отдельные секции приема и передачи данных для каждого порта Двойная буферизация регистров приема и передачи данных

Тактовые импульсы для последовательного обмена могут генерироваться как внутри процессора, так и поступать извне Сигналы синхронизации фреймов могут быть внутренними или внешними Длина передаваемых слов может составлять от 3 до 16 бит

Автоматическая генерация прерываний Аппаратный компандер освобождает ресурс ядра процессора

Рис. 8.16

В приемной части последовательного порта сигнал фреймовой синхронизации приема (RFS) инициирует прием данных. Последовательный поток принимаемых данных (DR) от внешнего устройства (АЦП), побитно направляется в приемный регистр сдвига. Для битовой синхронизации используются спадающие фронты тактовых импульсов сигнала SCLK. После завершения приема очередного слова, оно записывается в регистр приема данных (RX), и последовательный порт генерирует запрос прерывания, по которому ядро процессора имеет возможность прочитать принятое слово из регистра (RX).

15

a

Запись в регистр передачи данных (TX) подготавливает последовательный порт к передаче данных. Начало передачи данных сопровождается сигналом фреймовой синхронизации передачи (TFS). Затем слово из регистра передачи данных (TX)

записываются во внутренний передающий регистр сдвига. Данные из передающего регистра сдвига побитно посылаются на периферийное устройство (ЦАП). Для синхронизации последовательно передаваемых на внешнее устройство данных (DT) используются положительные фронты импульсов тактового сигнала SCLK. После передачи первого бита последовательный порт генерирует запрос прерывания, по которому ядро процессора может записать в регистр передачи данных новое слово, несмотря на то, что передача предыдущих данных еще не завершена.

При нормальном режиме фреймовой синхронизации сигнал фреймовой синхронизации (RFS или TFS) проверяется по нисходящему фронту тактового сигнала SCLK. Если в этот момент сигнал фреймовой синхронизации активен, то данные доступны (в режиме передачи) или данные фиксируются в приемном регистре сдвига (в режиме приема) по нисходящему фронту следующего тактового импульса сигнала SCLK. Сигнал фреймовой синхронизации не проверяется далее до окончания передачи или приема всего оставшегося слова. При альтернативном режиме фреймовой синхронизации сигнал фреймовой синхронизации устанавливается в том же самом такте сигнала SCLK, что и первый бит слова. Биты данных фиксируются по нисходящему фронту сигнала SCLK, но сигнал фреймовой синхронизации проверяется только в такте, соответствующем первому биту. Генерированный внутри сигнал фреймовой синхронизации остается в активном состоянии на все время приема или передачи последовательного слова. Альтернативный режим фреймовой синхронизации последовательного порта в процессорах семейства ADSP-21XX обычно используется для приема данных от АЦП или передачи данных на ЦАП.

Последовательные порты процессоров семейства ADSP-21XX чрезвычайно универсальны. Сигналы TFS, RFS или SCLK могут либо генерироваться встроенным генератором процессора семейства ADSP-21XX (режим master), либо поступать от внешнего источника (режим slave). Полярность этих сигналов может быть изменена программно, еще более повышая таким образом гибкость интерфейса. Порт также содержит аппаратные средства компандирования с µ- и A-характеристикой для голосовых телекоммуникационных приложений.

ОРГАНИЗАЦИЯ ПОСЛЕДОВАТЕЛЬНОГО ИНТЕРФЕЙСА МЕЖДУ DSP- ПРОЦЕССОРОМ И АЦП

Временные диаграммы работы последовательного порта процессора ADSP-2189M, работающего в режиме приема (альтернативный режим фреймовой синхронизации), показаны на рис. 8.17. Первый отрицательный (нисходящий) фронт сигнала SCLK, следующий после отрицательного (нисходящего) фронта сигнала RFS, синхронизирует фиксацию старшего бита данных (MSB) от АЦП во входном регистре сдвига процессора. Процесс продолжается до тех пор, пока все последовательные биты не будут поочередно приняты во входном регистре сдвига. Основные временные характеристики, на которые следует обратить внимание, это время установления последовательных данных (tSCS) и время их удержания (tSCH) по отношению к отрицательным фронтам сигнала SCLK. В случае использования процессора ADSP-2189M, эти значения равны соответственно 4 и 7 нс. При использовании АЦП последнего поколения, оснащенных высокоскоростными последовательными портами, обычно не возникает трудностей в обеспечении этих характеристик даже при максимальной скорости последовательной передачи данных.

16

a

ВРЕМЕННАЯ ДИАГРАММА РАБОТЫ ПОСЛЕДОВАТЕЛЬНОГО ПОРТА ПРОЦЕССОРА ADSP-2189M

ADC

SCLK

RFS IN

tSCS |

|

|

|

t |

SCH |

t |

SCS |

|

|||||||

≥ 4 нс |

|

|

|

|

|

||

|

|

|

|

≥ 7 нс |

|

|

|

DR IN |

MSB |

BIT n |

LSB |

РЕЖИМ ЧЕРЕДОВАНИЯ ФРЕЙМОВ, АЦП ЯВЛЯЕТСЯ ВЕДУЩИМ УСТРОЙСТВОМ (MASTER)

Рис. 8.17

Микросхемы AD7853/AD7853L – это 12-ти разрядные АЦП, поддерживающие частоты дискретизации 100/200 кГц и работающие от однополярного источника питания напряжением от +3 В до + 5.5 В с потреблением всего 4.5 мВт (AD7853L при напряжении питания +3 В). После каждого преобразования устройство автоматически переходит в режим пониженного энергопотребления и потребляемая мощность снижается до 25 мкВт. В микросхеме AD7853/AD7853L применяется схема последовательного приближения и используется ЦАП с перераспределением зарядов (ЦАП на переключаемых конденсаторах). Наличие режима калибровки позволяет устранить погрешность смещения и скомпенсировать погрешности усиления. Структурная схема устройства показана на рис. 8.18.

Микросхема AD7853 может работать при частоте внешнего тактового генератора до

4 МГц. Для AD7853L максимальная частота ограничена значением 1.8 МГц. Временные диаграммы для AD7853L показаны на рис. 8.19. В микросхемах AD7853/AD7853L можно конфигурировать выводы SYNC и SCLK как входы или выходы. В показанном примере генерация этих сигналов осуществляется микросхемой AD7853L. Задающий генератор сигнала синхронизации последовательного порта AD7853L работает на максимальной частоте 1.8 МГц (период 556 нс). Биты данных достоверны в течение 330 нс после появления положительных фронтов сигнала SCLK. Это позволяет получить как минимум около 330 нс для установления данных до спадающего фронта сигнала SCLK, что удовлетворяет требованию на минимальную величину tSCS в 4 нс для процессора ADSP2189M. Время удержания данных после спадающего фронта сигнала SCLK составляет приблизительно 226 нс, что тоже полностью удовлетворяет временным требованиям на величину tSCH в 7 нс для процессора ADSP-2189M. Эти простые вычисления показывают, что требования, предъявляемые спецификацией процессора ADSP-2189M ко времени установления данных и сигнала RFS, а также ко времени их удержания, выполнены со значительным запасом.

17

a |

|

|

|

|

|

12-РАЗРЯДНЫЙ АЦП AD7853/AD7853L |

|

||||

С ЕДИНСТВЕННЫМ НАПРЯЖЕНИЕМ ПИТАНИЯ |

|||||

+3 В, С ЧАСТОТОЙ ДИСКРЕТИЗАЦИИ 200/100 КГЦ |

|||||

И ПОСЛЕДОВАТЕЛЬНЫМ ВЫХОДОМ |

|

||||

AIN(+) |

|

AVDD |

|

AGND AGND |

|

|

|

|

AD7853L |

DVDD |

|

T/H |

|

|

|

||

AIN(–) |

ИСТОЧНИК ОПОРНОГО |

|

|

||

|

|

DGND |

|||

|

НАПРЯЖЕНИЯ 2.5 V |

COMP |

|||

REFIN / |

|

|

|

|

|

BUF |

|

|

|

|

|

REFOUT |

|

|

|

|

|

CREF1 |

|

CHARGE |

РЕГИСТР ПОСЛЕДОВ. |

CLKIN |

|

|

REDISTRIBUTION |

|

|||

|

ПРИБЛИЖЕНИЯ |

|

|||

|

|

DAC |

|

CONVST |

|

CREF2 |

|

|

И УПРАВЛЕНИЕ |

||

|

|

|

|

||

|

|

|

ПРЕОБРАЗОВАТЕЛЕМ |

BUSY |

|

|

|

|

|

|

|

CAL |

|

ПАМЯТЬ |

|

SLEEP |

|

|

ДЛЯ КАЛИБРОВКИ |

|

|||

|

|

И КОНТРОЛЛЕР |

|

|

|

ПОСЛЕДОВАТЕЛЬНЫЙ ИНТЕРФЕЙС И УПРАВЛЯЮЩИЙ РЕГИСТР |

|

||||

SM1 |

SM2 |

SYNC |

DIN |

DOUT SCLK POLARITY |

|

Рис. 8.18

ВРЕМЕННАЯ ДИАГРАММА ЗАПИСИ В ПАМЯТЬ В ПРОЦЕССОРАХ СЕМЕЙСТВА ADSP-21XX

SYNC (O/P)

SCLK |

1 |

5 |

6 |

16 |

(O/P) |

|

|

||

|

|

|

|

ВЫСОКО- |

|

330 нс min |

|

|

|

|

|

|

|

ИМПЕДАНСНОЕ |

|

|

|

|

СОСТОЯНИЕ |

DB15 |

DB11 |

DB0 |

ВЫСОКО- |

DOUT (O/P) |

|

|

|

|

|

|

|

ИМПЕДАНСНОЕ |

|

|

|

|

|

СОСТОЯНИЕ |

556 нс

556 нс

226 нс

226 нс

Рис. 8.19

На рис. 8.20 показана система, состоящая из АЦП AD7853L и процессора ADSP-2189M, функционирующая в режиме передачи данных от АЦП к DSP (альтернативный режим фреймовой синхронизации, АЦП работает в режиме "мастер"). В ИС AD7853/AD7853L имеются внутренние регистры, которые доступны для записи со стороны DSP-процессора через последовательный порт. Эти регистры используются для установки различных режимов работы АЦП AD7853/AD7853L, а также для инициализации процесса

18

a

калибровки. Используемые для этого сигналы не показаны на приведенной ниже диаграмме.

ПОСЛЕДОВАТЕЛЬНЫЙ ИНТЕРФЕЙС МЕЖДУ АЦП AD7853/AD7853L И ADSP-2189M

|

|

|

ТАКТОВЫЙ |

|

|

CLKIN |

ADSP-2189M |

|

|

ГЕНЕРАТОР |

|

|

|

|

|

|

|

|||

|

|

|

|

|

||

75 МГц |

|

|

4МГц / 1,8МГц max |

|

|

|

|

|

|

|

|

|

|

DSP |

|

|

ГЕНЕРАТОР |

|

|

|

|

|

|

ИМПУЛЬСОВ |

|

CONVST |

|

|

|

|

ПРЕОБРАЗОВАНИЯ |

|

||

|

|

|

|

|

||

|

|

|

(НЕОБЯЗАТЕЛЬНО) |

|

|

|

SCLK |

|

|

|

|

|

SCLK |

|

|

|

|

|

||

|

|

|

|

|

||

RFS |

|

|

|

|

|

SYNC |

|

|

|

|

|

||

DR |

|

|

|

|

|

DOUT |

|

|

|

|

|

||

ПОСЛЕДО- |

|

|

|

|

|

|

ВАТЕЛЬНЫЙ |

|

|

|

|

|

|

ПОРТ |

|

|

|

|

|

|

|

|

|

|

|

|

|

AD7853/

AD7853L

ADC

Рис. 8.20

ОРГАНИЗАЦИЯ ПОСЛЕДОВАТЕЛЬНОГО ИНТЕРФЕЙСА МЕЖДУ DSP- ПРОЦЕССОРОМ И ЦАП

Организация интерфейса между последовательными портами ЦАП и процессора семейства ADSP-21xx также относительно проста и подобна рассмотренной выше реализации взаимодействия между АЦП и процессором. Далее мы не будем заново рассматривать детали, но покажем простой пример организации интерфейса.

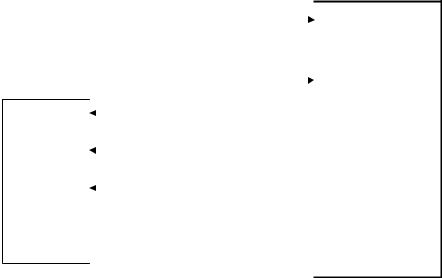

Микросхема AD5322 представляет собой 12-разрядный сдвоенный ЦАП с частотой дискретизации 100 кГц, оснащенный последовательным входным интерфейсом. Прибор работает от однополярного источника питания с напряжением +2.5-5.5 В; структурная схема устройства показана на рис. 8.21. Потребляемая мощность микросхемы при напряжении питания +3 В составляет 690 мкВт. В режиме пониженного энергопотребления потребляемая мощность снижается до 0.15 мкВт. Уровень гармонических искажений выходного сигнала не превышает -70 дБ относительно полной шкалы на частоте 10 кГц. Опорное напряжение для каждого ЦАП подается независимо через соответствующие выводы микросхемы (по одному на каждый ЦАП). Внешнее опорное напряжение может подаваться как через внутренние буферы, имеющиеся на соответствующих входах, так и напрямую. Выходы обоих ЦАП могут одновременно обновляться с помощью асинхронного сигнала LDAC. Устройство имеет встроенную схему формирования сигнала сброса по включению питания, гарантирующую нулевое значение сигнала на выходе ЦАП до тех пор, пока в ЦАП не будут записаны корректные данные.

19

a |

|

|

|

|

|

СТРУКТУРНАЯ СХЕМА 12-РАЗРЯДНОГО ЦАП AD5322 |

|||||

|

СО СКОРОСТЬЮ ПРЕОБРАЗОВАНИЯ 100 КГЦ |

||||

|

СХЕМА |

VDD |

|

VREFA |

|

|

СБРОСА ПРИ |

|

|

|

AD5322 |

|

ВКЛЮЧЕНИИ |

|

|

|

|

|

|

ВХОДНОЙ |

РЕГИСТР |

STRING |

|

|

|

РЕГИСТР |

ЦАП |

|

|

|

|

DAC A |

|

||

|

|

A |

A |

VOUTA |

|

SYNC |

|

|

|||

|

|

|

|

|

|

|

БЛОК ИНТЕРФЕЙСА |

|

|

|

РЕЗИСТОРНАЯ |

|

|

|

СХЕМА |

ЦЕПЬ |

|

|

|

|

УПРАВЛЕНИЯ |

|

|

SCLK |

|

|

ЭНЕРГО- |

|

|

|

|

|

ПОТРЕБЛЕНИЕМ |

|

|

DIN |

|

РЕГИСТР |

|

|

|

|

ВХОДНОЙ |

STRING |

|

||

|

|

|

|||

|

|

РЕГИСТР |

ЦАП |

DAC B |

VOUTB |

|

|

B |

B |

|

|

|

|

|

|

|

РЕЗИСТОРНАЯ |

|

|

|

|

|

ЦЕПЬ |

|

LDAC |

|

GND |

VREFB |

|

|

|

|

Рис. 8.21 |

|

|

Данные обычно передаются в AD5322 посредством использования входов SCLK, DIN и SYNC из последовательного порта DSP-процессора. Когда сигнал SYNC переходит в активное нулевое состояние, разрешается ввод данных в приемный регистр сдвига ЦАП. Данные фиксируются в приемном регистре сдвига микросхемы AD5322 по спадающим фронтам следующих 16 импульсов сигнала SCLK. Организация стандартного интерфейса между процессором ADSP-2189M и ЦАП AD5322 показана на рис. 8.22. Нужно заметить, что сигнал синхронизации для AD5322 задается генератором тактового сигнала процессора ADSP-2189M. Также существует возможность внешней по отношению к AD5322 генерации сигналов SCLK и SYNC и их использования для синхронизации процессора ADSP-2189M. Последовательный интерфейс AD5322 недостаточно быстр для работы с ADSP-2189M на максимальной скорости, которую может обеспечить процессор. Однако частота сигнала синхронизации последовательного порта процессора может быть запрограммирована на соответствующую скорость, поддерживаемую быстрыми или медленными ЦАП.

Входной регистр сдвига в микросхеме AD5322 имеет разрядность 16 бит. 16-разрядное слово состоит из четырех битов управления, за которыми следуют 12 бит данных для ЦАП. Первый посылаемый бит определяет, для какого из двух имеющихся ЦАП (А или B) предназначены данные. Второй бит определяет использование буферизированного или небуферизированного режима работы входа опорного напряжения. Следующие два бита управляют режимами работы ЦАП (нормальный режим, режим пониженного энергопотребления с заземлением выходов через 1 кОм или через 100 кОм, режим пониженного энергопотребления с высокоимпедансным выходом).

20