TsOS / Analog Devices / 03-АЦП

.pdfa

ГЛАВА 3

АНАЛОГО-ЦИФРОВЫЕ ПРЕОБРАЗОВАТЕЛИ ДЛЯ ЗАДАЧ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ

АЦП последовательного приближения

Сигма-дельта АЦП

Параллельные (Flash) АЦП

Конвейерные (Pipelined) АЦП

АЦП последовательного счета (Bit-Per-Stage)

1

a

ГЛАВА 3

АНАЛОГО-ЦИФРОВЫЕ ПРЕОБРАЗОВАТЕЛИ ДЛЯ ЗАДАЧ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ

Уолт Кестер, Джеймс Брайэнт

Современная тенденция развития АЦП и ЦАП состоит в увеличении скоростей и разрешающих способностей обработки сигналов при уменьшении уровня потребляемой мощности и напряжения питания. Современные преобразователи данных в основном работают на напряжениях питания ±5V (двуполярный источник питания), +5V или +3V (однополярный источник питания). В действительности, число устройств с напряжением питания +3V быстро увеличивается вследствие появления для них большого числа новых рынков сбыта, таких как цифровые камеры, видеокамеры и телефоны сотовой связи. Эта тенденция создала множество проектных и конструкторских проблем, которым не придавалось значения в разработках более ранних преобразователей, использовавших стандартное напряжение питания ±15V и диапазон изменения входных сигналов ±10V.

Более низкие напряжения питания подразумевают меньшие диапазоны входных напряжений и, следовательно, большую чувствительность к разного вида помехам: шумам от источников питания, некачественным опорным и цифровым сигналам, электромагнитным воздействиям и радиопомехам (EMI/RFI) и, возможно наиболее важный момент — к некачественным методам развязки, заземления и размещения компонентов на печатной плате. В АЦП с однополярным источником питания диапазон изменения входных сигналов обычно отсчитывается вне связи с «землей». При этом проблема заключается в поиске совместимых усилителей с однополярным питанием для нормализации сигнала на входе АЦП и в осуществлении необходимого сдвига входного сигнала относительно «земли» в приложениях с непосредственной связью.

Несмотря на эти проблемы, в настоящее время доступны компоненты, которые обладают чрезвычайно высокими разрешающими способностями при низких напряжениях питания и малой потребляемой мощности. Этот раздел посвящен обсуждению проблемы создания приложений на базе таких компонентов и описанию методов успешного проектирования таких систем.

Наиболее популярные АЦП для приложений цифровой обработки сигналов (ЦОС) базируются на пяти основных архитектурах: АЦП последовательного приближения, сигма-дельта АЦП, АЦП параллельной обработки (flash), АЦП конвейерной обработки

(pipelined) и АЦП последовательного счета (Bit-Per-Stage).

2

a

ОСОБЕННОСТИ АЦП С НИЗКИМ НАПРЯЖЕНИЕМ ПИТАНИЯ И МАЛЫМ ЭНЕРГОПОТРЕБЛЕНИЕМ

Типичные напряжения питания: ±5 В, +5 В, +5/+3 В, +3 В Из-за малой амплитуды сигнала устройство чувствительно

ко всем типам шумов (собственные шумы устройства, источника питания, логики и т.п.)

Шумы устройства увеличиваются вследствие малых токов Ограничения по величине синфазного входного напряжения Критичен выбор входного буферного усилителя При высокой разрешающей способности желателен режим автокалибровки

Рис. 3.1

АЦП ДЛЯ ЦИФРОВЫХ СИГНАЛЬНЫХ ПРОЦЕССОРОВ

Последовательного приближения: Разрешение до 16 бит

Минимальное время задержки, может работать в режиме однократного преобразования Используются в мультиплексированных системах сбора данных

Сигма-Дельта (Σ∆): Разрешение до 24 бит

Превосходная дифференциальная линейность Встроенный цифровой фильтр (возможно с линейной фазой)

Большое время задержки (время ожидания выходного сигнала) Трудно мультиплексировать входы из-за временных затрат на установку цифрового фильтра

Высокоскоростные архитектуры: Параллельный АЦП (Flash)

Субинтервальный (subranging) или конвейерный (pipelined) Последовательного счета (Bit-Per-Stage)

Рис. 3.2

АЦП ПОСЛЕДОВАТЕЛЬНОГО ПРИБЛИЖЕНИЯ

АЦП последовательного приближения много лет были главным инструментом преобразования сигнала. Недавние усовершенствования разработчиков расширили диапазон частот дискретизации этих АЦП до мегагерц. Использование методов внутренних коммутируемых конденсаторов вместе с методами автокалибровки расширяет

3

a

разрешающую способность этих АЦП до 16 разрядов на стандартных CMOS-процессах без необходимости в дорогой тонкопленочной лазерной подстройке.

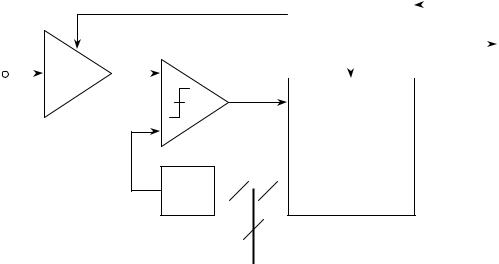

Основные элементы АЦП последовательного приближения представлены на рис.3.3. Этот АЦП выполняет преобразования в командном режиме. После подачи команды CONVERT START устройство выборки-хранения УВХ (SHA) устанавливается в режим хранения, и все разряды регистра последовательного приближения РПП (SAR) сбрасываются в "0", кроме старшего значащего разряда (MSB), который устанавливается в "1". Выходной сигнал регистра последовательного приближения (РПП) подается на внутренний ЦАП. Если выходной сигнал ЦАП больше, чем аналоговый входной сигнал, старший разряд РПП сбрасывается, в противном случае он остается установленным. Затем следующий старший значащий разряд устанавливается в "1". Если сигнал на выходе ЦАП больше, чем аналоговый входной сигнал, старший разряд РПП сбрасывается, в противном случае бит остается установленным. Описанный процесс поочередно повторяется для каждого разряда. Когда все разряды, в соответствии с входным сигналом, будут установлены в "0" или в "1", содержимое регистра последовательного приближения придет в соответствие со значением аналогового входного сигнала, и преобразование завершится. Если рассматриваемый АЦП имеет выход в виде последовательного порта, то последовательно поступаемые биты можно непосредственно передавать на выход.

Окончание преобразования индицируется сигналами end-of-convert (EOC), data-ready (DRDY) или BUSY (фактически, отсутствие сигнала BUSY индицирует окончание преобразования). Полярности и наименование этого сигнала могут отличаться для различных АЦП последовательного приближения, но основная концепция сохраняется. В начале интервала преобразования логический уровень сигнала высокий (или низкий) и остается в этом состоянии, пока преобразование не закончено. Затем уровень сигнала становиться низким (или высоким). Фронт сигнала индицирует наличие выходных данных.

АЦП ПОСЛЕДОВАТЕЛЬНОГО ПРИБЛИЖЕНИЯ

|

|

|

|

|

|

|

|

НАЧАТЬ |

|||

|

|

|

|

|

|

СИНХРОНИЗАЦИЯ |

ПРЕОБРАЗОВАНИЕ |

||||

|

|

|

|

|

|

|

|

|

|

||

АНАЛОГОВЫЙ |

|

|

КОМПАРАТОР |

|

|

|

|

|

|

||

|

|

|

|

|

EOC, DRDY ИЛИ |

||||||

|

|

|

|

|

|||||||

ВХОД |

|

|

|

|

|

|

|

|

|||

|

|

УВХ |

|

|

|

|

|

BUSY |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

РЕГИСТР ПОСЛЕД.

ПРИБЛИЖЕНИЯ

(SAR)

ЦАП

ВЫХОД

ВЫХОД

Рис. 3.3

4

a

N-разрядное преобразование осуществляется за N шагов. На первый взгляд может показаться, что 16-разрядному преобразователю для выполнения преобразования требуется в два раза больше времени, чем 8-разрядному преобразователю, но это не так. В 8-разрядном преобразователе перед принятием решения о значении очередного бита ЦАП должен установить на своем выходе сигнал с точностью, соответствующей 8 разрядам, в то время как ЦАП 16-разрядного преобразователя должен установить сигнала на своем выходе с точностью, соответствующей 16 разрядам, что занимает значительно больше времени. На практике 8-разрядный АЦП последовательного приближения может затрачивать на преобразование несколько сотен наносекунд, в то время как 16-разрядному АЦП требуется несколько микросекунд.

3-РАЗРЯДНЫЙ ЦАП С КОММУТИРУЕМЫМИ |

||||||

|

|

КОНДЕНСАТОРАМИ |

|

|||

|

БИТ 1 |

БИТ 2 |

|

БИТ 3 |

SC |

|

|

(MSB) |

|

|

(LSB) |

|

_ |

|

|

|

|

|

|

|

|

|

|

|

|

A |

|

CTOTAL = 2C |

C |

C/2 |

C/4 |

C/4 |

+ |

|

|

|

|

|

|

|

|

|

S1 |

S2 |

S3 |

S4 |

|

|

AIN |

|

|

|

|

|

|

SIN |

|

|

|

|

|

|

VREF |

|

|

|

|

|

|

ПЕРЕКЛЮЧАТЕЛИ ПОКАЗАНЫ В РЕЖИМЕ ВЫБОРКИ |

|

|||||

Рис. 3.4

Обратите внимание, что общая точность и линейность АЦП последовательного приближения определяется, прежде всего, внутренним ЦАП. До недавнего времени в большинстве прецизионных АЦП последовательного приближения для достижения желательной точности и линейности использовалась тонкопленочная лазерная подгонка. Процесс подстройки тонкопленочного резистора увеличивает стоимость системы, а значение сопротивления тонкопленочного резистора может измениться при механическом воздействии на корпус микросхемы.

По этим причинам в более новых АЦП последовательного приближения стали популярными ЦАП с коммутируемыми конденсаторами (или конденсаторами с перераспределением заряда). Преимущество ЦАП с коммутируемыми конденсаторами состоит в том, что их точность и линейность определяются, прежде всего, качеством фотолитографии, которое, в свою очередь, зависит от площади конденсаторных пластин, емкости и соотношения емкостей конденсаторов. Кроме того, для достижения высокой точности и линейности конденсаторы малой емкости могут подключаться параллельно основным конденсаторам или отключаться от них в соответствии с алгоритмом автокалибровки без необходимости применения тонкопленочной лазерной подстройки.

5

a

Согласование температурных характеристик коммутируемых конденсаторов может быть лучше, чем 1 ppm/ºC, чем и обеспечивается высокая температурная стабильность. Простой 3-разрядный ЦАП на переключаемых конденсаторах представлен на рис.3.4.

Переключатели (коммутаторы) показаны в режиме выборки, или дискретизации, когда напряжением аналогового входного сигнала AIN регулярно заряжается и разряжается параллельная комбинация всех конденсаторов. Режим хранения инициируется открытием SIN. При этом напряжение аналогового входного сигнала на конденсаторной матрице остается дискретным. Затем открывается переключатель SC, разрешая изменения Напряжения в точке А по мере коммутации переключателей разрядов. Если S1, S2, S3 и S4 замкнуты на «землю», в точке А появляется напряжение, равное - AIN. Замыкание S1 на VREF добавляет к -AIN напряжение, равное VREF /2. Затем компаратор принимает решение относительно значения старшего значащего разряда, и РПП либо оставляет S1 соединенным с VREF, либо подключает его к «земле», в зависимости от сигнала на выходе компаратора (нулевое или единичное значение выхода компаратора зависит от того, является ли напряжение в узле отрицательным или положительным). Аналогичный процесс проходит и в оставшихся двух разрядах. В конце интервала преобразования S1, S2, S3, S4 и SIN замыкаются на AIN, SC подключается к «земле», после чего преобразователь готов к новому циклу.

Обратите внимание, что для выполнения двоичного деления при управлении конденсаторами отдельных разрядов требуется дополнительный конденсатор младшего разряда (LSB) (емкостью C/4 в случае 3-разрядного ЦАП) для того, чтобы полное значение емкости конденсаторной матрицы равнялось 2C.

Работа "конденсаторного" ЦАП подобна работе резистивного R/2R ЦАП. Когда индивидуальный конденсатор разряда подключен к VREF, делитель напряжения, созданный конденсатором разряда и общей емкостью матрицы (2C), добавляет в точке А напряжение, равное весу этого разряда. Когда индивидуальный конденсатор разряда подключен к «земле», такое же напряжение, пропорциональное весу этого разряда, вычитается из суммарного напряжения в точке A.

Будучи весьма популярными, АЦП последовательного приближения поставляются с широкой гаммой разрешающих способностей, частот дискретизации, опций ввода-вывода, конструктивного исполнения и стоимостных показателей. Невозможно перечислить все их типы, поэтому на рис.3.5 представлен ряд последних, наиболее представительных РПП АЦП последовательного приближения компании Analog Devices. Обратите внимание, что многие устройства являются полными системами сбора данных с входными мультиплексорами, которые позволяют одному "ядру" АЦП обрабатывать много аналоговых каналов.

6

a

СРАВНЕНИЕ РАЗРЕШАЮЩЕЙ СПОСОБНОСТИ И ВРЕМЕНИ ПРЕОБРАЗОВАНИЯ ТИПОВЫХ АЦП ПОСЛЕДОВАТЕЛЬНОГО ПРИБЛИЖЕНИЯ

С ОДНОПОЛЯРНЫМ ИСТОЧНИКОМ ПИТАНИЯ

|

|

РАЗРЕШАЮЩАЯ |

ЧАСТОТА |

МОЩНОСТЬ, |

ЧИСЛО |

|

|

СПОСОБНОСТЬ |

ДИСКРЕТИЗАЦИИ |

мВт |

КАНАЛОВ |

|

AD7472 |

12 бит |

1,5 MSPS |

9 |

1 |

|

AD7891 |

12 бит |

500 KSPS |

85 |

8 |

AD7858/59 |

12 бит |

200 KSPS |

20 |

8 |

|

AD7887/88 |

12 бит |

125 KSPS |

3,5 |

8 |

|

AD7856/57 |

14 бит |

285 KSPS |

60 |

8 |

|

|

AD7660 |

16 бит |

100 KSPS |

15 |

1 |

|

AD974 |

16 бит |

200 KSPS |

120 |

4 |

|

AD7664 |

16 бит |

570 KSPS |

150 |

1 |

Рис. 3.5

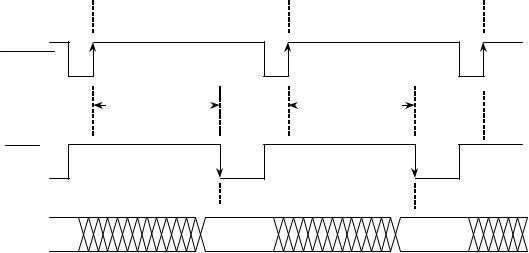

Несмотря на некоторые различия, основные принципы синхронизации большинства АЦП последовательного приближения сходны и достаточно просты (см. рис.3.6). Процесс преобразования инициируется сигналом CONVERT START. Сигнал CONVST представляет собой отрицательный импульс, положительный фронт которого запускает преобразование. Устройство выборки-хранения (УВХ) этим фронтом устанавливается в режим хранения и, используя алгоритм последовательного приближения, определяет различные разряды. Отрицательный фронт импульса CONVST устанавливает высокий уровень сигналов EOC или BUSY. По завершении преобразования устанавливается низкий уровень сигнала BUSY. В большинстве случаев задний фронт сигнала BUSY может использоваться в качестве индикатора корректности выходных данных и его можно использовать для записи выходных данных во внешний регистр. Но вследствие множества различий в терминологии и конструкции различных АЦП, при использовании определенного АЦП, следует всегда принимать во внимание конкретную спецификацию.

7

a

ВРЕМЕННАЯ ДИАГРАММА РАБОТЫ АЦП ПОСЛЕДОВАТЕЛЬНОГО ПРИБЛИЖЕНИЯ

ОТСЧЕТ X |

ОТСЧЕТ X+1 |

ОТСЧЕТ X+2 |

CONVST

ВРЕМЯ |

|

|

|

ВРЕМЯ |

ПРЕОБРА- |

|

|

|

ПРЕОБРА- |

|

|

|||

ЗОВАНИЯ |

|

|

|

ЗОВАНИЯ |

EOC,

BUSY

ВЫХОДНЫЕ |

ДАННЫЕ |

ДАННЫЕ |

ДАННЫЕ |

X |

X+1 |

Рис. 3.6

Необходимо также отметить, что некоторые АЦП последовательного приближения дополнительно к команде CONVERT START требуют внешней высокочастотной синхронизации, хотя в большинстве случаев необходимости в двух синхронизаторах нет. Частота внешнего синхронизатора, если он требуется, находится в диапазоне от 1 МГц до 30 МГц в зависимости от времени преобразования и разрешающей способности АЦП. В других АЦП последовательного приближения есть внутренний генератор, который используется для выполнения преобразования и требует только команды CONVERT START. Благодаря своей архитектуре, АЦП последовательного приближения допускают любую скорость повторения однократного преобразования, от 0 до максимального быстродействия преобразователя.

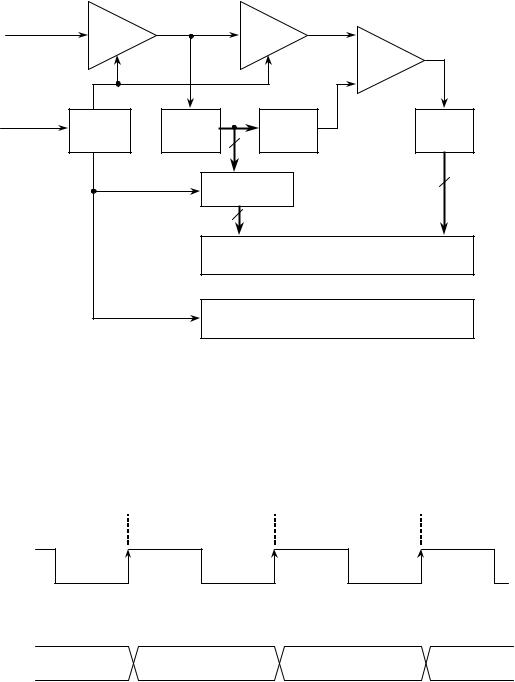

В АЦП последовательного приближения выходные данные, соответствующие дискретному входному сигналу, формируются в конце соответствующего интервала преобразования. Иначе обстоит дело в АЦП, построенных с использованием другой архитектуры, таких как сигма-дельта АЦП или АЦП с двухступенчатым конвейером, представленный на рис.3.7. Показанный на рисунке АЦП является 12-разрядным двухступенчатым конвейерным (pipelined), или субинтервальным, преобразователем. Первое преобразование выполняется 6-разрядным АЦП, который управляет 6-разрядным ЦАП. На выходе 6-разрядного ЦАП получается 6-разрядное приближение аналогового входного сигнала. Обратите внимание, что УВХ2 осуществляет временную задержку аналогового сигнала, пока 6-разрядный АЦП производит преобразование и 6-разрядный ЦАП устанавливает требуемый сигнал на выходе. Затем полученное с помощью ЦАП приближение вычитается из аналогового сигнала на выходе УВХ2, результат усиливается и оцифровывается 7-разрядным АЦП. Результаты этих двух преобразований объединяются, и дополнительный разряд используется для исправления ошибки, полученной при первом преобразовании. Типичные временные соотношения, соответствующие преобразователю этого типа, показаны на рис.3.8. Важно, что выходные данные, представленные сразу после отсчета X, фактически соответствуют отсчету X-2, то

8

a |

|

|

|

|

|

есть существует конвейерная задержка в два такта. Конвейерная архитектура свойственна |

|||||

высокоскоростным АЦП и, в большинстве случаев, конвейерная задержка не является |

|||||

главной проблемой системы в большинстве приложений, где используется этот тип |

|||||

преобразователя. |

|

|

|

|

|

АРХИТЕКТУРА 12-РАЗРЯДНОГО ДВУХСТУПЕНЧАТОГО |

|||||

|

|

КОНВЕЙЕРНОГО АЦП |

|||

АНАЛОГОВЫЙ |

|

|

|

|

|

ВХОД |

УВХ |

|

УВХ |

|

|

|

|

+ |

|||

|

1 |

|

|

2 |

|

ИМПУЛЬСЫ |

|

|

|

|

_ |

ДИСКРЕТИ- |

|

|

|

|

|

ЗАЦИИ |

СИНХРО- |

6-BIT |

|

6-BIT |

7-BIT |

|

|

||||

|

НИЗАЦИЯ |

АЦП |

6 |

ЦАП |

АЦП |

|

|

|

|

|

|

|

|

БУФЕРНЫЙ |

|

||

|

|

|

РЕГИСТР |

|

|

|

|

|

|

6 |

7 |

|

|

|

|

КОРРЕКЦИЯ ОШИБКИ |

|

12

12

ВЫХОДНОЙ РЕГИСТР

ВЫХОДНЫЕ ДАННЫЕ  12

12

Рис. 3.7

ВРЕМЕННАЯ ДИАГРАММА РАБОТЫ КОНВЕЙЕРНОГО АЦП

ОТСЧЕТ X |

ОТСЧЕТ X+1 |

ОТСЧЕТ X+2 |

СИНХРО

ИМПУЛЬСЫ

ВЫХОДНЫЕ |

ДАННЫЕ |

ДАННЫЕ |

ДАННЫЕ |

ДАННЫЕ |

X–2 |

X–1 |

X |

ПОКАЗАНА РАБОТА С ЗАДЕРЖКОЙ НА 2 ТАКТОВЫХ ЦИКЛА

Рис. 3.8

9

a

Конвейерные АЦП могут иметь более двух тактов задержки в зависимости от специфики своей архитектуры. Например, возможно выполнение преобразования за три, четыре или, возможно, даже большее количество конвейерных ступеней, что вызывает дополнительную задержку выходных данных.

Поэтому, если АЦП используется в событийно-управляемом (event-triggered ) (или однократном single-shot) режиме, требующем однозначного соответствия времени между каждым отсчетом и соответствующими данными, то конвейерная задержка может привести к нежелательному результату, и в этом случае более предпочтительна архитектура АЦП последовательного приближения. Конвейерная задержка или ожидание могут также создать проблемы в высокоскоростных системах управления с обратной связью или в приложениях с мультиплексированием данных. Кроме того, некоторые конвейерные преобразователи рассчитаны на определенную минимально допустимую скорость преобразования и должны непрерывно поддерживаться в рабочем состоянии для предотвращения насыщения внутренних узлов.

АЦП последовательного приближения с коммутируемыми конденсаторами имеет небуферированные входные цепи, подобные схеме, показанной на рис.3.9 для АЦП AD7858/59. За время сбора данных аналоговый входной сигнал должен зарядить эквивалентную входную емкость 20 пФ до необходимой величины. Если входной сигнал является сигналом постоянного тока, то сопротивление источника RS, включенное последовательно с внутренним сопротивлением выключателя 125 Ом, создает задержку с некоторой постоянной времени. Для достижения 12-разрядной точности необходимо предусмотреть интервал ожидания, соответствующий приблизительно промежутку в 9 постоянных времени для стабилизации сигнала на входе. Это определяет минимальное допустимое время выборки (достижение 14-разрядной точности требует приблизительно 10 постоянных времени, а 16разрядная точность требует приблизительно 11 постоянных времени).

tACQ > 9 × (RS + 125) Ом × 20 пФ.

Например, если RS = 50 Ом, то время выборки в этой формуле должно быть, по крайней мере, 310 нс.

В приложениях переменного тока, чтобы предотвратить искажения из-за нелинейности входной цепи АЦП, должны использоваться источники сигнала с низким выходным сопротивлением. В случае приложения с однополярным питанием должен использоваться полнодиапазонный (rail-to-rail) операционный усилитель типа AD820 с малым временем установки выходного сигнала. Малое время установки позволяет операционному усилителю быстро устранять возникающие на его входе токи переходного режима, вызванные внутренними переключениями АЦП. На рис.3.9 AD820 управляет ФНЧ, состоящим из резистора 50 Ом и конденсатора 10 нФ (частота среза приблизительно 320 КГц). Этот фильтр удаляет высокочастотные компоненты, которые могут приводить к эффекту наложения и уменьшают шум.

Использование в этом приложении операционного усилителя с однополярным питанием требует специального рассмотрения уровней сигнала. AD820 включен в инвертирующем режиме и имеет коэффициент усиления сигнала -1. На неинвертирующий вход усилителя с делителя 10,7 К/10К подается синфазное напряжение смещения +1,3 В, создавая выходное напряжение +2,6 В для VIN = 0 В, и +0,1 В для VIN = +2,5 В. Это смещение необходимо потому, что выход AD820 не может быть полностью заземлен, т.к. это ограничивается напряжением VCESAT n-p-n-транзистора выходного каскада, которое при этих условиях нагрузки приблизительно равно 50 мВ. Диапазон изменения входных

10