Шина адреса

Шина адресапредставляет собой набор проводников; по ним передается адрес ячейки памяти, в которую или из которой пересылаются данные. Как и в шине данных, по каждому проводнику передается один бит адреса, соответствующий одной цифре в адресе. Увеличение количества проводников (разрядов), используемых для формирования адреса, позволяет увеличить количество адресуемых ячеек. Разрядность шины адреса определяет максимальный объем памяти, адресуемой процессором.

Для ясности...

Представьте себе следующее. Если шина данных сравнивалась с автострадой, а ее разрядность — с количеством полос движения, то шину адреса можно ассоциировать с нумерацией домов или улиц. Количество линий в шине эквивалентно количеству цифр в номере дома. Например, если на какой-то гипотетической улице номера домов не могут состоять более чем из двух цифр (десятичных), то количество домов на ней не может быть больше ста (от 00 до 99), т. е. 102. При трехзначных номерах количество возможных адресов возрастает до 103 (от 000 до 999) и т. д.

В компьютерах применяется двоичная система счисления, поэтому при двухразрядной адресации можно выбрать только четыре ячейки (с адресами 00, 01, 10 и 11), т. е. 22, при трехразрядной — восемь (от 000 до 111), т. е. 23.

Например, в процессорах 8086 и 8088 используется 20-разрядная шина адреса, поэтому они могут адресовать 220 (1048 576) байт, или 1 Мбайт, памяти. Объемы памяти, адресуемой процессорами Intel, приведены в табл.

|

Тип процессора |

Разрядность шины адреса |

Байт |

Кбайт |

Мбайт |

Гбайт |

Тбайт |

|

8088/8086 |

20 |

1 048 576 |

1024 |

1 |

— |

— |

|

286/386SX |

24 |

16777216 |

16384 |

16 |

— |

— |

|

386DX/486/ Класс P5 |

32 |

4 294 967 296 |

4194304 |

4096 |

4 |

— |

|

Класс P6/ Класс P7 |

36 |

68 719 476 736 |

67 108 864 |

65 536 |

64 |

— |

|

Itanium |

44 |

17 592 186 044 416 |

17 179 869 184 |

16777216 |

16384 |

16 |

Шины данных и адреса независимы, и разработчики микросхем выбирают их разрядность по своему усмотрению, но, чем больше разрядов в шине данных, тем больше их и в шине адреса. Разрядность этих шин является показателем возможностей процессора: количество разрядов в шине данных определяет способность процессора обмениваться информацией, а разрядность шины адреса — объем памяти, с которым он может работать.

Внутренние регистры

Количество битов данных, которые может обработать процессор за один прием, характеризуется разрядностью внутренних регистров. Регистр — это, по существу, ячейка памяти внутри процессора; например, процессор может складывать числа, записанные в двух различных регистрах, а результат сохранять в третьем регистре. Разрядность регистра определяет количество разрядов обрабатываемых процессором данных, а также характеристики программного обеспечения и команд, выполняемых чипом.

Для ясности...

Чтобы понять, как работает микропроцессор, давайте рассмотрим шаг за шагом, как микросхема выполнит несложную задачу сложения двух чисел. Решается она в четыре простых действия, причем за каждым шагом можно проследить столько раз, сколько захотите. Помните о том, что каждый компонент процессора решает свою конкретную задачу.

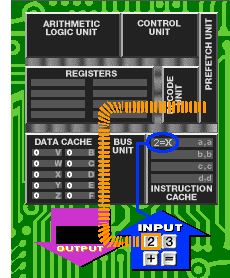

Н![]() ажатие

клавиши с цифрой "2" приводит

микропроцессор в состояние готовности

и подает блоку предварительной выборки

сигнал на запрос в системной памяти

компьютера инструкции в отношении вновь

поступивших данных, поскольку командная

кэш-память такой инструкции не содержит.

ажатие

клавиши с цифрой "2" приводит

микропроцессор в состояние готовности

и подает блоку предварительной выборки

сигнал на запрос в системной памяти

компьютера инструкции в отношении вновь

поступивших данных, поскольку командная

кэш-память такой инструкции не содержит.

.

.

Н![]() овая

инструкция по работе с данными поступает

из системной памяти компьютера через

блок шины в микропроцессор и записывается

в командную кэш-память, где ей присваивается

код "2=X".

овая

инструкция по работе с данными поступает

из системной памяти компьютера через

блок шины в микропроцессор и записывается

в командную кэш-память, где ей присваивается

код "2=X".

В![]() след

за этим блок предварительной выборки

запрашивает из кэш-памяти копию кода

"2=X", которую направляет для

дальнейшей обработки в блок декодировки.

след

за этим блок предварительной выборки

запрашивает из кэш-памяти копию кода

"2=X", которую направляет для

дальнейшей обработки в блок декодировки.

.

.

Б![]() лок

декодировки раскодирует инструкцию

"2=X", преобразуя ее в цепочку двоичных

символов, которая пересылается в

управляющий блок и в кэш данных, давая

им указание о том, как с полученной

инструкцией поступать дальше.

лок

декодировки раскодирует инструкцию

"2=X", преобразуя ее в цепочку двоичных

символов, которая пересылается в

управляющий блок и в кэш данных, давая

им указание о том, как с полученной

инструкцией поступать дальше.

П![]() оскольку

блоком декодировки принято решение о

сохранении цифры 2 в кэш данных, управляющий

блок выполняет соответствующую инструкцию

для кода "2=X": цифре 2 в кэш-памяти

данных присваивается адрес "Х",

здесь она и будет находиться в ожидании

дальнейших указаний

оскольку

блоком декодировки принято решение о

сохранении цифры 2 в кэш данных, управляющий

блок выполняет соответствующую инструкцию

для кода "2=X": цифре 2 в кэш-памяти

данных присваивается адрес "Х",

здесь она и будет находиться в ожидании

дальнейших указаний

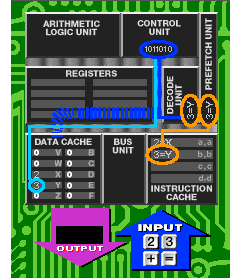

Н![]() ажав

клавишу с цифрой "3", Вы дадите блоку

предварительной выборки команду на

запрос в системной памяти компьютера

и в командной кэш-памяти инструкций о

действиях в отношении вновь поступивших

данных. Поскольку командная кэш-память

таких инструкций не содержит, они

поступят из системной памяти.

ажав

клавишу с цифрой "3", Вы дадите блоку

предварительной выборки команду на

запрос в системной памяти компьютера

и в командной кэш-памяти инструкций о

действиях в отношении вновь поступивших

данных. Поскольку командная кэш-память

таких инструкций не содержит, они

поступят из системной памяти.

.

.

А![]() налогично

команде "2=X," новые инструкции по

данным поступают из системной памяти

компьютера в микропроцессор и записываются

в командную кэш-память, где получают

код адресации "3=Y".

налогично

команде "2=X," новые инструкции по

данным поступают из системной памяти

компьютера в микропроцессор и записываются

в командную кэш-память, где получают

код адресации "3=Y".

П![]() осле

этого копия кода "3=Y" поступает из

командной кэш-памяти в блок предварительной

выборки, откуда переправляется в

декодирующий блок для дальнейшей

обработки.

осле

этого копия кода "3=Y" поступает из

командной кэш-памяти в блок предварительной

выборки, откуда переправляется в

декодирующий блок для дальнейшей

обработки.

.

.

Д![]() екодирующий

блок раскодирует инструкцию "3=Y",

преобразуя ее в цепочку двоичных

символов, которую направляет в управляющий

блок и в кэш-память данных, давая им

указание о том, как с данной инструкцией

поступать дальше.

екодирующий

блок раскодирует инструкцию "3=Y",

преобразуя ее в цепочку двоичных

символов, которую направляет в управляющий

блок и в кэш-память данных, давая им

указание о том, как с данной инструкцией

поступать дальше.

П![]() оскольку

декодирующий блок принимает решение о

сохранении цифры 3 в кэш-памяти данных,

то он выполняет соответствующую

инструкцию для кода "3=Y": цифре 3

присваивается в кэш-памяти данных адрес

"Y", где она, аналогично цифре 2, и

будет находиться в ожидании дальнейших

указаний.

оскольку

декодирующий блок принимает решение о

сохранении цифры 3 в кэш-памяти данных,

то он выполняет соответствующую

инструкцию для кода "3=Y": цифре 3

присваивается в кэш-памяти данных адрес

"Y", где она, аналогично цифре 2, и

будет находиться в ожидании дальнейших

указаний.

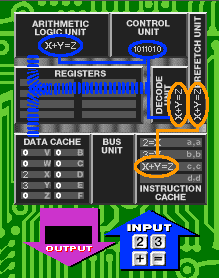

Н![]() ажатие

клавиши со значком "+" заставляет

блок предварительной выборки запросить

из главной памяти компьютера и командной

кэш-памяти инструкции в отношении вновь

поступивших данных. Как и в предыдущих

случаях, эти инструкции должны быть

получены из системной памяти.

ажатие

клавиши со значком "+" заставляет

блок предварительной выборки запросить

из главной памяти компьютера и командной

кэш-памяти инструкции в отношении вновь

поступивших данных. Как и в предыдущих

случаях, эти инструкции должны быть

получены из системной памяти.

.

.

П![]() оскольку

речь идет о не использовавшейся ранее

инструкции, "плюс" поступает в

микропроцессор из системной памяти

компьютера и записывается в командную

кэш-память с присвоением адресного кода

"X+Y=Z", обозначающего операцию

сложения.

оскольку

речь идет о не использовавшейся ранее

инструкции, "плюс" поступает в

микропроцессор из системной памяти

компьютера и записывается в командную

кэш-память с присвоением адресного кода

"X+Y=Z", обозначающего операцию

сложения.

В![]() след

за этим блок предварительной выборки

запрашивает из командной кэш-памяти

копию кода "X+Y=Z" и пересылает ее

блоку декодировки для дальнейшей

обработки.

след

за этим блок предварительной выборки

запрашивает из командной кэш-памяти

копию кода "X+Y=Z" и пересылает ее

блоку декодировки для дальнейшей

обработки.

Б![]() лок

декодировки раскодирует инструкцию

"X+Y=Z", преобразуя ее в цепочку

двоичных символов, которую направляет

в управляющий блок и в кэш-память данных,

давая им указание о том, как с данной

инструкцией поступать дальше. Одновременно

арифметическое логическое устройство

(ALU) получает указание на выполнение

операции СЛОЖЕНИЯ.

лок

декодировки раскодирует инструкцию

"X+Y=Z", преобразуя ее в цепочку

двоичных символов, которую направляет

в управляющий блок и в кэш-память данных,

давая им указание о том, как с данной

инструкцией поступать дальше. Одновременно

арифметическое логическое устройство

(ALU) получает указание на выполнение

операции СЛОЖЕНИЯ.

.

.

У![]() правляющий

блок расчленяет код, а арифметическое

логическое устройство (ALU) выполняет по

команде операцию СЛОЖЕНИЯ чисел,

закодированных как "X" и "Y" и

извлеченных из кэш-памяти данных. После

этого ALU, "посовещавшись" со своими

"партнерами" — регистрами, пересылает

им полученное число 5 для записи по

одному из адресов.

правляющий

блок расчленяет код, а арифметическое

логическое устройство (ALU) выполняет по

команде операцию СЛОЖЕНИЯ чисел,

закодированных как "X" и "Y" и

извлеченных из кэш-памяти данных. После

этого ALU, "посовещавшись" со своими

"партнерами" — регистрами, пересылает

им полученное число 5 для записи по

одному из адресов.

.

.

П![]() осле

нажатия клавиши со значком "=" блок

предварительной выборки в очередной

раз проверяет командную кэш-память на

предмет наличия инструкций, относящихся

к вновь поступившим данным. Как и прежде,

такие инструкции там отсутствуют.

осле

нажатия клавиши со значком "=" блок

предварительной выборки в очередной

раз проверяет командную кэш-память на

предмет наличия инструкций, относящихся

к вновь поступившим данным. Как и прежде,

такие инструкции там отсутствуют.

.

.

И![]() нструкция

для значка "=" поступает в

микропроцессор из системной памяти

компьютера через блок шины и записывается

в командную кэш-память, получив код

адресации "Print Z" ("отобразить на

экране символ Z").

нструкция

для значка "=" поступает в

микропроцессор из системной памяти

компьютера через блок шины и записывается

в командную кэш-память, получив код

адресации "Print Z" ("отобразить на

экране символ Z").

В![]() след

за этим блок предварительной выборки

запрашивает из командной кэш-памяти

копию кода "Print Z", которую пересылает

декодирующему блоку для дальнейшей

обработки.

след

за этим блок предварительной выборки

запрашивает из командной кэш-памяти

копию кода "Print Z", которую пересылает

декодирующему блоку для дальнейшей

обработки.

.

.

Д![]() екодирующий

блок раскодирует инструкцию "Print Z",

преобразуя ее в цепочку двоичных

символов, которая затем пересылается

управляющему блоку с указанием на то,

как с полученной инструкцией поступать

дальше.

екодирующий

блок раскодирует инструкцию "Print Z",

преобразуя ее в цепочку двоичных

символов, которая затем пересылается

управляющему блоку с указанием на то,

как с полученной инструкцией поступать

дальше.

Т![]() еперь,

когда значение величины, представленной

кодом Z, уже вычисленно и записано в

позиции № 5 блока регистров, для завершения

операции сложения 2+3 остается выполнить

команду вывода содержания регистра 5

на экран дисплея. На этом работа

микропроцессора заканчивается.

еперь,

когда значение величины, представленной

кодом Z, уже вычисленно и записано в

позиции № 5 блока регистров, для завершения

операции сложения 2+3 остается выполнить

команду вывода содержания регистра 5

на экран дисплея. На этом работа

микропроцессора заканчивается.

.

.

Во всех современных процессорах внутренние регистры являются 64-разрядными (но часто еще встречаются 32-разрядные). В некоторых процессорах разрядность внутренней шины данных (а шина состоит из линий передачи данных и регистров!) больше, чем разрядность внешней. Так, например, в процессорах 8088 и 386SX разрядность внутренней шины только вдвое больше разрядности внешней шины. Такие процессоры (их часто называют половинчатыми или гибридными) обычно являются более дешевыми вариантами исходных.

Если разрядность внутренних регистров больше разрядности внешней шины данных, то для их полной загрузки необходимо несколько циклов считывания.

В процессорах Pentium шина данных 64-разрядная, а регистры 32-разрядные. Такое построение на первый взгляд кажется странным, если не учитывать, что в этом процессоре для обработки информации служат два 32-разрядных параллельных конвейера. Pentium во многом подобен двум 32-разрядным процессорам, объединенным в одном корпусе, а 64-разрядная шина данных позволяет быстрее заполнить рабочие регистры. Архитектура процессора с несколькими конвейерами называется суперскалярной.

Современные процессоры, имеют от шести внутренних конвейеров для выполняющихся команд. Хотя некоторые из указанных внутренних конвейеров специализированы (т. е. предназначены для выполнения специальных функций), эти процессоры могут все же выполнять три команды за один цикл. В последних версиях процессоров используются 10-ступенчатые параллельные конвейеры, которые позволяют выполнять до 20 операций в течение одного такта.