ТСвИС / (х) архитектура устройства компьютера.ассемблер

.pdf

Архитектура ЭВМ и систем К.т.н., доц. каф. ИСТ Кислицын Д.И. – ННГАСУ, 2010г.

Архитектура ЭВМ и систем К.т.н., доц. каф. ИСТ Кислицын Д.И. – ННГАСУ, 2010г.

Материнская плата

Чипсет Intel X58

Архитектура ЭВМ и систем К.т.н., доц. каф. ИСТ Кислицын Д.И. – ННГАСУ, 2010г.

Архитектура ЭВМ и систем К.т.н., доц. каф. ИСТ Кислицын Д.И. – ННГАСУ, 2010г.

Материнская плата

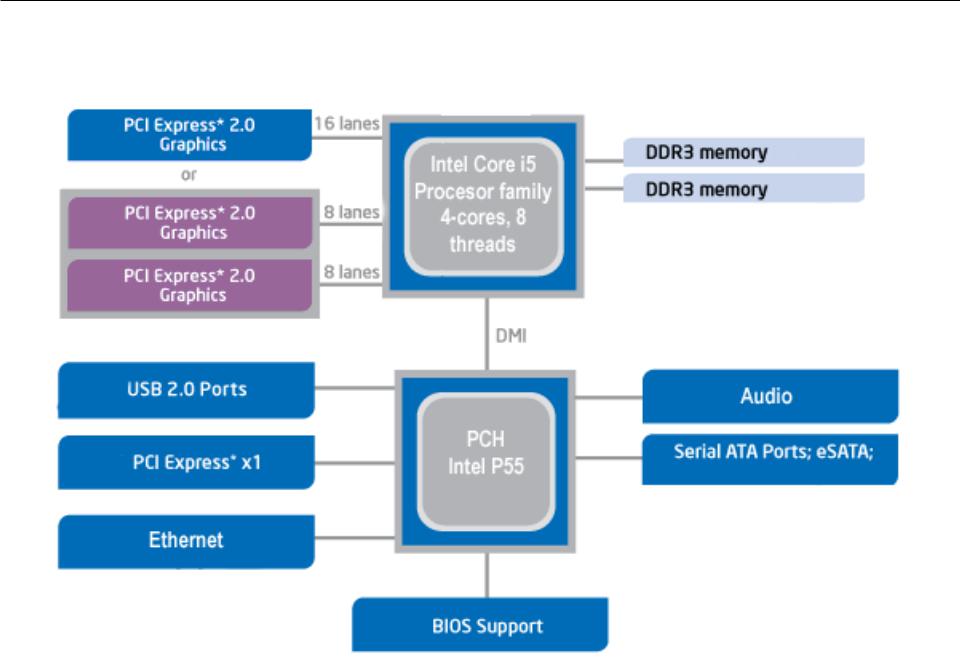

Чипсет Intel P55

Архитектура ЭВМ и систем К.т.н., доц. каф. ИСТ Кислицын Д.И. – ННГАСУ, 2010г.

Архитектура ЭВМ и систем К.т.н., доц. каф. ИСТ Кислицын Д.И. – ННГАСУ, 2010г.

Материнская плата

ASUSTeK P5E3 Deluxe

Архитектура ЭВМ и систем К.т.н., доц. каф. ИСТ Кислицын Д.И. – ННГАСУ, 2010г.

Архитектура ЭВМ и систем К.т.н., доц. каф. ИСТ Кислицын Д.И. – ННГАСУ, 2010г.

|

|

Материнская плата |

|

|

ASUSTeK P5E3 Deluxe |

Гнездо процессора |

Socket LGA775 |

|

|

|

|

Поддержка типов |

Pentium 4 5xx/6xx, Celeron 4x0, Pentium D 8xx/9xx, Pentium E21x0, Core 2 Duo E4x00/E6xx0, Core 2 |

|

процессоров |

Extreme X6800/QX6x00/QX6x50, Core 2 Quad Q6x00 |

|

|

|

|

Чипсет |

Intel X38 (82X38 + 82801IR (ICH9R)) |

|

|

|

|

Частота шины |

1600, 1333, 1066, 800 МГц |

|

|

|

|

Hyper Threading |

Да |

|

|

|

|

Кол-во разъемов PCI |

2 |

|

|

|

|

Кол-во PCI Express 2.0 |

2 |

слота 1x, 3 слота 16x (один из слотов работает в режиме 4х или 1х) |

|

|

|

Поддержка CrossFire |

Да |

|

|

|

|

Кол-во разъемов DDR3 |

4 |

(поддержка двухканального режима) |

|

|

|

Тип ОЗУ |

DDR3 PC3-8500 (DDR3-1066), PC3-6400 (DDR3-800), PC3-10600 (DDR3-1333), DDR3-1600,DDR3-1800 |

|

|

|

|

Max объем ОЗУ |

8 |

Гб |

|

|

|

Звук |

8-канальный HDA кодек Analog Devices AD1988B |

|

|

|

|

Видео |

Нет |

|

|

|

|

Serial ATA-II |

8 |

каналов с возможностью подключения 6и внутренних устройств и 2х внешних |

|

|

|

UDMA/133 |

1 |

канал с возможностью подключения 2х устройств |

|

|

|

Сеть |

2 |

сетевых контроллера (10/100/1000 Мбит/сек) |

|

|

|

Кол-во USB 2.0 |

6 |

|

|

|

|

Архитектура ЭВМ и систем К.т.н., доц. каф. ИСТ Кислицын Д.И. – ННГАСУ, 2010г.

Архитектура ЭВМ и систем К.т.н., доц. каф. ИСТ Кислицын Д.И. – ННГАСУ, 2010г.

Материнская плата

ASUS Maximus III Extreme

Архитектура ЭВМ и систем К.т.н., доц. каф. ИСТ Кислицын Д.И. – ННГАСУ, 2010г.

Архитектура ЭВМ и систем К.т.н., доц. каф. ИСТ Кислицын Д.И. – ННГАСУ, 2010г.

Материнская плата

ASUS Maximus III Extreme

Гнездо процессора |

Socket LGA1156 |

|

|

|

|

Поддержка типов процессоров |

Intel Core i7/Core i5/Core i3 |

|

|

|

|

Чипсет |

Intel P55 |

|

|

|

|

Кол-во разъемов PCI |

1 |

|

|

|

|

Кол-во PCI Express 2.0 |

5 слота 16x (один из слотов работает в режиме 4х или 1х) |

|

|

|

|

Поддержка |

Да |

|

CrossFire / SLI |

|

|

|

|

|

Кол-во разъемов DDR3 |

4 (поддержка двухканального режима) |

|

|

|

|

Тип ОЗУ |

DDR3 DIMM, 1066 - 2200 МГц |

|

|

|

|

Max объем ОЗУ |

16 Гб |

|

|

|

|

Звук |

10-канальный VIA VT2020 |

|

|

|

|

Видео |

Нет |

|

|

|

|

Serial ATA-II |

7 (3 Гбит/с) + 2 (6 Гбит/с) |

|

|

|

|

Сеть |

1 Гбит/с |

Realtek RTL8112L |

|

|

|

Кол-во USB |

11 (USB 2.0) + 2 (USB 3.0) |

|

|

|

|

Архитектура ЭВМ и систем К.т.н., доц. каф. ИСТ Кислицын Д.И. – ННГАСУ, 2010г.

Архитектура ЭВМ и систем К.т.н., доц. каф. ИСТ Кислицын Д.И. – ННГАСУ, 2010г.

П а м я т ь

ROM – Read Only Memory (ПЗУ)

Неперезаписы |

|

|

Перезаписываемая |

|

||

ваемая |

|

|

(Flash-Memory) |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

NOR |

|

NAND |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Статическая (SRAM - Static RAM)

Выполняется на базе триггеров + малое время срабатывания

-низкая удельная плотность данных

-высокое энергопотребление

Используется в качестве буферной (кэш-памяти)

RAM – Random Access Memory (ОЗУ)

Динамическая (DRAM – Dynamic RAM)

Выполняется на базе эл.ѐмкости

+высокая удельная плотность данных

+низкое энергопотребление

- большое время срабатывания Используется в качестве основного вида памяти

•EDO DRAM (Extended Data Output DRAM)

•SDRAM (Synchronous DRAM)

•DDR SDRAM (Double Data Rate SDRAM)

•DRDRAM (Direct RAMBus DRAM)

|

|

Форм-факторы микросхем памяти |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

SIMM - Single Inline Memory Module |

|

DIMM - Dual Inline Memory Module |

|||

|

|

|

|

|

|

|

|

|

|

|

|

30 pin |

|

72 pin |

|

168, 184, 240 pin |

|

|

|

|

|

|

|

286-, 386- и некоторые |

486компьютеры и |

|

Pentium II и выше… |

||

486компьютеры |

Pentium от 66MHz до |

|

|

|

|

|

|

200MMX |

|

|

|

Архитектура ЭВМ и систем К.т.н., доц. каф. ИСТ Кислицын Д.И. – ННГАСУ, 2010г.

Архитектура ЭВМ и систем К.т.н., доц. каф. ИСТ Кислицын Д.И. – ННГАСУ, 2010г.

Оперативная память

Адресация ячеек памяти

Задача адресации заключается в указании на текущую ячейку памяти, к которой происходит обращение процессора. Адрес текущей ячейки как правило записывается в один или несколько регистров процессора.

Регистром называется функциональный узел, осуществляющий приѐм, хранение и передачу информации. Регистры состоят из группы триггеров.

По назначению регистры различаются на:

•аккумулятор — используется для хранения промежуточных результатов арифметических и логических операций и инструкций ввода-вывода;

•флаговые — хранят признаки результатов арифметических и логических операций;

•общего назначения — хранят операнды арифметических и логических выражений, индексы и адреса;

•указательные — хранят указатели на специальные области памяти (указатель текущей операции, указатель базы, указатель стека);

•сегментные — хранят адреса и селекторы сегментов памяти;

•управляющие — хранят информацию, управляющую состоянием процессора, а также адреса системных таблиц.

Архитектура ЭВМ и систем К.т.н., доц. каф. ИСТ Кислицын Д.И. – ННГАСУ, 2010г.

Архитектура ЭВМ и систем К.т.н., доц. каф. ИСТ Кислицын Д.И. – ННГАСУ, 2010г.

Оперативная память

Адресация ячеек памяти

Непосредственная адресация – указание в команде самого значения операнда, а не его адреса.

Прямая адресация - указание в команде непосредственно абсолютного адреса операнда. Косвенная адресация - указание в команде регистра или адреса ячейки памяти, в которой

находится абсолютный адрес операнда или его составляющие.

Ассоциативная адресация - указание в команде не адреса, а идентифицирующего содержательного признака, подлежащего выборке.

Неявная адресация – адрес операнда в команде не указан, но он подразумевается кодом операции.

Относительная адресация - исполнительный адрес определяется как сумма адресного кода команды и базового адреса, как правило хранящегося в специальном регистре — регистре базы. Относительная адресация позволяет при меньшей длине адресного кода команды обеспечить доступ к любой ячейке памяти.

Стековая адресация — структура данных с методом доступа к элементам LIFO (англ. Last In

— First Out, «последним пришел — первым вышел»). Чаще всего принцип работы стека сравнивают со стопкой тарелок: чтобы взять вторую сверху, нужно снять верхнюю. Добавление элемента, называемое также проталкиванием (push), возможно только в вершину стека (добавленный элемент становится первым сверху). Удаление элемента, называемое также выталкивание (pop), возможно также только из вершины стека, при этом, второй сверху элемент становится верхним. Стеки широко применяются в вычислительной технике — в частности, для отслеживания точек возврата из подпрограмм используется стек вызовов, который является неотъемлемой частью архитектуры большинства современных процессоров.

Архитектура ЭВМ и систем К.т.н., доц. каф. ИСТ Кислицын Д.И. – ННГАСУ, 2010г.

Архитектура ЭВМ и систем К.т.н., доц. каф. ИСТ Кислицын Д.И. – ННГАСУ, 2010г.

Оперативная память

SDRAM DIMM - синхронная динамическая память с произвольным доступом. Массовый выпуск SDRAM начался в 1993 году. Первоначально этот тип памяти предлагался в качестве альтернативы для дорогой видеопамяти (VRAM), однако вскоре SDRAM завоевал популярность и стал применяться в качестве ОЗУ, постепенно вытесняя другие типы динамической памяти.

Синхронная работа SDRAM в отличие от стандартной и асинхронной DRAMs, имеет таймер ввода данных, таким образом системный таймер, который пошагово контролирует деятельность микропроцессора, может также управлять работой SDRAM. Это означает, что контроллер памяти знает точный цикл таймера на котором запрошенные данные будут обработаны. В результате, это освобождает процессор от необходимости находится в состоянии ожидания между моментами доступа к памяти.

SDR (Single Data Rate) SDRAM

DDR (Double Data Rate) SDRAM

DDR2 SDRAM

DDR3 SDRAM

RDRAM - разработана компанией Rambus в 1996 г. Более производительная, чем DDR. Недостатки:

Θвысокая стоимость;

Θпарная установка модулей;

Θжѐсткие требования для разработчиков материнских плат.