ТСвИС / (х) архитектура устройства компьютера.ассемблер

.pdf

Архитектура ЭВМ и систем К.т.н., доц. каф. ИСТ Кислицын Д.И. – ННГАСУ, 2010г.

Архитектура ЭВМ и систем К.т.н., доц. каф. ИСТ Кислицын Д.И. – ННГАСУ, 2010г.

Архитектура ЭВМ и систем

Введение. Предпосылки создания ЭВМ Информация и Информатика Эволюция ЭВМ

Логические основы построения вычислительной машины Электронные технологии и элементы, применяемые в ЭВМ Алгоритмы и языки программирования Состав машинных команд. Адресация регистров и ячеек памяти в ПК

Программное обеспечение компьютера

Центральный процессор Архитектура фон Неймана Структура ПК Материнская плата

Оперативная память

Оптический привод Жѐсткий диск Основы Ассемблера Видеокарта Монитор

Клавиатура

Мышь Принтер. Технологии печати Сканеры

Сравнение последовательных и параллельных шин Сети ЭВМ

Архитектура ЭВМ и систем К.т.н., доц. каф. ИСТ Кислицын Д.И. – ННГАСУ, 2010г.

Архитектура ЭВМ и систем К.т.н., доц. каф. ИСТ Кислицын Д.И. – ННГАСУ, 2010г.

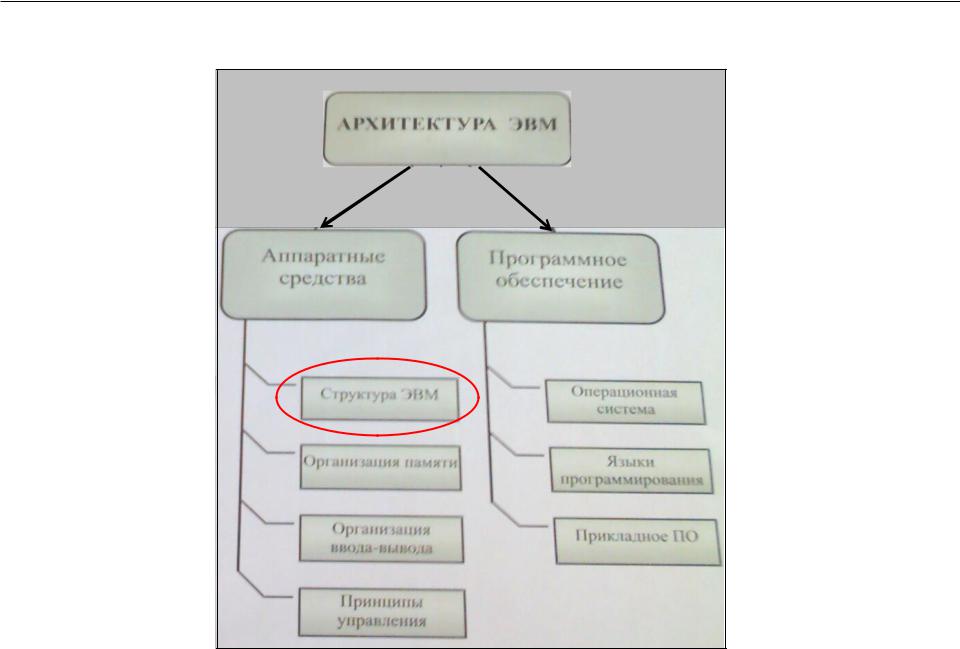

Основные компоненты архитектуры ЭВМ

Архитектура ЭВМ и систем К.т.н., доц. каф. ИСТ Кислицын Д.И. – ННГАСУ, 2010г.

Архитектура ЭВМ и систем К.т.н., доц. каф. ИСТ Кислицын Д.И. – ННГАСУ, 2010г.

Микропроцессор

Микропроцессор – процессор (устройство, отвечающее за выполнение арифметических, логических операций и операций управления, записанных в машинном коде), реализованный в виде одной микросхемы или комплекта из нескольких

специализированных микросхем.

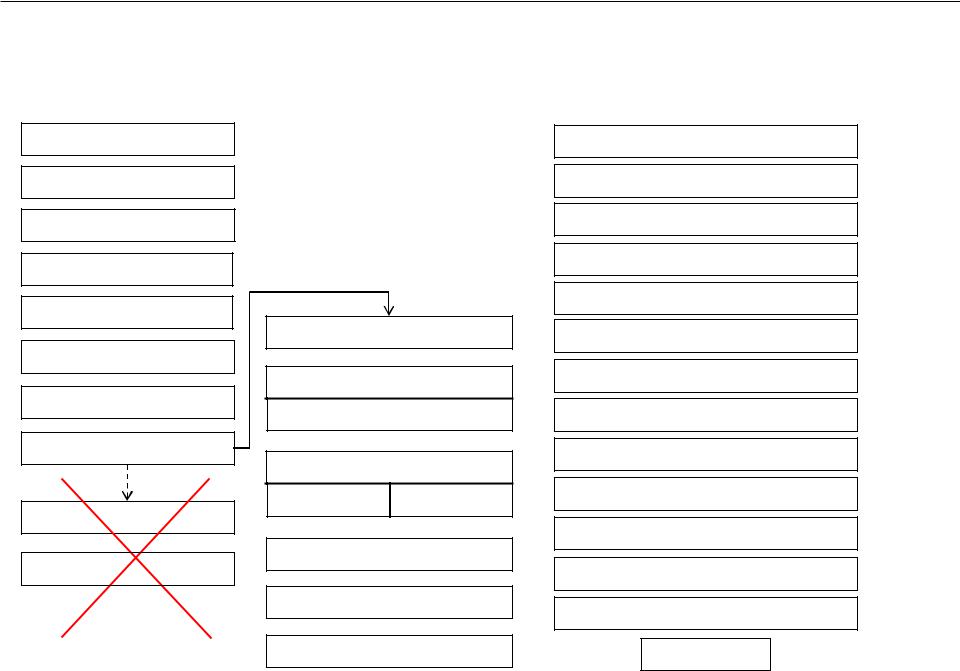

Классификация микропроцессоров

Принцип реализации

|

RISC процессоры |

|

|

|

|

CISC процессоры |

|

||||

|

(с сокращённым набором команд) |

|

|

|

(с полным набором команд) |

|

|||||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

Внутренняя структура |

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

Гарвардская архитектура |

|

|

|

|

|

Архитектура Фон-Неймана |

|

|

||

|

(раздельное хранение и |

|

|

|

|

|

|

(совместного хранения |

|

|

|

|

обработка команд и данных) |

|

|

|

|

|

|

программ и данных ) |

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

Система команд |

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

||||||

|

Аккумуляторные микропроцессоры |

|

|

|

МП с регистрами общего назначения |

|

|||||

|

(результат большинства операций |

|

|

|

(представляющие собой часть регистров |

|

|||||

|

сохраняется в специальном регистре, |

|

|

|

процессора, использующихся без |

|

|||||

|

который называется «аккумулятор») |

|

|

|

ограничения в арифметических операциях) |

|

|||||

Архитектура ЭВМ и систем К.т.н., доц. каф. ИСТ Кислицын Д.И. – ННГАСУ, 2010г.

Архитектура ЭВМ и систем К.т.н., доц. каф. ИСТ Кислицын Д.И. – ННГАСУ, 2010г.

Микропроцессор

Микропроцессор выполняет следующие функции:

-выборку команд программы из основной памяти

-дешифрацию команд

-выполнение арифметических, логических и других операций,

закодированных в командах

-управление пересылкой информации между регистрами и основной памятью, между устройствами ввода/вывода

-отработку сигналов от устройств ввода/вывода, в том числе реализацию прерываний с этих устройств

-управление и координацию работы основных узлов МП

Архитектура ЭВМ и систем К.т.н., доц. каф. ИСТ Кислицын Д.И. – ННГАСУ, 2010г.

Архитектура ЭВМ и систем К.т.н., доц. каф. ИСТ Кислицын Д.И. – ННГАСУ, 2010г.

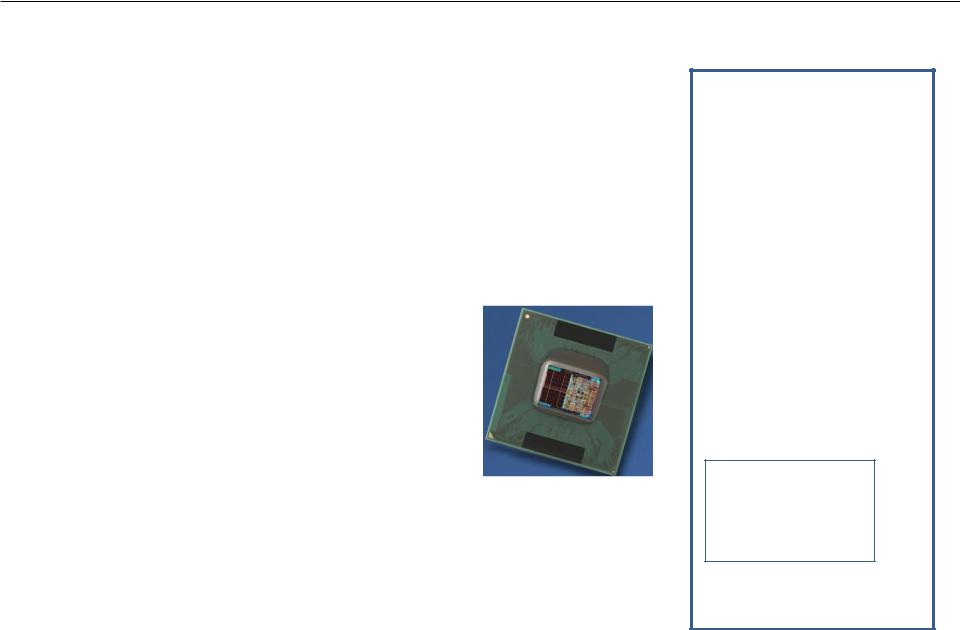

Центральный процессор

Центральный процессор (ЦПУ, CPU, от англ. Central Processing Unit) — это основной рабочий компонент компьютера, который выполняет арифметические и

логические операции, заданные программой, управляет

вычислительным процессом и координирует работу всех устройств компьютера.

Современные процессоры выполняются в виде микропроцессоров (МП).

Физически микропроцессор представляет собой интегральную схему

— тонкую пластинку кристаллического кремния прямоугольной формы площадью всего несколько квадратных миллиметров, на которой размещены схемы, реализующие все функции процессора.

Кристалл-пластинка обычно помещается в

пластмассовый или керамический плоский корпус и

соединяется золотыми проводками с металлическими штырьками, чтобы его можно было присоединить к системной плате компьютера.

Микропроцессор

Устройство |

|

И |

управления (УУ) |

|

|

|

н |

|

|

|

|

|

|

т |

|

|

|

Арифметико- |

|

е |

|

р |

|

логическое |

|

|

|

ф |

|

устройство (АЛУ) |

|

|

|

е |

|

|

|

|

|

|

й |

|

|

|

Микро- |

|

с |

|

н |

|

процессорная |

|

|

|

а |

|

память |

|

|

|

я |

|

(МПП) |

|

|

|

|

|

кэш |

|

с |

|

|

|

|

||

|

|

и |

Математический |

|

с |

|

т |

|

сопроцессор |

|

|

|

е |

|

|

|

|

|

|

м |

|

|

а |

|

|

|

Архитектура ЭВМ и систем К.т.н., доц. каф. ИСТ Кислицын Д.И. – ННГАСУ, 2010г.

Архитектура ЭВМ и систем К.т.н., доц. каф. ИСТ Кислицын Д.И. – ННГАСУ, 2010г.

Центральный процессор

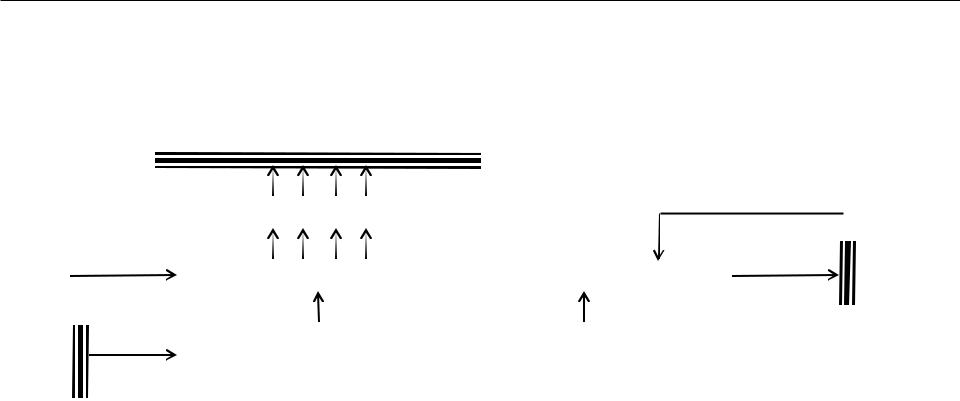

Устройство управления (УУ) – вырабатывает управляющие сигналы, поступающие по кодовым шинам инструкций во все блоки ЭВМ

От

генератора

тактовых

импульсов

Код

команды

Кодовая шина данных (КШД)

Кодовая шина инструкций (КШИ)

Код команды

|

|

|

|

От микропроцессорной |

|

|

ПЗУ микропрограмм |

|

|

||

|

|

|

|

памяти |

|

|

|

|

|

|

|

|

|

|

|

|

Код адреса |

|

Дешифратор операций |

|

|

Узел формирования адреса |

|

|

|

|

|

||

|

|

|

|

|

Кодовая шина |

|

|

|

|

|

|

|

Регистр команд |

||||

|

адреса (КША) |

||||

|

|

|

|

|

|

|

КОП |

|

|

Адреса операндов |

|

|

|

|

|

|

|

Регистр команд – запоминающий регистр, хранит код команды: код выполняемой операции и адреса операндов

Дешифратор операции – логический блок, выбирающий в соответствии с поступающим из регистра команд кодом операции (КОП) один из множества имеющихся у него выходов

ПЗУ микропрограмм – хранит управляющие сигналы, необходимые для выполнения в блоках ПК операций обработки информации

Узел формирования адреса - устройство, вычисляющее полный адрес ячейки памяти (регистра) по реквизитам , поступающим из регистра команд и регистров МПП

КШД, КША и КШИ – часть внутренней интерфейсной шины микропроцессора

Архитектура ЭВМ и систем К.т.н., доц. каф. ИСТ Кислицын Д.И. – ННГАСУ, 2010г.

Архитектура ЭВМ и систем К.т.н., доц. каф. ИСТ Кислицын Д.И. – ННГАСУ, 2010г.

Центральный процессор

Арифметико-логическое устройство (АЛУ) – предназначено для выполнения арифметических и логических операций преобразования информации.

|

|

Регистр 1: 1-е число и результат |

|

|

|

Кодовая |

|

|

|

|

|

|

|

|

|

||

шина |

|

|

|

|

Схемы |

|

Регистр 2: 2-е число |

|

|||

данных |

|

|

|

управления |

|

(КШД) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Сумматор |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Кодовая

шина

инструкций (КШИ)

Микропроцессорная память (кэш) – предназначена для кратковременного хранения информации, участвующей в вычислениях в ближайшие такты работы процессора. Имеет небольшой объѐм (до нескольких Мб), но очень высокое быстродействие (время доступа измеряется нс).

Интерфейсная часть микропроцессора – предназначена для связи и согласования МП с системной шиной ПК, а также для формирования полных адресов операндов и команд.

Архитектура ЭВМ и систем К.т.н., доц. каф. ИСТ Кислицын Д.И. – ННГАСУ, 2010г.

Архитектура ЭВМ и систем К.т.н., доц. каф. ИСТ Кислицын Д.И. – ННГАСУ, 2010г.

Центральный процессор

Этапы цикла выполнения:

1.Процессор выставляет число, хранящееся в регистре счѐтчика команд, на шину адреса, и отдаѐт памяти команду чтения

2.Выставленное число является для памяти адресом; память, получив адрес и команду чтения, выставляет содержимое, хранящееся по этому адресу, на шину данных, и сообщает о готовности

3.Процессор получает число с шины данных, интерпретирует его как команду (машинную инструкцию) из своей системы команд и исполняет еѐ

4.Если последняя команда не является командой перехода, процессор увеличивает на единицу (в предположении, что длина каждой команды равна единице) число, хранящееся в счѐтчике команд; в результате там образуется адрес следующей команды

5.Снова выполняется п. 1

Архитектура ЭВМ и систем К.т.н., доц. каф. ИСТ Кислицын Д.И. – ННГАСУ, 2010г.

Архитектура ЭВМ и систем К.т.н., доц. каф. ИСТ Кислицын Д.И. – ННГАСУ, 2010г.

Центральный процессор

«Десктопные» процессоры (старшие модели)

Процессоры Intel

4-битные (1971)

8-битные (1972)

16-битные x86 (1978)

32-битные x86 (1981)

Pentium I (1993)

Pentium Pro (1995)

Pentium II (1997)

Pentium III (1999)

Pentium IV (2000)

Pentium D (2005) [2]

Pentium M (2003)

Core (2006)

Solo  Duo

Duo

Core 2 (2006)

Duo Quad

Intel Core i7 (2008) [до 6]

Intel Core i5 (2009) [2, 4]

Intel Core i3 (2010) [2]

Процессоры AMD

Am9080/ 8080 (1974)

Am2900 (1975)

16-битные x86 (1979)

Am29K (1987)

Am486 (1993)

K5(1996)

K6(1998)

K6-2(1998)

K6-III (1999)

K7 - Athlon (1999) [1, 2]

K8 - Athlon 64 (2003) [1, 2]

K8 - Turion 64 (2005) [1, 2]

K10 – Phenom (2007) [2, 3, 4, 6]

AMD Fusion

Архитектура ЭВМ и систем К.т.н., доц. каф. ИСТ Кислицын Д.И. – ННГАСУ, 2010г.

Архитектура ЭВМ и систем К.т.н., доц. каф. ИСТ Кислицын Д.И. – ННГАСУ, 2010г.

Центральный процессор

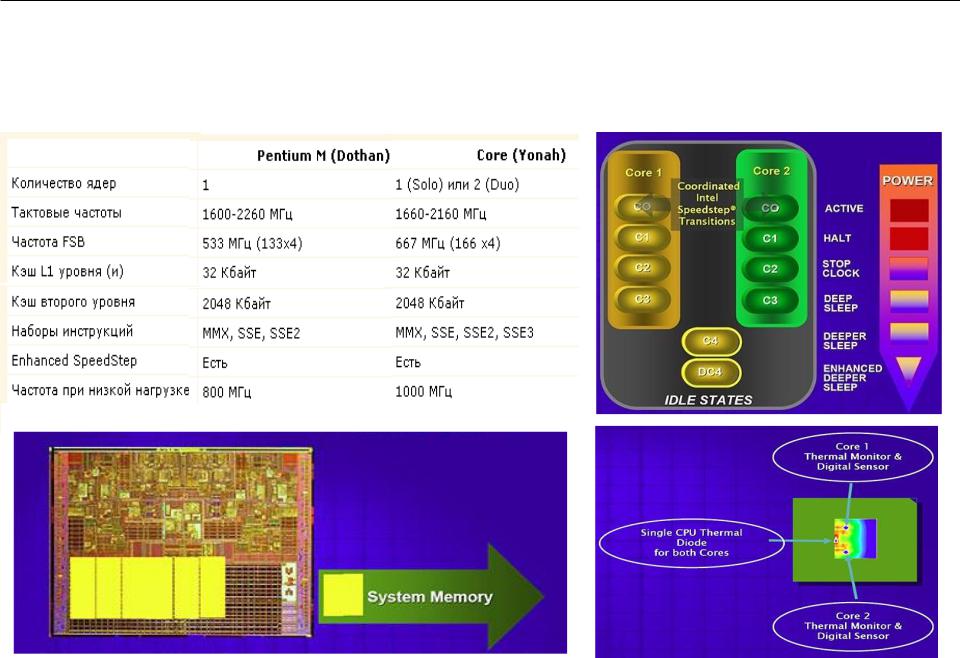

Мобильные процессоры Pentium M и Centrino Duo

Dynamic Power Coordination

Dynamic Cache Sizing