ТСвИС / архитектура вычислительных систем. arebook

.pdf

x0

x1

x2

x3

35

&

&

1

F

&

&

1 1

a1 a0

Рис.2.9. Схемная реализация мультиплексора

36

x0 |

MUX |

|

x1 |

4 - 1 |

|

|

|

|

x2 |

|

|

x3 |

|

F |

а0 |

|

|

а1 |

|

|

|

|

|

Рис.2.10. Условное обозначение мультиплексора

|

________ |

|

______ |

_ |

_ |

ri = ai bi = ai bi ai-bi , |

||

|

|

_ |

признаком «больше» - функция ri = ai |

bi , признаком «меньше» - |

|

функция ri = ai bi . |

|

|

Логические функции, выражающие отношения равенства,

«больше» и «меньше» между |

n-разрядными числами a и b, |

||

можно записать следующим образом: |

|

||

_____________ |

_____________ |

||

_ |

_ |

_ |

_ |

Fa = b = (an-1bn-1 an-1bn-1) (an-2bn-2 an-2bn-2) F'a = b |

|||

_ |

_ |

|

|

Fa > b = an-1bn-1 rn-1an-2bn-2 F'a > b

37

_ _

Fa < b = an-1bn-1 rn-1an-2bn-2 F'a < b

38

Настраиваемые значения логической функции

F(0)

F(1)

F(2)

F(2 n-1)

x0

x1

x2

xn-1

.

.

.

.

.

.

x0

x1

x2

.

.

.

xm-1

а0 а1 a2

.

.

.

an-1

MUX 2 n - 1

F

Аргументы логической функции

Рис.2.11. Схема использования мультиплексора в качестве УЛМ

39

x |

EN |

DMX |

|

|

|

|

0 |

|

|

|

|

|

F0 |

|

a0 |

1 |

|

1 |

F1 |

|

|

|

||

|

|

|

2 |

F2 |

|

|

|

|

|

a1 |

2 |

|

3 |

F3 |

|

|

|

||

|

|

|

|

|

Рис.2.13. Условное обозначение дешифраторадемультиплексора

Штрихами помечены функции отношений по младшим разрядам слов.

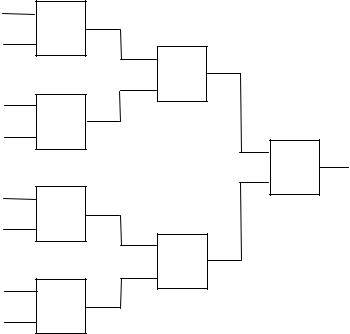

Схемная реализация компаратора в соответствии с приведенными выше формулами представлена на рис.2.13.

Схема сдвига сдвигает код на один разряд влево или вправо в зависимости от заданного сигнала управления С=0 или С=1, соответственно. Пример реализации схемы для случая четырех входных битов приведен на рис.2.14.

40

an -1

bn--1

an -2

bn -2

1 |

& |

|

|

|

|

|

1 |

Fa < b |

|

|

|

|

||

|

|

1 |

rn -1 |

|

|

|

& |

|

|

|

|

|

|

|

1 |

& |

|

|

|

|

|

|

|

|

|

|

|

1 |

Fa > b |

1 |

& |

|

|

|

|

|

|

|

|

|

|

1 |

|

|

1 |

& |

|

& |

|

|

|

|

||

|

|

rn -2 |

|

|

F'a<b |

& |

|

|

|

|

|

|

|

F'a>b |

& |

|

|

|

Fa = b |

|

|

|

F'a=b |

& |

Рис.2.13. Схемная реализация компаратора

41

x0 |

x1 |

x2 |

x3 |

С

1

& |

|

& |

|

& |

|

& |

|

& |

|

& |

|

|

|

|

|

|

|

|

|

|

|

1 |

|

1 |

|

|

|

y0 |

y1 |

y2 |

y3 |

2.14. Схема сдвига

42

Схема контроля четности выполняет функцию проверки поступающего на ее n входов двоичного кода xn-1 xn-2 … x0 на присутствие в нем четного (нечетного) числа единиц. Схема реализует сумматор по модулю 2 битов входного кода, формируя на выходе «1», если число единиц во входном коде нечетное, и «0», если число единиц четное.

Реализация восьмивходовой схемы контроля четности на базе XOR-элементов представлена на рис.2.15. XOR-элемент, обозначаемый символом «=1», в свою очередь может быть построен по схеме, обведенной пунктиром на рис.2.13 (с исключением инверсии на выходе).

Сумматор осуществляет арифметическое сложение двух целых чисел. Накапливающий сумматор поданное на его вход число суммирует к хранящемуся в его памяти предыдущему результату. Комбинационный сумматор не имеет памяти и формирует на выходе результат сложения поданных на его вход двух чисел.

Многоразрядный комбинационный сумматор складывается из одноразрядных сумматоров. Одноразрядный комбинационный сумматор имеет три входа ai , bi (соответствующие разряды складываемых чисел), pi-1 (сигнал переноса из соседнего младшего разряда) и два выхода si (соответствующий разряд суммы), pi (сигнал переноса в соседний старший разряд). Соотношение значений входных и выходных сигналов описываются таблицей истинности, представленной на рис.2.16.

По таблице истинности легко построить логические

функции для выходов сумматора: |

|

||

_ |

_ |

|

_ |

pi = ai bi pi-1 ai bi pi-1 ai bi pi-1 ai bi pi-1 = |

|||

|

_ |

_ |

_ |

= pi-1 ( ai bi ai |

bi ) ai bi ( pi-1 pi-1) = |

||

43

= pi-1( ai bi) ai bi |

|

|

|

_ _ |

_ |

_ |

_ _ |

si = ai bi pi-1 ai bi pi-1 ai bi pi-1 ai bi pi-1 = |

|||

_ |

_ |

_ |

_ _ |

= ai ( bi pi-1 bi pi-1) ai (bi pi-1 bi pi-1) = |

|||

_ |

|

|

______ |

= ai (bi pi-1) ai (bi pi-1) = ai bi pi-1

x7

x6

x5

x4

x3

x2

x1

x0

44

=1

=1

=1

=1

F

=1

=1

=1

Рис.2.15. Схема контроля четности