- •Твердотільна електроніка

- •Передмова

- •1 Елементи фізики напівпровідників та електронно-діркових переходів

- •1.1 Загальні відомості про напівпровідники

- •1.1.1 Власна електропровідність напівпровідників

- •1.1.2 Електронна провідність напівпровідників

- •1.1.3 Діркова провідність напівпровідників

- •1.1.4 Рекомбінація носіїв заряду та тривалість їх життя

- •1.1.5 Види струмів у напівпровідниках

- •1.2 Електронно - дірковий перехід та фізичні процеси в ньому

- •Пряме включення переходу

- •Зворотне включення переходу

- •1.2.4 Теоретична вольт-амперна характеристика

- •1.2.5 Параметри переходу

- •Товщина переходу

- •Ємності переходу

- •1.2.6 Реальна вах переходу

- •Пряма гілка вах

- •Зворотна гілка вах

- •1.3 Різновиди електричних переходів та контактів

- •1.3.1 Гетеропереходи

- •1.3.4 Контакти металу з напівпровідниками

- •1.3.5 Омічні контакти

- •2 Напівпровідникові діоди

- •2.1 Класифікація та система позначень діодів

- •2.2 Випрямні діоди

- •Параметри випрямних діодів

- •2.3 Напівпровідникові стабілітрони

- •2.4 Універсальні діоди

- •2.5 Імпульсні діоди та перехідні процеси в них

- •2.6 Тунельні та обернені діоди

- •2.7 Варикапи

- •2.8 Діоди Шотткі

- •3 Біполярні транзистори

- •3.1 Будова та принцип дії біполярних транзисторів

- •3.1.1 Загальні відомості про біполярні транзистори

- •Класифікація транзисторів

- •Система позначень бт

- •Будова сплавних транзисторів

- •3.1.2 Способи вмикання й режими роботи біполярних транзисторів

- •3.1.3 Принцип дії біполярного транзистора в активному режимі

- •3.1.4 Вплив конструкції та режиму роботи транзистора на h21б

- •3.1.5 Схема вмикання транзистора зі спільним емітером та спільним колектором

- •3.1.6 Модель Еберса-Молла

- •3.2 Статичні характеристики і параметри біполярних транзисторів

- •3.2.1 Статичні характеристики біполярного транзистора у схемі зі спільною базою

- •Вхідні характеристики

- •Вихідні характеристики

- •Характеристики прямої передачі

- •Характеристики зворотного зв’язку

- •3.2.2 Статичні характеристики біполярного транзистора у схемі зі спільним емітером

- •Вхідні характеристики

- •Вихідні характеристики

- •Характеристики прямої передачі

- •Характеристики зворотного зв’язку

- •3.2.3 Статичні характеристики біполярного транзистора у схемі зі спільним коллектором

- •3.2.4 Вплив температури на статичні характеристики транзисторів

- •3.2.5 Граничні режими транзистора

- •Пробої транзистора

- •Максимально допустима потужність, що розсіюється колектором

- •3.2.6 Диференціальні параметри біполярного транзистора

- •Зв'язок між h-параметрами для різних схем увімкнення бт

- •3.2.7 Фізичні параметри та еквівалентні схеми біполярних транзисторів

- •3.3 Робота біполярного транзистора у динамічному режимі

- •3.3.1 Принцип дії підсилювального каскаду на біполярному транзисторі

- •3.3.2 Способи забезпечення режиму спокою транзисторного каскаду

- •Емітерному колі

- •Оцінка транзисторних каскадів з точки зору температурної нестабільності

- •3.3.3 Динамічні характеристики біполярного транзистора та їх використання

- •Вихідна навантажувальна характеристика

- •Вхідна навантажувальна характеристика

- •Параметри режиму підсилення та їх розрахунок за динамічними характеристиками транзисторного каскаду

- •3.3.4 Частотні властивості біполярних транзисторів

- •Вплив ємностей переходів і розподіленого опору бази на частотні властивості транзистора

- •3.3.5 Робота біполярного транзистора у ключовому режимі

- •3.4 Деякі різновиди біполярних транзисторів

- •3.4.1 Одноперехідний транзистор

- •3.4.2 Високочастотні малопотужні транзистори

- •3.4.3 Потужні транзистори

- •4 Польові транзистори

- •4.1 Польові транзистори з керувальним переходом

- •Статичні вхідні характеристики

- •Статичні прохідні (стокозатворні) характеристики

- •Статичні вихідні (стокові) характеристики

- •Диференціальні параметри польових транзисторів

- •4.2 Польові транзистори з ізольованим затвором (мдн - транзистори)

- •4.2.1 Ефект поля

- •4.3 Залежність характеристик і параметрів польових транзисторів від температури

- •4.4 Динамічний режим роботи польових транзисторів

- •4.4.1 Каскад на польовому транзисторі: розрахунок у статиці та динаміці

- •4.4.2 Частотні властивості польових транзисторів

- •4.5 Потужні польові транзистори

- •Потужні мдн – транзистори

- •Транзистори зі статичною індукцією

- •4.6 Польові прилади із зарядовим зв’язком

- •5 Тиристори

- •5.1 Будова, принцип дії та режими роботи тиристора

- •5.1.1 Загальні відомості

- •5.1.2 Диністорний режим

- •5.1.3 Триністорний режим

- •5.1.4 Симістори

- •5.2 Способи комутації тиристорів

- •5.2.1 Увімкнення тиристорів

- •Увімкнення за допомогою струму керування

- •Увімкнення тиристора за допомогою імпульсу анодної напруги

- •5.2.2 Вимкнення тиристорів

- •Вимкнення за допомогою подачі напруги на керувальний електрод (за допомогою струму керування)

- •5.3 Біполярні транзистори з ізольованим затвором

- •6 Оптоелектронні напівпровідникові прилади

- •6.1 Загальні відомості

- •6.2 Випромінювальні діоди

- •6.3 Напівпровідникові фотоприймачі

- •6.3.1 Фоторезистори

- •6.3.2 Фотодіоди

- •6.3.3 Фотоприймачі з внутрішнім підсиленням

- •6.4 Оптрони та їх застосування

- •7 Основи мікроелектроніки

- •7.1 Основні поняття і визначення

- •Історична довідка

- •7.2 Гібридні інтегральні схеми

- •7.3 Напівпровідникові інтегральні схеми

- •7.3.1 Технологія

- •Планарно-дифузійна технологія виготовлення біполярних напівпровідникових інтегральних схем

- •7.3.2 Технологія виготовлення інтегральних

- •Ізоляція

- •7.3.3 Біполярні транзистори

- •Багатоемітерні транзистори

- •Супербета - транзистори

- •Біполярні транзистори з бар'єром Шотткі

- •7.3.4 Мон (мдн)- транзистори

- •7.3.6 Резистори

- •7.3.7 Конденсатори

- •7.4 Інтегральні схеми з інжекційним живленням

- •Позначення основних величин

- •Список літератури

- •1.1.4 Рекомбінація носіїв заряду та тривалість їх життя 11

- •1.2.4 Теоретична вольт-амперна характеристика p-nпереходу 28

- •1.2.5 Параметри переходу 30

- •3 Біполярні транзистори 69

- •3.1 Будова та принцип дії біполярних транзисторів 69

- •3.1.1 Загальні відомості про біполярні транзистори 69

- •6 Оптоелектронні напівпровідникові

- •Твердотільна електронікА

7.3 Напівпровідникові інтегральні схеми

7.3.1 Технологія

Напівпровідникова (монолітна, твердотіла) технологія більш придатна для масового виробництва ІС з високим ступенем інтеграції, характеристики яких не критичні щодо розкиду параметрів пасивних елементів, їх температурної нестабільності і впливу паразитних зв'язків. За напівпровідниковою технологією виготовляється більшість цифрових інтегральних схем і багатофункціональних аналогових ІС. Надійність напівпровідникових мікросхем значно вища, ніж у гібридних ІС, внаслідок невеликої кількості припаювань.

Усі елементи напівпровідникових ІС виконані всередині напівпровідникового кристала – чіпа. Товщина чіпа – 200-300 мкм, горизонтальні розміри – від 1,5 х 1,5 мм до 6,0 х 6,0 мм.

Планарно-дифузійна технологія виготовлення біполярних напівпровідникових інтегральних схем

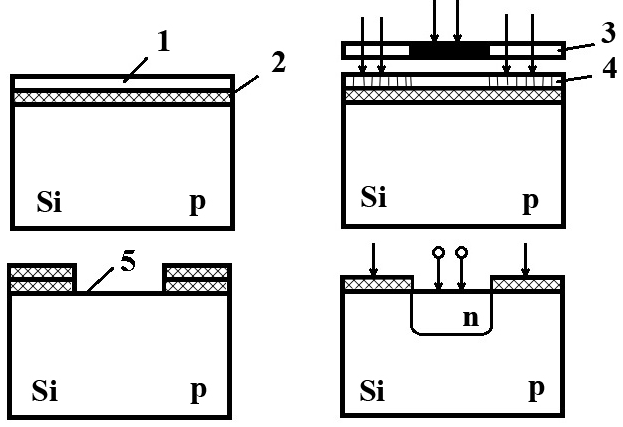

На кремнієвому кристалі (рис. 7.8) створюється тонкий шар двоокису SiO2. На нього наноситься шар 1 фоторезиста. Це речовина, яка під дією опромінення стає кислотостійкою. Фоторезист опромінюється ультрафіолетовими променями через фотошаблон 3 (фотопластинка з відповідним рисунком із прозорих і непрозорих ділянок). Опромінені ділянки 5 витравлюються кислотою. Цей процес називається фотолітографією. На ділянках 5 утворюються вікна, через які здійснюється процес дифузії донорних атомів із нагрітого газу 6.

Рисунок 7.8 – Технологія виготовлення біполярних структур ІС

Таким чином, у кремнієвому кристалі формуються n – області (так звані «кишені»), які відповідають емітерам усієї сукупності біполярних транзисторів цієї ІС. При повторенні операцій послідовно формуються області бази, потім колектора. Паралельно формуються пасивні елементи, а на поверхні кристала – міжз'єднання і контактні площадки.

Ця планарно-дифузійна технологія має такі недоліки:

нерівномірний розподіл домішок у областях;

нерівномірний опір колектора і збільшення його значення;

відсутні чіткі межі переходів, що призводить до зменшення напруги пробою між колектором і підкладкою;

підкладка дуже впливає на електричні параметри транзистора ІС.

Натомість біполярні інтегральні транзистори, виготовлені за планарно-епітаксійною технологією, відзначаються рівномірним розподілом домішок (рис. 7.9).

Рисунок 7.9 – Планарно-епітаксійна біполярна структура

У них на p-підкладці вирощується колектор n - типу. Для зменшення опору колектора, а отже, зниження втрат потужності і ступеня впливу підкладки створюють прихований n+- шар, який має менший порівняно з епітаксійним n - шаром опір. Цей прихований шар створюється за допомогою додаткової дифузії донорних домішок у відповідні ділянки підкладки.

7.3.2 Технологія виготовлення інтегральних

МДН- структур

Послідовність операцій цієї технології показана на рис. 7.10. Виконується товстий (до 1,5 мкм) шар окису кремнію SiO2 (а); за допомогою фотолітографії витравляється «вікно» (б); це вікно покривається тонким шаром SiO2 (0,2 мкм) (в); потім уся пластина покривається шаром матеріалу затвора (алюміній, хром, молібден) (г); за допомогою фотолітографії залишається шар металу тільки над тією областю, де буде затвор (д); шляхом дифузії та іонного легування створюються p+- області витоку і стоку (причому електрод затвора служить маскою) (е).

Рисунок 7.10 – Технологія виготовлення МОН (МДН) - структур