- •Предисловие

- •Глава 1. Общие сведения о микропроцессорах

- •1.1 Классификация микропроцессоров

- •1.2 Характеристики микропроцессоров

- •1.2.1 Тактовая частота

- •1.2.2 Архитектура процессора

- •1.2.3 Технологический процесс производства

- •1.2.4 Частота системной шины

- •1.2.5 Размер кэша

- •1.3 Типы архитектур микропроцессоров

- •1.4 Структурная схема микропроцессоров

- •1.4.1 Микропроцессор Фон-Неймана

- •1.4.2 Конвейер

- •1.4.3 Зависимость между частотой и количеством ступеней конвейера

- •1.5 Представление информации в эвм

- •1.5.1 Двоичное представление целых чисел

- •1.5.2 Представление символьной информации

- •Глава 2. Архитектура микропроцессоров ia-32

- •2.1 Состав и функции регистров

- •2.1.1 Основные регистры

- •2.1.2 Регистры дополнительных функциональных модулей

- •2.2 Типы адресации

- •2.3 Система команд

- •2.3.1 Классификация команд

- •2.3.2 Формат команды

- •2.3.3 Однобайтовые команды

- •2.3.4 Непосредственно заданные операнды

- •2.3.5 Команды с регистровыми операндами

- •2.3.7 Команды с операндами, расположенными в памяти

- •Глава 3. Организация многоуровневой памяти

- •3.1 Принцип построения многоуровневой памяти

- •3.2 Организация кэш-памяти

- •3.3 Протоколы когерентности памяти микропроцессоров

- •3.4 Страничная организация памяти

- •Глава 4. Режимы работы процессоров ia-32

- •4.1 Обзор режимов работы

- •4.2 Реальный режим адресации

- •4.3 Защищённый режим

- •4.3.1 Дескрипторные таблицы

- •4.3.2 Дескрипторные регистры

- •4.3.3 Дескриптор

- •4.3.4 Односегментная модель памяти

- •4.3.5 Многосегментная модель памяти

- •Глава 5. Страничная организация памяти в процессорах ia‑32

- •5.1 Каталог страниц

- •5.2 Таблица страниц

- •5.3 Страничная переадресация

- •5.4 Диспетчер виртуальных машин системы Microsoft Windows

- •Глава 6. Архитектура процессоров с параллелизмом уровня команд

- •6.1 Подходы к использованию ресурса транзисторов в микропроцессорах

- •6.2 Суперскалярные процессоры и процессоры с длинным командным словом

- •6.3 Зависимости между командами, препятствующие их параллельному исполнению

- •6.4 Предварительная выборка команд и предсказание переходов

- •6.5 Условное выполнение команд в vliw-процессорах

- •6.6 Декодирование команд, переименование ресурсов и диспетчеризация

- •6.7 Исполнение команд

- •6.8 Завершение выполнения команды

- •6.9 Направления развития архитектуры процессоров с параллелизмом уровня команд

- •Глава 7. Мультитредовые микропроцессоры

- •7.1 Основы мультитредовой архитектуры

- •7.2 Выявление тредов

- •7.3 Мультитредовые процессоры с тредами, выявляемыми путем анализа потоков управления программы

- •7.3.1 Мультитредовая модель выполнения программы

- •7.3.2 Мультитредовые программы

- •7.3.3 Аппаратные средства мультитредовой архитектуры

- •7.3.4 Преимущества мультитредовой архитектуры

- •7.4 Мультитредовые процессоры с тредами, выявляемыми путем анализа потоков данных программы

- •7.5 Специфика мультитредовых моделей распараллеливания

- •Глава 8. Модуль обработки вещественных чисел

- •8.1 Представление чисел с плавающей запятой

- •8.2 Состав модуля fpu

- •Глава 9. Основы 64-разрядной архитектуры

- •9.1 Состав и назначение регистров микропроцессора ia-64

- •9.2 Особенности архитектуры epic

- •9.3 Архитектура x86-64

- •9.4 Структура одноядерного процессора

- •9.5 Многоядерные процессоры

- •9.6 Зачем нужны “лишние” разряды?

- •Глава 10. Современные 64-разрядные микропроцессоры корпораций Intel и amd

- •10.1 Архитектура Intel Core 2

- •10.1.1 Intel Wide Dynamic Execution

- •10.1.2 Intel Intelligent Power Capability

- •10.1.3 Intel Advanced Smart Cache

- •10.1.4 Intel Smart Memory Access

- •10.1.5 Intel Advanced Digital Media Boost

- •10.1.6 Логическая схема процессора

- •10.2 Архитектура Intel Core i7

- •10.2.1 Технология Hyper-Threading в архитектуре Nehalem

- •10.2.2 Иерархия кэш-памяти в архитектуре Nehalem

- •10.3 Хронология развития семейств микропроцессоров с архитектурой Nehalem

- •10.4 Архитектура amd Athlon 64

- •10.4.1 Ядро процессора

- •10.4.3 Контроллер памяти

- •10.4.4 Контроллер HyperTransport

- •10.5 Архитектура amd k10

- •10.4.1 Технология amd Memory Optimizer Technology

- •10.5.2 Ядро процессора

- •10.5.3 Предвыборка данных и инструкций

- •10.5.4 Выборка из кэша

- •10.5.5 Предсказание переходов и ветвлений

- •10.5.6 Процесс декодирования

- •10.5.7 Диспетчеризация и переупорядочение микроопераций

- •10.5.8 Выполнение микроопераций

- •10.5.9 Технологии энергосбережения

- •10.5.10 Шина HyperTransport 3.0

- •10.5.11 Семейство процессоров Barcelona

- •10.5.12 Семейство процессоров Phenom

- •Глава 11. Технологии, поддерживаемые современными микропроцессорами

- •11.1 Технологии тепловой защиты

- •11.1.1 Технология Thermal Monitor

- •11.1.2 Технология Thermal Monitor 2

- •11.1.3 Режим аварийного отключения

- •11.2 Технологии энергосбережения

- •11.2.1 Технология Enhanced Intel SpeedStep

- •11.2.2 Технология Cool'n'Quiet

- •11.3 Технология расширенной памяти

- •11.4 Технология антивирусной защиты

- •11.5 Технология виртуализации

- •11.6 Реализация технологий в современных микроархитектурах

- •11.6.2 Em64t – NetBurst

- •11.6.3 Intel Core

- •11.6.4 Intel Atom

- •11.6.5 Nehalem

- •11.6.6 Xeon

- •Глава 12. Графические микропроцессоры

- •12.1 Основные термины и определения

- •12.2 Технологии построения трёхмерного изображения

- •12.2.1 Технологии повышения реалистичности трехмерного изображения

- •12.3 Шейдерный процессор

- •12.4 Особенности современных графических процессоров

- •Глава 13. Однокристальные микроконтроллеры

- •13.1 Общая характеристика микроконтроллеров

- •13.2 Микроконтроллеры семейства avr

- •Почему именно avr?

- •13.3 Общие сведения об омк avr

- •13.4 Характеристики avr-микроконтроллеров

- •Глава 14. Технология производства микропроцессоров

- •14.1 Особенности производства процессоров

- •14.2 Новые технологические решения

- •14.3 Технология производства сверхбольших интегральных схем

- •I. Выращивание кристалла кремния

- •II. Создание проводящих областей

- •III. Тестирование

- •IV. Изготовление корпуса

- •V. Доставка

- •14.4 Перспективы производства сбис

- •Англо-русский словарь терминов и аббревиатур

- •Библиографический список

- •Интернет-ссылки

- •350072. Краснодар, ул. Московская, 2, кор. А.

4.3.2 Дескрипторные регистры

GDTR (Global Descriptor Table Register – регистр глобальной дескрипторной таблицы) – специальный 48-битный регистр, который описывает местоположение и размер таблицы, содержащей дескрипторы. Он появился вместе с механизмом защиты в 80286 моделях процессоров как сегментный механизм защиты.

Регистр содержит два поля: первое поле – первые 32 бита, описывают физический адрес, по которому должна быть расположена дескрипторная таблица, а последние 16 бит – лимит, ограничение, которое накладывается на верхний дескриптор. Каждый дескриптор занимает в памяти по 8 байт, потому лимит всегда должен вычисляться так: limit = 8n ‑ 1, где n – количество дескрипторов.

При инициализации операционной системы глобальная дескрипторная таблица обычно создаётся на полное количество дескрипторов (limit = 65535), или 8192 дескрипторов. Затем вычисляется физический адрес начала таблицы, и загружается регистр GDTR специальной ассемблерной инструкцией LGDT (Load GDT):

mov AX, GDT_Limit

push AX

mov EAX, GDT_Base

push EAX

mov BP, SP

LGDT qword [SS:BP] ; Не забывайте, что стек растёт “вниз”!

После включения механизма защиты начинает действовать селекторная система адресации, вместо сегментной, и использоваться GDT.

LDTR (Local Descriptor Table Register – регистр локальной таблицы дескрипторов) – специальный 16-битный регистр, содержащий селектор сегмента LDT. Расположение в памяти и размер определяются соответствующими полями дескриптора. В настоящее время LDT используются только для выполнения 16-разрядных приложений.

Загрузка регистра LDTR осуществляется привилегированной командой LLDT (Load LDT):

LLDT word LDT_Seg

На 64-разрядных процессорах программы выполняются только в режиме памяти flat. Поэтому LDT не поддерживаются вовсе.

4.3.3 Дескриптор

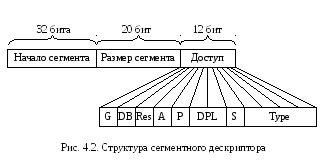

Дескриптор несёт в себе полную информацию о сегменте: местоположение, уровень доступа, размер, принадлежность и т.д. Длина дескриптора равна восьми байтам. По информации, находящейся в дескрипторе, операционная система определяет линейные адреса сегментов программы. Структура дескриптора изображена на рисунке 4.2.

Биты поля доступа имеют следующий смысл:

Флаг гранулярности G определяет размер гранул, составляющих сегмент: при G=0 размер гранулы равен значению соответствующего поля в дескрипторе, а при G=1 размер гранулы равен полю дескриптора, умноженному на (212 = 4096). Таким образом, при G=0 максимальный размер сегмента 1 Мб, а при G=1 максимальный размер сегмента 4 Гб.

Флаг разрядности DB актуален для пользовательских сегментов кода и стека. Определяет разрядность сегмента в 16 бит при нулевом и 32 бит при единичном значении.

Зарезервированный флаг Res должен всегда равняться нулю.

Пользовательский флаг A отдан операционной системе. Его состояние никак не влияет на работу с сегментом.

Бит P определяет доступность сегмента (0 – сегмента нет, 1 – есть). При обращении к сегменту со сброшенным битом P происходит исключение #NP, обработчик которого может загрузить/создать сегмент.

Номер привилегий DPL содержит 2-битный номер (от 0 до 3), определяющий, к какому уровню (кольцу) защиты относится этот сегмент.

Тип сегмента определяется пятью битами. Из них старший бит (S) определяет сегмент как системный (S=0) или пользовательский (S=1). Значение остальных бит Type для системных и пользовательских сегментов описано в таблицах 4.1 и 4.2.

Младший бит байта AR пользовательских сегментов (A – Accessed,) можно использовать для сбора статистики о сегменте. При первом же обращении к сегменту (чтение, запись, выполнение) он устанавливается процессором в 1.

Таблица 4.1. Типы системных сегментов

|

Типы системных сегментов (при S=0) | ||||

|

Биты AR |

Описание | |||

|

3 |

2 |

1 |

0 | |

|

0 |

0 |

0 |

0 |

Зарезервировано |

|

0 |

0 |

0 |

1 |

Свободный 16-битный TSS |

|

0 |

0 |

1 |

0 |

LDT |

|

0 |

0 |

1 |

1 |

Занятый 16-битный TSS |

|

0 |

1 |

0 |

0 |

16-битный шлюз вызова |

|

0 |

1 |

0 |

1 |

Шлюз задачи |

|

0 |

1 |

1 |

0 |

16-битный шлюз прерывания |

|

0 |

1 |

1 |

1 |

16-битный шлюз ловушки |

|

1 |

0 |

0 |

0 |

Зарезервировано |

|

1 |

0 |

0 |

1 |

Свободный 32-битный TSS |

|

1 |

0 |

1 |

0 |

Зарезервировано |

|

1 |

0 |

1 |

1 |

Занятый 32-битный TSS |

|

1 |

1 |

0 |

0 |

32-битный шлюз вызова |

|

1 |

1 |

0 |

1 |

Зарезервировано |

|

1 |

1 |

1 |

0 |

32-битный шлюз прерывания |

|

1 |

1 |

1 |

1 |

32-битный шлюз ловушки |

Таблица 4.2. Типы пользовательских сегментов

|

Биты AR |

Описание | ||

|

3 |

2 |

1 | |

|

0 |

0 |

0 |

Сегмент данных только для чтения |

|

0 |

0 |

1 |

Сегмент данных для чтения/записи |

|

0 |

1 |

0 |

Сегмент данных только для чтения, растёт вниз |

|

0 |

1 |

1 |

Сегмент данных для чтения/записи, растёт вниз |

|

1 |

0 |

0 |

Сегмент кода только для выполнения |

|

1 |

0 |

1 |

Сегмент кода для выполнения/чтения |

|

1 |

1 |

0 |

Подчинённый сегмент кода только для выполнения |

|

1 |

1 |

1 |

Подчинённый сегмент кода для выполнения/чтения |