- •Предисловие

- •Глава 1. Общие сведения о микропроцессорах

- •1.1 Классификация микропроцессоров

- •1.2 Характеристики микропроцессоров

- •1.2.1 Тактовая частота

- •1.2.2 Архитектура процессора

- •1.2.3 Технологический процесс производства

- •1.2.4 Частота системной шины

- •1.2.5 Размер кэша

- •1.3 Типы архитектур микропроцессоров

- •1.4 Структурная схема микропроцессоров

- •1.4.1 Микропроцессор Фон-Неймана

- •1.4.2 Конвейер

- •1.4.3 Зависимость между частотой и количеством ступеней конвейера

- •1.5 Представление информации в эвм

- •1.5.1 Двоичное представление целых чисел

- •1.5.2 Представление символьной информации

- •Глава 2. Архитектура микропроцессоров ia-32

- •2.1 Состав и функции регистров

- •2.1.1 Основные регистры

- •2.1.2 Регистры дополнительных функциональных модулей

- •2.2 Типы адресации

- •2.3 Система команд

- •2.3.1 Классификация команд

- •2.3.2 Формат команды

- •2.3.3 Однобайтовые команды

- •2.3.4 Непосредственно заданные операнды

- •2.3.5 Команды с регистровыми операндами

- •2.3.7 Команды с операндами, расположенными в памяти

- •Глава 3. Организация многоуровневой памяти

- •3.1 Принцип построения многоуровневой памяти

- •3.2 Организация кэш-памяти

- •3.3 Протоколы когерентности памяти микропроцессоров

- •3.4 Страничная организация памяти

- •Глава 4. Режимы работы процессоров ia-32

- •4.1 Обзор режимов работы

- •4.2 Реальный режим адресации

- •4.3 Защищённый режим

- •4.3.1 Дескрипторные таблицы

- •4.3.2 Дескрипторные регистры

- •4.3.3 Дескриптор

- •4.3.4 Односегментная модель памяти

- •4.3.5 Многосегментная модель памяти

- •Глава 5. Страничная организация памяти в процессорах ia‑32

- •5.1 Каталог страниц

- •5.2 Таблица страниц

- •5.3 Страничная переадресация

- •5.4 Диспетчер виртуальных машин системы Microsoft Windows

- •Глава 6. Архитектура процессоров с параллелизмом уровня команд

- •6.1 Подходы к использованию ресурса транзисторов в микропроцессорах

- •6.2 Суперскалярные процессоры и процессоры с длинным командным словом

- •6.3 Зависимости между командами, препятствующие их параллельному исполнению

- •6.4 Предварительная выборка команд и предсказание переходов

- •6.5 Условное выполнение команд в vliw-процессорах

- •6.6 Декодирование команд, переименование ресурсов и диспетчеризация

- •6.7 Исполнение команд

- •6.8 Завершение выполнения команды

- •6.9 Направления развития архитектуры процессоров с параллелизмом уровня команд

- •Глава 7. Мультитредовые микропроцессоры

- •7.1 Основы мультитредовой архитектуры

- •7.2 Выявление тредов

- •7.3 Мультитредовые процессоры с тредами, выявляемыми путем анализа потоков управления программы

- •7.3.1 Мультитредовая модель выполнения программы

- •7.3.2 Мультитредовые программы

- •7.3.3 Аппаратные средства мультитредовой архитектуры

- •7.3.4 Преимущества мультитредовой архитектуры

- •7.4 Мультитредовые процессоры с тредами, выявляемыми путем анализа потоков данных программы

- •7.5 Специфика мультитредовых моделей распараллеливания

- •Глава 8. Модуль обработки вещественных чисел

- •8.1 Представление чисел с плавающей запятой

- •8.2 Состав модуля fpu

- •Глава 9. Основы 64-разрядной архитектуры

- •9.1 Состав и назначение регистров микропроцессора ia-64

- •9.2 Особенности архитектуры epic

- •9.3 Архитектура x86-64

- •9.4 Структура одноядерного процессора

- •9.5 Многоядерные процессоры

- •9.6 Зачем нужны “лишние” разряды?

- •Глава 10. Современные 64-разрядные микропроцессоры корпораций Intel и amd

- •10.1 Архитектура Intel Core 2

- •10.1.1 Intel Wide Dynamic Execution

- •10.1.2 Intel Intelligent Power Capability

- •10.1.3 Intel Advanced Smart Cache

- •10.1.4 Intel Smart Memory Access

- •10.1.5 Intel Advanced Digital Media Boost

- •10.1.6 Логическая схема процессора

- •10.2 Архитектура Intel Core i7

- •10.2.1 Технология Hyper-Threading в архитектуре Nehalem

- •10.2.2 Иерархия кэш-памяти в архитектуре Nehalem

- •10.3 Хронология развития семейств микропроцессоров с архитектурой Nehalem

- •10.4 Архитектура amd Athlon 64

- •10.4.1 Ядро процессора

- •10.4.3 Контроллер памяти

- •10.4.4 Контроллер HyperTransport

- •10.5 Архитектура amd k10

- •10.4.1 Технология amd Memory Optimizer Technology

- •10.5.2 Ядро процессора

- •10.5.3 Предвыборка данных и инструкций

- •10.5.4 Выборка из кэша

- •10.5.5 Предсказание переходов и ветвлений

- •10.5.6 Процесс декодирования

- •10.5.7 Диспетчеризация и переупорядочение микроопераций

- •10.5.8 Выполнение микроопераций

- •10.5.9 Технологии энергосбережения

- •10.5.10 Шина HyperTransport 3.0

- •10.5.11 Семейство процессоров Barcelona

- •10.5.12 Семейство процессоров Phenom

- •Глава 11. Технологии, поддерживаемые современными микропроцессорами

- •11.1 Технологии тепловой защиты

- •11.1.1 Технология Thermal Monitor

- •11.1.2 Технология Thermal Monitor 2

- •11.1.3 Режим аварийного отключения

- •11.2 Технологии энергосбережения

- •11.2.1 Технология Enhanced Intel SpeedStep

- •11.2.2 Технология Cool'n'Quiet

- •11.3 Технология расширенной памяти

- •11.4 Технология антивирусной защиты

- •11.5 Технология виртуализации

- •11.6 Реализация технологий в современных микроархитектурах

- •11.6.2 Em64t – NetBurst

- •11.6.3 Intel Core

- •11.6.4 Intel Atom

- •11.6.5 Nehalem

- •11.6.6 Xeon

- •Глава 12. Графические микропроцессоры

- •12.1 Основные термины и определения

- •12.2 Технологии построения трёхмерного изображения

- •12.2.1 Технологии повышения реалистичности трехмерного изображения

- •12.3 Шейдерный процессор

- •12.4 Особенности современных графических процессоров

- •Глава 13. Однокристальные микроконтроллеры

- •13.1 Общая характеристика микроконтроллеров

- •13.2 Микроконтроллеры семейства avr

- •Почему именно avr?

- •13.3 Общие сведения об омк avr

- •13.4 Характеристики avr-микроконтроллеров

- •Глава 14. Технология производства микропроцессоров

- •14.1 Особенности производства процессоров

- •14.2 Новые технологические решения

- •14.3 Технология производства сверхбольших интегральных схем

- •I. Выращивание кристалла кремния

- •II. Создание проводящих областей

- •III. Тестирование

- •IV. Изготовление корпуса

- •V. Доставка

- •14.4 Перспективы производства сбис

- •Англо-русский словарь терминов и аббревиатур

- •Библиографический список

- •Интернет-ссылки

- •350072. Краснодар, ул. Московская, 2, кор. А.

Глава 1. Общие сведения о микропроцессорах

1.1 Классификация микропроцессоров

МП – реализованное на одной или нескольких интегральных микросхемах устройство преобразования цифровой информации согласно программе, хранящейся в памяти.

По назначению МП разделяют на универсальные и специализированные.

Универсальными микропроцессорами являются МП общего назначения, которые решают широкий класс задач вычисления, обработки и управления. К универсальным относят МП компаний Intel и AMD.

Специализированные микропроцессоры предназначены для решения задач определенного класса. К специализированным МП относятся: сигнальные, медийные, мультимедийные МП и транспьютеры.

Сигнальные процессоры предназначены для цифровой обработки сигналов в реальном масштабе времени (например, для фильтрации сигналов, вычисления свертки, вычисления корреляционной функции, ограничения и преобразования сигнала, выполнения прямого и обратного преобразования Фурье). К сигнальным процессорам относятся процессоры компаний Texas Instruments TMS320C80, Analog Devices ADSP2106x, Motorola DSP560xx и DSP9600x.

Медийные и мультимедийные процессоры предназначены для обработки аудиосигналов, графической информации, видеоизображений, а также для решения ряда задач в мультимедиакомпьютерах, игровых приставках, бытовой технике. К медийным и мультимедийным процессорам относятся процессоры компаний MicroUnity Mediaprocessor, Philips ‑ Trimedia, Cromatic Reserch Mpact Media Engine, Nvidia NV1, Cyrix ‑ MediaGX.

Транспьютеры предназначены для организации массовых параллельных вычислений и работы в мультипроцессорных системах. Для них характерным является наличие внутренней памяти и встроенного межпроцессорного интерфейса, т. е. каналов связи с другими БИС МП. К транспьютерам относятся процессоры компании Inmos ‑ Т-2, Т-4, Т-8, Т9000.

По количеству интегральных микросхем различают однокристальные и секционные МП.

Однокристальный микропроцессор это конструктивно законченное изделие в виде одной СБИС. Другое название однокристальных МП микропроцессоры с фиксированной разрядностью данных. К этому типу относятся процессоры Intel Core i7; AMD К10; Cyrix 6x86; Digital Equipment Corporation Alpha 21364; Silicon Graphics – MIPS R10000; Motorola Power PC 620; Hewlett-Packard PA-8000; Sun Microsystems Ultra SPARC II.

Секционный микропроцессор – однокристальный МП малой разрядности, имеющий выводы для параллельного подключения дополнительных секционных микропроцессоров с целью наращивания разрядности. Другое название секционных МП – разрядно-модульные микропроцессоры или микропроцессоры с наращиваемой разрядностью. К этому типу можно отнести отечественные микропроцессоры К589ИК02 и К1804ВС1

По количеству процессорных ядер в СБИС различают одноядерные и многоядерные процессоры.

По составу функциональных блоков СБИС разделяют на микропроцессоры и микроконтроллеры. Однокристальный микроконтроллер (ОМК) в одном корпусе СБИС содержит все основные компоненты компьютера: МП, память команд и данных, таймеры, аналоговые и цифровые порты ввода/вывода, компараторы, АЦП, ЦАП и т.п. К таким микроконтроллерам относят ОМК компаний Intel – MCS-196,296; MicroChip – PIC; Mitsubishi Electric – M3820; Motorola – MC; Atmel – AVR; Bosch. ОМК используются при разработке встраиваемых систем управления цифровыми и аналоговыми техническими устройствами.

По способу управления различают МП со схемным и микропрограммным управлением. МП со схемным управлением имеют фиксированный набор команд, который не может изменяться потребителем. В МП с микропрограммным управлением систему команд разрабатывают при проектировании конкретного МПК на базе набора простейших микрокоманд с учётом класса решаемых задач.

По типу архитектуры различают МП с Принстонской (фоннеймановской) и гарвардской архитектурой.

По типу системы команд различают CICS-процессоры (Complete Instruction Set Computing) с полным набором команд и RISC-процессоры (Reduced Instruction Set Computing) с сокращённым набором команд.

По тактовой частоте и размеру кэш-памяти МП каждого производителя представляются широкой потребительской линейкой от дешёвых МП с низким быстродействием до дорогих МП с высоким быстродействием.

По разрядности МП делятся на три нижеописанных подкатегории. Разрядность – максимальное число одновременно обрабатываемых двоичных разрядов.

Разрядность внутренних регистров обуславливает диапазон целых чисел, которые могут храниться и обрабатываться в МП. Разрядность внутренних регистров МП в настоящее время достигает 32 и 64 бит.

разрядность шины данных определяет число одновременно передаваемых бит и тем самым обуславливает скорость передачи данных. Разрядность шины данных МП в настоящее время достигает 32 и 64 бит.

разрядность шины адреса определяет размер адресного пространства. Так как ШД и ША мультиплексируются в одну шину, то в настоящее время разрядность ША достигает 32 и 64 бит.

По размеру команд различают МП с одинаковым размером команд и с различным размером команд.

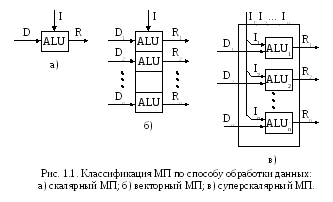

По способу обработки данных МП делятся на скалярные МП (SISD – single instruction single data), выполняющие одну команду над одним элементов данных (ОКОД – одна команда одно данное); векторные МП (SIMD – single instruction multiple data), выполняющие одну команду над вектором элементов данных (ОКМД – одна команда много данных) и суперскалярные МП (MIMD – multiple instructions multiple data), объединяющие несколько скалярных МП и выполняющие несколько команд над несколькими данных (МКМД – много команд много данных).

На рисунке 1.1 представлена классификация МП по способу обработки данных. Скалярный МП содержит одно арифметико-логическое устройство АЛУ (ALU – arithmetic logic unit), выполняющее одну команду Instruction над данными D. На выходе АЛУ скалярного процессора выставляется один результат R. Векторный МП состоит из нескольких идентичных АЛУ, которые в один момент времени выполняют одинаковую команду Instruction над различными данными D1, D2, …, Dn. Такой набор данных называют вектором. На выходе АЛУ векторного процессора выставляется вектор результатов R1, R2, …, Rn. Суперскалярный МП представляет собой совокупность скалярных процессоров и позволяет выполнять за один квант времени несколько различных команд I1, I 2,…, I n.

Многие МП попадают под разные классификационные признаки, поскольку способны решать задачи разных классов. Универсальные МП имеют мультимедийное расширение набора команд – Intel, AMD, Ultra-Sparc. В CISC-процессорах Intel реализовано ядро с RISC-архитектурой.