- •Objectives

- •Embedded Microcomputer Applications

- •Microcomputer and Microcontroller Architectures

- •Digital Hardware Concepts

- •Voltage, Current, and Resistance

- •Diodes

- •Transistors

- •Mechanical Switches

- •Transistor Switch ON

- •Transistor Switch OFF

- •The FET as a Logic Switch

- •NMOS Logic

- •CMOS Logic

- •Mixed MOS

- •Logic Symbols

- •Tri-State Logic

- •Timing Diagrams

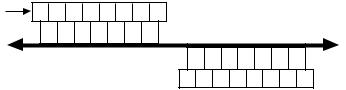

- •Multiplexed Bus

- •Loading and Noise Margin Analysis

- •The Design and Development Process

- •Chapter One Problems

- •2 Microcontroller Concepts

- •Organization: von Neumann vs. Harvard

- •Microprocessor/Microcontroller Basics

- •Microcontroller CPU, Memory, and I/O

- •Design Methodology

- •Introduction to the 8051 Architecture

- •Memory Organization

- •CPU Hardware

- •Oscillator and Timing Circuitry

- •The 8051 Microcontroller Instruction Set Summary

- •Direct and Register Addressing

- •Indirect Addressing

- •Immediate Addressing

- •Generic Address Modes and Instruction Formats

- •Address Modes

- •The Software Development Cycle

- •Software Development Tools

- •Chapter Two Problems

- •Timing Diagram Notation Conventions

- •Rise and Fall Times

- •Propagation Delays

- •Setup and Hold Time

- •Tri-State Bus Interfacing

- •Pulse Width and Clock Frequency

- •Fan-Out and Loading Analysis—DC and AC

- •Calculating Wiring Capacitance

- •Fan-Out When CMOS Drives LSTTL

- •Transmission Line Effects

- •Ground Bounce

- •Logic Family IC Characteristics and Interfacing

- •Interfacing TTL Compatible Signals to 5 Volt CMOS

- •Design Example: Noise Margin Analysis Spreadsheet

- •Worst-Case Timing Analysis Example

- •Chapter Three Review Problems

- •Memory Taxonomy

- •Secondary Memory

- •Sequential Access Memory

- •Direct Access Memory

- •Read/Write Memories

- •Read-Only Memory

- •Other Memory Types

- •JEDEC Memory Pin-Outs

- •Device Programmers

- •Memory Organization Considerations

- •Parametric Considerations

- •Asynchronous vs. Synchronous Memory

- •Error Detection and Correction

- •Error Sources

- •Confidence Checks

- •Memory Management

- •Cache Memory

- •Virtual Memory

- •CPU Control Lines for Memory Interfacing

- •Chapter Four Problems

- •Read and Write Operations

- •Address, Data, and Control Buses

- •Address Spaces and Decoding

- •Address Map

- •Chapter Five Problems

- •The Central Processing Unit (CPU)

- •External Data Memory Cycles

- •External Memory Data Memory Read

- •External Data Memory Write

- •Design Problem 1

- •Design Problem 2

- •Design Problem 3

- •Completing the Analysis

- •Chapter Six Problems

- •Memory Selection and Interfacing

- •Preliminary Timing Analysis

- •Introduction to Programmable Logic

- •Technologies: Fuse-Link, EPROM, EEPROM, and RAM Storage

- •PROM as PLD

- •Programmable Logic Arrays

- •PAL-Style PLDs

- •Design Examples

- •PLD Development Tools

- •Simple I/O Decoding and Interfacing Using PLDs

- •IC Design Using PCs

- •Chapter Seven Problems

- •Direct CPU I/O Interfacing

- •Port I/O for the 8051 Family

- •Output Current Limitations

- •Simple Input/Output Devices

- •Matrix Keyboard Input

- •Program-Controlled I/O Bus Interfacing

- •Real-Time Processing

- •Direct Memory Access (DMA)

- •Burst vs. Single Cycle DMA

- •Cycle Stealing

- •Elementary I/O Devices and Applications

- •Timing and Level Conversion Considerations

- •Level Conversion

- •Power Relays

- •Chapter Eight Problems

- •Interrupt Cycles

- •Software Interrupts

- •Hardware Interrupts

- •Interrupt Driven Program Elements

- •Critical Code Segments

- •Semaphores

- •Interrupt Processing Options

- •Level and Edge Triggered Interrupts

- •Vectored Interrupts

- •Non-Vectored Interrupts

- •Serial Interrupt Prioritization

- •Parallel Interrupt Prioritization

- •Construction Methods

- •10 Other Useful Stuff

- •Electromagnetic Compatibility

- •Electrostatic Discharge Effects

- •Fault Tolerance

- •Software Development Tools

- •Other Specialized Design Considerations

- •Thermal Analysis and Design

- •Battery Powered System Design Considerations

- •Processor Performance Metrics

- •Device Selection Process

- •Power and Ground Planes

- •Ground Problems

- •11 Other Interfaces

- •Analog Signal Conversion

- •Special Proprietary Synchronous Serial Interfaces

- •Unconventional Use of DRAM for Low Cost Data Storage

- •Digital Signal Processing / Digital Audio Recording

- •Detailed Checklist

- •Define Power Supply Requirements

- •Verify Voltage Level Compatibility

- •Check DC Fan-Out: Output Current Drive vs. Loading

- •Verify Worst Case Timing Conditions

- •Determine if Transmission Line Termination is Required

- •Clock Distribution

- •Power and Ground Distribution

- •Asynchronous Inputs

- •Guarantee Power-On Reset State

- •Programmable Logic Devices

- •Deactivate Interrupt and Other Requests on Power-Up

- •Electromagnetic Compatibility Issues

- •Manufacturing and Test Issues

- •Books

- •Web and FTP Sites

- •Periodicals: Subscription

- •Periodicals: Advertiser Supported Trade Magazines

- •Programming Microcontrollers in C, Second Edition

- •Controlling the World with Your PC

- •The Forrest Mims Engineers Notebook

- •The Forrest Mims Circuit Scrapbook, Volumes I and II

- •The Integrated Circuit Hobbyist’s Handbook

- •Simple, Low-Cost Electronics Projects

192EMBEDDED CONTROLLER

Hardware Design

in Figure 9-9. This is typical of a microcomputer bus with shared interrupt request signals on the bus, and for devices that are capable of generating multiple interrupts simultaneously. This is often implemented by connecting

multiple open-drain or open-collector,

IRQ1

active low requests to the interrupt request

IRQ to CPU line with a pull-up resistor. This allows

IRQ to CPU line with a pull-up resistor. This allows

multiple devices to use the same /IRQ line.

An edge triggered system would sense only one edge, and thus it may miss IRQ2 whereas a level sensitive system will respond to both. An example of this condition in the 8051 CPU is the serial I/O port interrupt. The “receive buffer full” and the “transmit buffer empty” signals are combined as shown above to a common level-sensitive internal interrupt request. If the receive buffer happened to be filled and the transmit buffer emptied at the same time, there would only be one edge, due to the overlapping requests. Thus, a level sensitive input is required to guarantee that both interrupt will be serviced.

Vectored Interrupts

In a vectored interrupt system, the interrupt request is accompanied by an identifier, referred to as a vector or interrupt vector number that defines the source of the interrupt. The vector is a pointer that is used as an index into a table known as the interrupt vector table. This table contains the addresses of the ISRs that are to be executed when the corresponding interrupts are processed. The 8051 CPU architecture does have separate interrupt vectors for different interrupts, but it does not have an interrupt vector table. Instead, each interrupt is assigned a separate absolute memory address that will generally contain a jump to the actual ISR to be executed.

In other processors with interrupt vector tables, when a vectored interrupt is processed, the CPU goes through the following sequence of events to begin execution of the ISR:

1.After acknowledging the interrupt, the CPU receives the vector number.

2.The CPU converts the vector into a memory address in the vector table.

3.The ISR address is fetched from the vector table and placed in the program counter.

193CHAPTER NINE

Other Interfaces and Bus Cycles

For example, when an external event occurs, the interrupting device activates the IRQ input to the interrupt controller that then requests an interrupt cycle from the CPU. When the CPU acknowledges the interrupt, the interrupt con troller passes the vector number to the CPU. The CPU converts the vector number to a memory address. This address points to the place in memory, which in turn contains the address of ISR.

Non-Vectored Interrupts

For systems with non-vectored interrupts, there is only one interrupt service routine entry point, and the ISR code must determine what caused the inter rupt if there are multiple interrupt sources in the system. When an interrupt occurs a call to a fixed location is executed, and that begins execution of the ISR. It is possible to have multiple interrupts pointing to the same ISR. The first act of such an ISR is to determine which interrupt occurred and branch to the appropriate handler. Serial I/O ports frequently have one vector for transmit and receive interrupts.

A typical microcontroller serial I/O port consists of a serial-in/parallel-out shift register for receiving serial input data, and a parallel-in/serial-out shift register for transmitting serial data, as shown in figure 9-10.

Serial to Parallel

Shift Register

Serial |

|

Data In |

CPU Data Bus |

|

Figure 9-10: Serial to parallel conversion interface.

Serial

Serial

Parallel to Serial Data Out Shift Register

When the last bit of serial data shifts into the receive register, the receive interrupt bit is set (the RI SFR bit in the 8051) to indicate that the receiver buffer is full and ready to be read by the CPU. Likewise, the transmit interrupt bit is set (the TI SFR bit in the 8051) to when transmit buffer is empty and ready to accept more data from the CPU.

194EMBEDDED CONTROLLER

Hardware Design

When multiple simultaneous interrupts occur, the processor must have some way of choosing which interrupt should be processed first. There are two common techniques for resolving the priority of simultaneous interrupts: serial and parallel.

Serial Interrupt Prioritization

When an interrupt occurs, the interrupting device lowers IEO and waits until IEI is high. Each device below it in line lowers its IEO. The device then per forms an interrupt cycle. When the ISR is complete an end of interrupt occurs, the interrupting device raises its IEO line, which propagates down the line. This is usually referred to as a daisy chain interrupt priority system. At any given time, the highest priority device in the chain will be serviced first. Figure 9-11 illustrates this process.

Logic

One

Highest |

|

|

|

|

|

|

|

|

|

Lowest |

|

|||

IEI IEO |

|

IEI IEO |

|

IEI IEO |

|

IEI IEO |

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IEI = Interrupt Enable Input

IEO = Interrupt Enable Output

Figure 9-11: Serial “daisy chain” interrupt prioritization.

Parallel Interrupt Prioritization

A parallel priority encoder can also be used to prioritize multiple simulta neous interrupt requests. The priority encoder encodes the highest priority active input as a binary value, and that value is used as part of the interrupt vector number. The interrupts could be prioritized using an encoder that is equivalent to a 74x148 style 8:3 line priority encoder.

In most machines, the CPU checks for interrupt requests just after execution of each instruction. When an interrupt is enabled and occurs, the CPU will:

1.Save the PC (program counter) on the stack.

2.Acknowledge the interrupt request and get the vector from interrupt source.

195CHAPTER NINE

Other Interfaces and Bus Cycles

3.Use the vector as an address or as a pointer into the interrupt vector table to fetch the address of the ISR from the vector table.

4.Load the address of ISR into the program counter.

5.CPU executes the ISR until return from interrupt execution at end of ISR.

6.Pop address off stack into program counter.

7.Continue execution where interrupt occurred.

The purpose of the interrupt processing sequence is to allow the processor to temporarily stop an executing program when an external event occurs, call the appropriate interrupt service routine to process the event, and then return to the interrupted program where it left off.

Interrupts provide a very efficient means for the processing of events that occur at unpredictable times with a minimum of delay. This is particularly important when there are a number of things that the processor must handle concurrently. Whole operating systems, usually referred to as real-time operating systems (RTOS), are designed to allow an application programmer to design multiple programs that can run concurrently on a single CPU almost as if they were running on separate processors.