- •Objectives

- •Embedded Microcomputer Applications

- •Microcomputer and Microcontroller Architectures

- •Digital Hardware Concepts

- •Voltage, Current, and Resistance

- •Diodes

- •Transistors

- •Mechanical Switches

- •Transistor Switch ON

- •Transistor Switch OFF

- •The FET as a Logic Switch

- •NMOS Logic

- •CMOS Logic

- •Mixed MOS

- •Logic Symbols

- •Tri-State Logic

- •Timing Diagrams

- •Multiplexed Bus

- •Loading and Noise Margin Analysis

- •The Design and Development Process

- •Chapter One Problems

- •2 Microcontroller Concepts

- •Organization: von Neumann vs. Harvard

- •Microprocessor/Microcontroller Basics

- •Microcontroller CPU, Memory, and I/O

- •Design Methodology

- •Introduction to the 8051 Architecture

- •Memory Organization

- •CPU Hardware

- •Oscillator and Timing Circuitry

- •The 8051 Microcontroller Instruction Set Summary

- •Direct and Register Addressing

- •Indirect Addressing

- •Immediate Addressing

- •Generic Address Modes and Instruction Formats

- •Address Modes

- •The Software Development Cycle

- •Software Development Tools

- •Chapter Two Problems

- •Timing Diagram Notation Conventions

- •Rise and Fall Times

- •Propagation Delays

- •Setup and Hold Time

- •Tri-State Bus Interfacing

- •Pulse Width and Clock Frequency

- •Fan-Out and Loading Analysis—DC and AC

- •Calculating Wiring Capacitance

- •Fan-Out When CMOS Drives LSTTL

- •Transmission Line Effects

- •Ground Bounce

- •Logic Family IC Characteristics and Interfacing

- •Interfacing TTL Compatible Signals to 5 Volt CMOS

- •Design Example: Noise Margin Analysis Spreadsheet

- •Worst-Case Timing Analysis Example

- •Chapter Three Review Problems

- •Memory Taxonomy

- •Secondary Memory

- •Sequential Access Memory

- •Direct Access Memory

- •Read/Write Memories

- •Read-Only Memory

- •Other Memory Types

- •JEDEC Memory Pin-Outs

- •Device Programmers

- •Memory Organization Considerations

- •Parametric Considerations

- •Asynchronous vs. Synchronous Memory

- •Error Detection and Correction

- •Error Sources

- •Confidence Checks

- •Memory Management

- •Cache Memory

- •Virtual Memory

- •CPU Control Lines for Memory Interfacing

- •Chapter Four Problems

- •Read and Write Operations

- •Address, Data, and Control Buses

- •Address Spaces and Decoding

- •Address Map

- •Chapter Five Problems

- •The Central Processing Unit (CPU)

- •External Data Memory Cycles

- •External Memory Data Memory Read

- •External Data Memory Write

- •Design Problem 1

- •Design Problem 2

- •Design Problem 3

- •Completing the Analysis

- •Chapter Six Problems

- •Memory Selection and Interfacing

- •Preliminary Timing Analysis

- •Introduction to Programmable Logic

- •Technologies: Fuse-Link, EPROM, EEPROM, and RAM Storage

- •PROM as PLD

- •Programmable Logic Arrays

- •PAL-Style PLDs

- •Design Examples

- •PLD Development Tools

- •Simple I/O Decoding and Interfacing Using PLDs

- •IC Design Using PCs

- •Chapter Seven Problems

- •Direct CPU I/O Interfacing

- •Port I/O for the 8051 Family

- •Output Current Limitations

- •Simple Input/Output Devices

- •Matrix Keyboard Input

- •Program-Controlled I/O Bus Interfacing

- •Real-Time Processing

- •Direct Memory Access (DMA)

- •Burst vs. Single Cycle DMA

- •Cycle Stealing

- •Elementary I/O Devices and Applications

- •Timing and Level Conversion Considerations

- •Level Conversion

- •Power Relays

- •Chapter Eight Problems

- •Interrupt Cycles

- •Software Interrupts

- •Hardware Interrupts

- •Interrupt Driven Program Elements

- •Critical Code Segments

- •Semaphores

- •Interrupt Processing Options

- •Level and Edge Triggered Interrupts

- •Vectored Interrupts

- •Non-Vectored Interrupts

- •Serial Interrupt Prioritization

- •Parallel Interrupt Prioritization

- •Construction Methods

- •10 Other Useful Stuff

- •Electromagnetic Compatibility

- •Electrostatic Discharge Effects

- •Fault Tolerance

- •Software Development Tools

- •Other Specialized Design Considerations

- •Thermal Analysis and Design

- •Battery Powered System Design Considerations

- •Processor Performance Metrics

- •Device Selection Process

- •Power and Ground Planes

- •Ground Problems

- •11 Other Interfaces

- •Analog Signal Conversion

- •Special Proprietary Synchronous Serial Interfaces

- •Unconventional Use of DRAM for Low Cost Data Storage

- •Digital Signal Processing / Digital Audio Recording

- •Detailed Checklist

- •Define Power Supply Requirements

- •Verify Voltage Level Compatibility

- •Check DC Fan-Out: Output Current Drive vs. Loading

- •Verify Worst Case Timing Conditions

- •Determine if Transmission Line Termination is Required

- •Clock Distribution

- •Power and Ground Distribution

- •Asynchronous Inputs

- •Guarantee Power-On Reset State

- •Programmable Logic Devices

- •Deactivate Interrupt and Other Requests on Power-Up

- •Electromagnetic Compatibility Issues

- •Manufacturing and Test Issues

- •Books

- •Web and FTP Sites

- •Periodicals: Subscription

- •Periodicals: Advertiser Supported Trade Magazines

- •Programming Microcontrollers in C, Second Edition

- •Controlling the World with Your PC

- •The Forrest Mims Engineers Notebook

- •The Forrest Mims Circuit Scrapbook, Volumes I and II

- •The Integrated Circuit Hobbyist’s Handbook

- •Simple, Low-Cost Electronics Projects

90EMBEDDED CONTROLLER

Hardware Design

This voltage is maintained while sourcing the LSTTL IIH max of 60 A.

Solving for Rmax :

Rmax <= 1.6 V / 60 A = 26.7 kilohms maximum

Thus, the acceptable range for the pull up resistor is

1.62 kilohms <= RPU <= 26.7 kilohms

An acceptable standard value such as 10 kilohms would be appropriate.

Another limit relates to the rise time of the signal under load, due to the R-C time constant of the pull-up resistor charging the load capacitance, CL. From the example above, let’s see what the effect of this time constant is on the selection of the resistor value.

The maximum R value can be approximated by the equation:

R = T / CL where T is the rise time and CL is the total load capacitance

Ignoring the Ioh current of the LSTTL driver, if the circuit above had an allow able rise time T = 50 nS and CL = 20 pF, then the maximum R value would be:

Rmax = 50 nS / 20 pF = 2.5 kilohms maximum to maintain the 50 nS rise time.

So a better choice might be a standard 2.2 kilohm pull-up resistor. Since the driver will supply some current to charge the load capacitance, this is a fairly conservative value. We would also have to allow for the additional rise time as part of the timing analysis for the low-to-high transition.

Worst-Case Timing Analysis Example

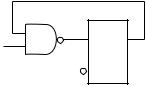

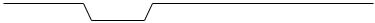

Let’s suppose an LSTTL gate is used to enable the D input of a flip-flop frequency divider, as shown in Figure 3-16. Figure 3-17 shows a

functional timing diagram for the circuit in |

IN |

D Q |

||

|

||||

Figure 3-16, and Figure 3-18 illustrates a specifi |

Clock |

|

> CK |

|

cation timing diagram for the same circuit. The |

|

|||

|

||||

|

|

|

||

timing of the input signals must conform to the |

Figure 3-16: Example of |

|||

combined specs of both devices, as defined below: |

||||

worst-case timing. |

|

|||

91CHAPTER THREE

Worst-Case Timing, Loading, Analysis, and Design

Clock

IN

D

Q

Figure 3-17: Functional timing diagram for Figure 3-16.

Clock

Q

IN

D

|

|

|

|

|

|

overall |

|

|

|

|

|

|

TSU |

TPCKQ TPLH |

|

|

||||

TSU |

||||||

|

or |

for |

||||

TPLH FF

Figure 3-18: Specification timing diagram for Figure 3-16.

Flip-Flop Timing Specs

Symbol |

min |

typ |

max |

units |

|

|

|

|

|

TSU |

10 |

|

|

nS |

TH |

1 |

|

|

nS |

TPCKQ |

|

|

15 |

nS |

TPWCK |

10 |

|

|

nS |

FCLK |

|

|

50 |

MHz |

Gate Timing Specs

Symbol |

min |

typ |

max |

units |

|

|

|

|

|

TPHL |

1 |

2 |

5 |

nS |

TPLH |

2 |

4 |

6 |

nS |

Test conditions RL = 1K, CL = 100 pF

For the circuit shown in Figure 3-16 and the accompanying specifications, what is the maximum guaranteed clock rate?