- •Objectives

- •Embedded Microcomputer Applications

- •Microcomputer and Microcontroller Architectures

- •Digital Hardware Concepts

- •Voltage, Current, and Resistance

- •Diodes

- •Transistors

- •Mechanical Switches

- •Transistor Switch ON

- •Transistor Switch OFF

- •The FET as a Logic Switch

- •NMOS Logic

- •CMOS Logic

- •Mixed MOS

- •Logic Symbols

- •Tri-State Logic

- •Timing Diagrams

- •Multiplexed Bus

- •Loading and Noise Margin Analysis

- •The Design and Development Process

- •Chapter One Problems

- •2 Microcontroller Concepts

- •Organization: von Neumann vs. Harvard

- •Microprocessor/Microcontroller Basics

- •Microcontroller CPU, Memory, and I/O

- •Design Methodology

- •Introduction to the 8051 Architecture

- •Memory Organization

- •CPU Hardware

- •Oscillator and Timing Circuitry

- •The 8051 Microcontroller Instruction Set Summary

- •Direct and Register Addressing

- •Indirect Addressing

- •Immediate Addressing

- •Generic Address Modes and Instruction Formats

- •Address Modes

- •The Software Development Cycle

- •Software Development Tools

- •Chapter Two Problems

- •Timing Diagram Notation Conventions

- •Rise and Fall Times

- •Propagation Delays

- •Setup and Hold Time

- •Tri-State Bus Interfacing

- •Pulse Width and Clock Frequency

- •Fan-Out and Loading Analysis—DC and AC

- •Calculating Wiring Capacitance

- •Fan-Out When CMOS Drives LSTTL

- •Transmission Line Effects

- •Ground Bounce

- •Logic Family IC Characteristics and Interfacing

- •Interfacing TTL Compatible Signals to 5 Volt CMOS

- •Design Example: Noise Margin Analysis Spreadsheet

- •Worst-Case Timing Analysis Example

- •Chapter Three Review Problems

- •Memory Taxonomy

- •Secondary Memory

- •Sequential Access Memory

- •Direct Access Memory

- •Read/Write Memories

- •Read-Only Memory

- •Other Memory Types

- •JEDEC Memory Pin-Outs

- •Device Programmers

- •Memory Organization Considerations

- •Parametric Considerations

- •Asynchronous vs. Synchronous Memory

- •Error Detection and Correction

- •Error Sources

- •Confidence Checks

- •Memory Management

- •Cache Memory

- •Virtual Memory

- •CPU Control Lines for Memory Interfacing

- •Chapter Four Problems

- •Read and Write Operations

- •Address, Data, and Control Buses

- •Address Spaces and Decoding

- •Address Map

- •Chapter Five Problems

- •The Central Processing Unit (CPU)

- •External Data Memory Cycles

- •External Memory Data Memory Read

- •External Data Memory Write

- •Design Problem 1

- •Design Problem 2

- •Design Problem 3

- •Completing the Analysis

- •Chapter Six Problems

- •Memory Selection and Interfacing

- •Preliminary Timing Analysis

- •Introduction to Programmable Logic

- •Technologies: Fuse-Link, EPROM, EEPROM, and RAM Storage

- •PROM as PLD

- •Programmable Logic Arrays

- •PAL-Style PLDs

- •Design Examples

- •PLD Development Tools

- •Simple I/O Decoding and Interfacing Using PLDs

- •IC Design Using PCs

- •Chapter Seven Problems

- •Direct CPU I/O Interfacing

- •Port I/O for the 8051 Family

- •Output Current Limitations

- •Simple Input/Output Devices

- •Matrix Keyboard Input

- •Program-Controlled I/O Bus Interfacing

- •Real-Time Processing

- •Direct Memory Access (DMA)

- •Burst vs. Single Cycle DMA

- •Cycle Stealing

- •Elementary I/O Devices and Applications

- •Timing and Level Conversion Considerations

- •Level Conversion

- •Power Relays

- •Chapter Eight Problems

- •Interrupt Cycles

- •Software Interrupts

- •Hardware Interrupts

- •Interrupt Driven Program Elements

- •Critical Code Segments

- •Semaphores

- •Interrupt Processing Options

- •Level and Edge Triggered Interrupts

- •Vectored Interrupts

- •Non-Vectored Interrupts

- •Serial Interrupt Prioritization

- •Parallel Interrupt Prioritization

- •Construction Methods

- •10 Other Useful Stuff

- •Electromagnetic Compatibility

- •Electrostatic Discharge Effects

- •Fault Tolerance

- •Software Development Tools

- •Other Specialized Design Considerations

- •Thermal Analysis and Design

- •Battery Powered System Design Considerations

- •Processor Performance Metrics

- •Device Selection Process

- •Power and Ground Planes

- •Ground Problems

- •11 Other Interfaces

- •Analog Signal Conversion

- •Special Proprietary Synchronous Serial Interfaces

- •Unconventional Use of DRAM for Low Cost Data Storage

- •Digital Signal Processing / Digital Audio Recording

- •Detailed Checklist

- •Define Power Supply Requirements

- •Verify Voltage Level Compatibility

- •Check DC Fan-Out: Output Current Drive vs. Loading

- •Verify Worst Case Timing Conditions

- •Determine if Transmission Line Termination is Required

- •Clock Distribution

- •Power and Ground Distribution

- •Asynchronous Inputs

- •Guarantee Power-On Reset State

- •Programmable Logic Devices

- •Deactivate Interrupt and Other Requests on Power-Up

- •Electromagnetic Compatibility Issues

- •Manufacturing and Test Issues

- •Books

- •Web and FTP Sites

- •Periodicals: Subscription

- •Periodicals: Advertiser Supported Trade Magazines

- •Programming Microcontrollers in C, Second Edition

- •Controlling the World with Your PC

- •The Forrest Mims Engineers Notebook

- •The Forrest Mims Circuit Scrapbook, Volumes I and II

- •The Integrated Circuit Hobbyist’s Handbook

- •Simple, Low-Cost Electronics Projects

100EMBEDDED CONTROLLER

Hardware Design

Another way of classifying memory devices is based on how information is written into the memory. Read/write memories are memories that can be written to as easily as they are read from by the processor.

Read/Write Memories

Static RAM or SRAM refers to a volatile semiconductor read/write memory in which the basic storage element is a flip-flop to store each bit. The flip-flops are arranged in rows and columns and are available in several organizations. The flip-flops take about four transistors per bit of storage, so they are generally about four times less dense than DRAMs that use only one transistor per bit. While these devices are volatile, they will maintain information as long as they are powered, unlike dynamic RAM that must be refreshed.

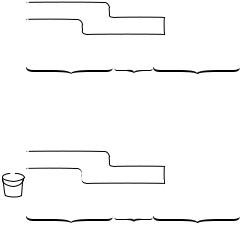

Dynamic RAM or DRAM, is a memory using a capacitor as the storage element. The presence or absence of charge on the capacitor represents ones and zeros. Because the capacitors are not perfect, they leak charge and will “forget” in as little as a few milliseconds if they are left alone, rather like a small child after being told to clean her room. In order to make the capacitors useful for storage they must be periodically refreshed. This is done by sensing whether there is any charge present on the capacitor and recharging the capacitor if there was charge present when it was sensed.

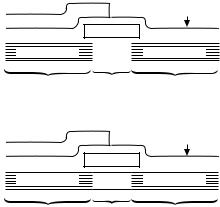

Refer to Figure 4-5. Charge is stored on the parasitic gate capacitance of a MOSFET transistor so that only one transistor is required per bit of storage. The process of reading or sensing the data is destructive in the sense that the charge representing the data is lost when it is sensed. The DRAM capacitor must be refreshed whenever it is read, and also periodically to restore the charge that leaks away. Each row in a DRAM has a sense amplifier and recharge circuitry designed to read and restore the data on an entire row at once. In order to refresh the DRAM data, a special abbreviated read cycle must be performed for each row of the memory. Because of the high density of data storage in DRAMs such as a 4 megabit device, the memory must have 22 address bits to select the location to be read or written. Rather than using 22 individual pins to specify the location, 11 wires are used and the address is latched by the DRAM in two parts: the row address and the column address. This is referred to as a multiplexed address Two control signals, row address strobe (RAS) and

101CHAPTER FOUR

Memory Technologies and Interfacing

column address strobe (CAS, are used to multiplex the two 11-bit halves of the address into the DRAM. To simplify the refresh process, only the row address is used in a refresh cycle. Doing this takes advan tage of the fact that there is one sense and refresh circuit for each bit in a row. The refresh row address is sequenced through all possible addresses before the capacitors can discharge.

One DRAM Bit Cell

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Gate |

|

|

SiO2 |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Semiconductor. |

|

|

|

|

|

|

|

Semiconductor. |

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Source |

|

Channel |

Drain |

||||||||||

|

|

|

|

|

|

|

|

ON or OFF |

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

depending on |

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

gate voltage |

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

Charge on gate leaks off slowly, |

|||||||||

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

and must be “refreshed” periodically |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Gate |

SiO2 |

|||||||

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

Bit |

|

|

|

Semiconductor. |

|

|

|

|

|

|

|

Semiconductor. |

|

|

||||

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

Bucket |

|

|

|

Source |

|

Channel |

Drain |

|||||||||||

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

ON |

|

|

|

|

|

||||

Read-Only Memory

Figure 4-5: Dynamic RAM bit storage mechanism.

Read-only memory (ROM) is a class of storage that cannot be erased or modi fied by the processor. Typical embedded systems may make use of one or more of the following types of ROM: mask ROM PROM, EPROM EEPROM or flash EPROM.

Mask ROM is memory that has been programmed at the time it is manufactured and can never be changed. The data patterns are defined by the photographic masks used to define the circuits on a chip when it is being fabricated. Mask ROMs are used when the programs or data do not need to be changed, when the production quantities are large, and the cost must be as low as possible. This is the oldest form of ROM and is still used in high volume applications because of its very low manufacturing cost. The program must be permanently defined in advance by including it as part of the master artwork film or “masks” used to fabricate the chips. It is also the least flexible to change, as a program change necessitates building and packaging new chips, which can take from weeks to months to accomplish.

PROM is user-programmable ROM, which is often used as a generic term for memories that can be programmed one or more times by the user using a special device called a PROM programmer or PROM burner. This was the first “field programmable” memory, meaning that it can be loaded with data by the

103CHAPTER FOUR

Memory Technologies and Interfacing

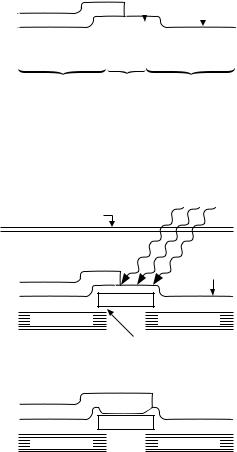

current flow across the insulating region for up to 50 milliseconds, and some of the charge is stranded on the floating gate. Figure 4-7 illustrates the program and read operations of a typical EPROM.

|

Reading a Bit |

|

Charged |

Insulating |

|||||||||||

|

|

Gate |

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

Material |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Metal |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Metal Gate |

|

|

SiO2 |

||||

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Semiconductor. |

|

|

|

|

|

|

|

|

Semiconductor. |

|

||

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Source Channel Drain