- •Table of Contents

- •Objectives

- •Embedded Microcomputer Applications

- •Microcomputer and Microcontroller Architectures

- •Digital Hardware Concepts

- •Voltage, Current, and Resistance

- •Diodes

- •Transistors

- •Mechanical Switches

- •Transistor Switch ON

- •Transistor Switch OFF

- •The FET as a Logic Switch

- •NMOS Logic

- •CMOS Logic

- •Mixed MOS

- •Real Transistors Don’t Eat Q!

- •Logic Symbols

- •Tri-State Logic

- •Timing Diagrams

- •Multiplexed Bus

- •Loading and Noise Margin Analysis

- •The Design and Development Process

- •Chapter One Problems

- •Organization: von Neumann vs. Harvard

- •Microprocessor/Microcontroller Basics

- •Microcontroller CPU, Memory, and I/O

- •Design Methodology

- •The 8051 Family Microcontroller

- •Processor Architecture

- •Introduction to the 8051 Architecture

- •8051 Memory Organization

- •8051 CPU Hardware

- •Oscillator and Timing Circuitry

- •The 8051 Microcontroller Instruction Set Summary

- •Direct and Register Addressing

- •Indirect Addressing

- •Immediate Addressing

- •Generic Address Modes and Instruction Formats

- •8051 Address Modes

- •The Software Development Cycle

- •Software Development Tools

- •Hardware Development Tools

- •Chapter Two Problems

- •Timing Diagram Notation Conventions

- •Rise and Fall Times

- •Propagation Delays

- •Setup and Hold Time

- •Tri-State Bus Interfacing

- •Pulse Width and Clock Frequency

- •Fan-Out and Loading Analysis—DC and AC

- •Calculating Wiring Capacitance

- •Fan-Out When CMOS Drives LSTTL

- •Transmission Line Effects

- •Ground Bounce

- •Logic Family IC Characteristics and Interfacing

- •Interfacing TTL Compatible Signals to 5 Volt CMOS

- •Design Example: Noise Margin Analysis Spreadsheet

- •Worst-Case Timing Analysis Example

- •Chapter Three Review Problems

- •Memory Taxonomy

- •Secondary Memory

- •Sequential Access Memory

- •Direct Access Memory

- •Read/Write Memories

- •Read-Only Memory

- •Other Memory Types

- •JEDEC Memory Pin-Outs

- •Device Programmers

- •Memory Organization Considerations

- •Parametric Considerations

- •Asynchronous vs. Synchronous Memory

- •Error Detection and Correction

- •Error Sources

- •Confidence Checks

- •Memory Management

- •Cache Memory

- •Virtual Memory

- •CPU Control Lines for Memory Interfacing

- •Chapter Four Problems

- •Read and Write Operations

- •Address, Data, and Control Buses

- •Address Spaces and Decoding

- •Address Map

- •Chapter Five Problems

- •The Central Processing Unit (CPU)

- •Memory Selection and Interfacing

- •Preliminary Timing Analysis

- •External Data Memory Cycles

- •External Memory Data Memory Read

- •External Data Memory Write

- •Design Problem 1

- •Design Problem 2

- •Design Problem 3

- •Completing the Analysis

- •Chapter Six Problems

- •Introduction to Programmable Logic

- •Technologies: Fuse-Link, EPROM, EEPROM, and RAM Storage

- •PROM as PLD

- •Programmable Logic Arrays

- •PAL-Style PLDs

- •Design Examples

- •PLD Development Tools

- •Simple I/O Decoding and Interfacing Using PLDs

- •IC Design Using PCs

- •Chapter Seven Problems

- •Direct CPU I/O Interfacing

- •Port I/O for the 8051 Family

- •Output Current Limitations

- •Simple Input/Output Devices

- •Matrix Keyboard Input

- •Program-Controlled I/O Bus Interfacing

- •Real-Time Processing

- •Direct Memory Access (DMA)

- •Burst vs. Single Cycle DMA

- •Cycle Stealing

- •Elementary I/O Devices and Applications

- •Timing and Level Conversion Considerations

- •Level Conversion

- •Power Relays

- •Chapter Eight Problems

- •Interrupt Cycles

- •Software Interrupts

- •Hardware Interrupts

- •Interrupt Driven Program Elements

- •Critical Code Segments

- •Semaphores

- •Interrupt Processing Options

- •Level and Edge Triggered Interrupts

- •Vectored Interrupts

- •Non-Vectored Interrupts

- •Serial Interrupt Prioritization

- •Parallel Interrupt Prioritization

- •Construction Methods

- •Power and Ground Planes

- •Ground Problems

- •Electromagnetic Compatibility

- •Electrostatic Discharge Effects

- •Fault Tolerance

- •Hardware Development Tools

- •Instrumentation Issues

- •Software Development Tools

- •Other Specialized Design Considerations

- •Thermal Analysis and Design

- •Battery Powered System Design Considerations

- •Processor Performance Metrics

- •Benchmarks

- •Device Selection Process

- •Analog Signal Conversion

- •Special Proprietary Synchronous Serial Interfaces

- •Unconventional Use of DRAM for Low Cost Data Storage

- •Digital Signal Processing / Digital Audio Recording

- •Detailed Checklist

- •1. Define Power Supply Requirements

- •2. Verify Voltage Level Compatibility

- •3. Check DC Fan-Out: Output Current Drive vs. Loading

- •4. AC (Capacitive) Output Drive vs. Capacitive Load and De-rating

- •5. Verify Worst Case Timing Conditions

- •6. Determine if Transmission Line Termination is Required

- •7. Clock Distribution

- •8. Power and Ground Distribution

- •9. Asynchronous Inputs

- •10. Guarantee Power-On Reset State

- •11. Programmable Logic Devices

- •12. Deactivate Interrupt and Other Requests on Power-Up

- •13. Electromagnetic Compatibility Issues

- •14. Manufacturing and Test Issues

- •Books

- •Web and FTP Sites

- •Periodicals: Subscription

- •Periodicals: Advertiser Supported Trade Magazines

- •Index

175CHAPTER EIGHT

Basic I/O Interfaces

register must be polled to determine if the device is ready. If the program is written to loop continuously waiting for the device to become ready, a lot of CPU time is wasted if the data is not available shortly after the polling begins. An example would be a keyboard, where keys are pressed at relatively slow and unpredictable rates. In order to minimize the time wasted in polling for these irregular data, interrupts are used. An interrupt is triggered by an event that is not synchronized to the main program and calls a special subroutine, referred to as an interrupt service routine (ISR that transfers the data. This “on-demand” processing is more efficient when data rates are relatively slow or unpredictable. At the other extreme however, when peak data transfer rates are high as they are in a disk drive, another technique that reduces the amount of work the CPU must do to transfer I/O data is used. The I/O interface transfers data directly between the I/O device and memory without CPU intervention using direct memory access (DMA).

Real-Time Processing

Some applications demand that the CPU respond to external events and process them in a finite amount of time. Real-time processing means that data are processed at the same rate that they occur. They are event-driven which means they are triggered by external events, such as the tick of a clock, completion of I/O, etc. Examples of real-time PC programs are the flight control program on the Space Shuttle, arcade games, speech processing software, and flight simulators. Examples of non-real-time PC programs would be word processors and accounting programs.

Direct Memory Access (DMA)

Direct memory access (DMA) requires that the I/O interface be active and semiintelligent, since it must count the words and increment the memory address for each element transferred in addition to performing the actual transfer.

The transfer process involved with DMA is typically as follows:

1)The program writes into the I/O control register of the interface:

a)The type of transfer (I or O).

b)The number of bytes or “block size” to transfer.

176EMBEDDED CONTROLLER

Hardware Design

c)The physical address in memory where the data will be transferred.

d)A start command is given to begin the transfer.

2)Data is transferred directly between memory and I/O devices under control of the I/O interface.

3)When the transfer is complete, the I/O interface sets a completion bit in the status register, and may also initiate an interrupt to the CPU.

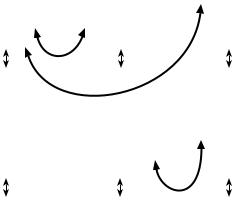

Figure 8-10 compares program-controlled and DMA I/O.

Direct memory access is used for high speed I/O. The I/O device interface takes over the bus from the CPU and controls the transfer of data between memory and I/O directly, without any intervention by the CPU (as shown in Figure 8-10). Data is generally transferred in larger blocks, such as a disk file block.

Program Controlled I/O

CPU |

|

Memory |

|

I/O |

|

|

|

|

|

DMA (Direct Memory Access) I/O

CPU |

|

Memory |

|

I/O |

|

|

|

|

|

Devices on a bus can talk with each other without

talking with the CPU, except to tell it when done. DMA is good for disk and network transfers because the rates are much higher than the CPU can handle using program controlled I/O. There are two ways of doing DMA transfers: single cycle DMA and burst DMA modes.

Burst vs. Single Cycle DMA

In burst mode DMA, the DMA device gets control of the bus, transfers a whole block of data (a disk sector, for example), and then releases the memory back to the CPU. A single cycle DMA device gets the bus, transfers just one word of data, and releases the bus. Arbitration is the process of determining what device will have control of the memory bus.

177CHAPTER EIGHT

Basic I/O Interfaces

Burst mode has low overhead and can handle the highest peak data rates, but the CPU can get locked out of memory for intervals that are as long as the longest block to be transferred. If the transfer is longer than the shortest interrupt interval, such as the real time clock tick interval, interrupts can get lost.

Cycle Stealing

In this mode, DMA transfers are completed during bus cycles that are not used by the CPU, so no arbitration needs to be done. Most modern, high performance processors utilize almost 100% of available memory bandwidth however, so there isn’t much available for DMA. To save time, it is possible to perform arbitration and data transfer overlapping in time.

In general, burst mode DMA is more effective when relatively short time durations are needed to transfer the data block. Under those conditions, the bus is fully utilized for a short time interval. The DMA controller acquires access to the memory, transfers an entire block of data, and then releases the memory. An entire block of data is transferred in one short burst. The disadvantage is that a burst mode DMA device “hogs” the bus, thus preventing any other device from accessing memory during the burst. If the burst lasts too long, it may prevent the CPU from servicing certain time critical events, such as the real time clock interval (clock tick). In that case, the clock would run slower than it should because it would cause the CPU to miss some of the clock ticks. Therefore, burst mode DMA is most effective for data that is transferred at a high peak rate for short intervals. Typically, the data within a burst comes in too quickly to allow the arbitration handshaking required for the DMA controller to acquire and release the data between each data element. An example of this situation is the transmission or reception of data on a high-speed local area network interface. Small packets of data come across the network in high-speed (less than one microsecond per byte) bursts, with relatively low packet rates (milliseconds between packets).

For single cycle mode, the DMA controller acquires access to memory, transfers one word, and releases the memory. That allows other memory transfers to be interleaved with the DMA. That is why this mode is also referred to as “interleaved DMA.” Single cycle DMA is better suited to transferring data over longer periods of time, where there is enough time to acquire and release the bus for every word transferred. In this case, the CPU and other devices can still access