- •Table of Contents

- •Objectives

- •Embedded Microcomputer Applications

- •Microcomputer and Microcontroller Architectures

- •Digital Hardware Concepts

- •Voltage, Current, and Resistance

- •Diodes

- •Transistors

- •Mechanical Switches

- •Transistor Switch ON

- •Transistor Switch OFF

- •The FET as a Logic Switch

- •NMOS Logic

- •CMOS Logic

- •Mixed MOS

- •Real Transistors Don’t Eat Q!

- •Logic Symbols

- •Tri-State Logic

- •Timing Diagrams

- •Multiplexed Bus

- •Loading and Noise Margin Analysis

- •The Design and Development Process

- •Chapter One Problems

- •Organization: von Neumann vs. Harvard

- •Microprocessor/Microcontroller Basics

- •Microcontroller CPU, Memory, and I/O

- •Design Methodology

- •The 8051 Family Microcontroller

- •Processor Architecture

- •Introduction to the 8051 Architecture

- •8051 Memory Organization

- •8051 CPU Hardware

- •Oscillator and Timing Circuitry

- •The 8051 Microcontroller Instruction Set Summary

- •Direct and Register Addressing

- •Indirect Addressing

- •Immediate Addressing

- •Generic Address Modes and Instruction Formats

- •8051 Address Modes

- •The Software Development Cycle

- •Software Development Tools

- •Hardware Development Tools

- •Chapter Two Problems

- •Timing Diagram Notation Conventions

- •Rise and Fall Times

- •Propagation Delays

- •Setup and Hold Time

- •Tri-State Bus Interfacing

- •Pulse Width and Clock Frequency

- •Fan-Out and Loading Analysis—DC and AC

- •Calculating Wiring Capacitance

- •Fan-Out When CMOS Drives LSTTL

- •Transmission Line Effects

- •Ground Bounce

- •Logic Family IC Characteristics and Interfacing

- •Interfacing TTL Compatible Signals to 5 Volt CMOS

- •Design Example: Noise Margin Analysis Spreadsheet

- •Worst-Case Timing Analysis Example

- •Chapter Three Review Problems

- •Memory Taxonomy

- •Secondary Memory

- •Sequential Access Memory

- •Direct Access Memory

- •Read/Write Memories

- •Read-Only Memory

- •Other Memory Types

- •JEDEC Memory Pin-Outs

- •Device Programmers

- •Memory Organization Considerations

- •Parametric Considerations

- •Asynchronous vs. Synchronous Memory

- •Error Detection and Correction

- •Error Sources

- •Confidence Checks

- •Memory Management

- •Cache Memory

- •Virtual Memory

- •CPU Control Lines for Memory Interfacing

- •Chapter Four Problems

- •Read and Write Operations

- •Address, Data, and Control Buses

- •Address Spaces and Decoding

- •Address Map

- •Chapter Five Problems

- •The Central Processing Unit (CPU)

- •Memory Selection and Interfacing

- •Preliminary Timing Analysis

- •External Data Memory Cycles

- •External Memory Data Memory Read

- •External Data Memory Write

- •Design Problem 1

- •Design Problem 2

- •Design Problem 3

- •Completing the Analysis

- •Chapter Six Problems

- •Introduction to Programmable Logic

- •Technologies: Fuse-Link, EPROM, EEPROM, and RAM Storage

- •PROM as PLD

- •Programmable Logic Arrays

- •PAL-Style PLDs

- •Design Examples

- •PLD Development Tools

- •Simple I/O Decoding and Interfacing Using PLDs

- •IC Design Using PCs

- •Chapter Seven Problems

- •Direct CPU I/O Interfacing

- •Port I/O for the 8051 Family

- •Output Current Limitations

- •Simple Input/Output Devices

- •Matrix Keyboard Input

- •Program-Controlled I/O Bus Interfacing

- •Real-Time Processing

- •Direct Memory Access (DMA)

- •Burst vs. Single Cycle DMA

- •Cycle Stealing

- •Elementary I/O Devices and Applications

- •Timing and Level Conversion Considerations

- •Level Conversion

- •Power Relays

- •Chapter Eight Problems

- •Interrupt Cycles

- •Software Interrupts

- •Hardware Interrupts

- •Interrupt Driven Program Elements

- •Critical Code Segments

- •Semaphores

- •Interrupt Processing Options

- •Level and Edge Triggered Interrupts

- •Vectored Interrupts

- •Non-Vectored Interrupts

- •Serial Interrupt Prioritization

- •Parallel Interrupt Prioritization

- •Construction Methods

- •Power and Ground Planes

- •Ground Problems

- •Electromagnetic Compatibility

- •Electrostatic Discharge Effects

- •Fault Tolerance

- •Hardware Development Tools

- •Instrumentation Issues

- •Software Development Tools

- •Other Specialized Design Considerations

- •Thermal Analysis and Design

- •Battery Powered System Design Considerations

- •Processor Performance Metrics

- •Benchmarks

- •Device Selection Process

- •Analog Signal Conversion

- •Special Proprietary Synchronous Serial Interfaces

- •Unconventional Use of DRAM for Low Cost Data Storage

- •Digital Signal Processing / Digital Audio Recording

- •Detailed Checklist

- •1. Define Power Supply Requirements

- •2. Verify Voltage Level Compatibility

- •3. Check DC Fan-Out: Output Current Drive vs. Loading

- •4. AC (Capacitive) Output Drive vs. Capacitive Load and De-rating

- •5. Verify Worst Case Timing Conditions

- •6. Determine if Transmission Line Termination is Required

- •7. Clock Distribution

- •8. Power and Ground Distribution

- •9. Asynchronous Inputs

- •10. Guarantee Power-On Reset State

- •11. Programmable Logic Devices

- •12. Deactivate Interrupt and Other Requests on Power-Up

- •13. Electromagnetic Compatibility Issues

- •14. Manufacturing and Test Issues

- •Books

- •Web and FTP Sites

- •Periodicals: Subscription

- •Periodicals: Advertiser Supported Trade Magazines

- •Index

96EMBEDDED CONTROLLER

Hardware Design

The same technologies that were developed for memories have been applied to programmable logic and microcontroller chips. Each memory technology has unique advantages and limitations that the designer must be aware of.

The wide variety of storage concepts and technology are central to the design of microcontrollers, and are categorized and described in this chapter.

Memory Taxonomy

There are many classes of memory devices, and the emphasis is placed here on those that are of significance to the designer of embedded systems. As a result, most of this chapter is dedicated to solid-state semiconductor memory chips rather than magnetic and optical storage devices.

The most significant distinction between memory devices is how they are connected to the CPU. There are two ways of connecting memory to the CPU:

•Primary memory the CPU is directly connected to the memory

•Secondary memory: connected to the CPU indirectly

Figure 4-2 illustrates the differ- |

|

|

|

|

|

|

Secondary |

|

|

|

|

|

|

|

|

Memory |

|

||

ence in the way the two types |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

are connected to the processor |

|

|

|

|

|

|

|

|

|

bus. The CPU is only able to |

|

CPU |

|

Primary |

|

|

Secondary |

|

|

|

|

Memory |

|

|

|

||||

directly access information |

|

|

|

|

|

Memory |

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

Control |

|

|

|

stored in primary memory. All |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

instructions and data must be |

|

|

|

|

|

|

|

|

|

transferred to primary memory |

|

|

|

|

|

|

|

|

|

first before the CPU can process |

|

|

CPU has direct |

|

CPU accesses |

||||

them. An example of primary |

|

|

|

||||||

|

|

access to data |

secondary memory |

||||||

memory is semiconductor RAM. |

|

|

|

in primary |

indirectly through |

||||

|

|

|

memory |

memory control device |

|||||

The term RAM is frequently, |

|

Figure 4-2: Primary versus secondary memory. |

|||||||

but improperly, used to refer to |

|

||||||||

|

|

|

|

|

|

|

|

|

|

primary storage. RAM only specifies the access mechanism (described below) but is often misused to imply the primary read/write semiconductor storage from which the CPU fetches instructions and data. Random access methods may be used in either primary or secondary memories, but are most commonly used for the primary storage, which is why RAM has been associated

97CHAPTER FOUR

Memory Technologies and Interfacing

with primary memories. Because the CPU must access instructions and data quickly, primary memory must have very fast access time, on the order of tens to hundreds of nanoseconds or approximately 10-8 to 10-7 seconds, compared to secondary (disk) memory with memory access on the order of milliseconds (10-3 seconds).

Unfortunately, semiconductor memory, which is used for primary storage because of its high speed, is much higher in cost, size, and power per bit of storage than secondary memories. Semiconductor memory is currently the most practical mechanism for storing programs and data that are available for immediate use by the CPU. This is because the primary program and data memory must operate on the order of the speed of the processor memory cycles. Otherwise, the memory speed limits the overall system speed, because the CPU would have to be forced to wait until the memory is ready. One or more CPU clock cycles would have to be added to each memory access in order to slow the CPU down to match the speed of the memory. These delay cycles are referred to as wait states because the processor must wait for one or more clocks before the memory data is available to the CPU.

Secondary Memory

A separate intermediate device usually controls secondary memory, which is not directly accessible to the CPU. The device manages the transfer of information between the storage device and the processor bus. When the data stored on a secondary memory device is needed by the CPU, it must first be moved to primary memory via the controller before the CPU can access it. Examples of secondary storage include magnetic and optical disk and tape that are used for large information stores because of their low cost per bit combined with high density and low power. Because of these differences, typical microcomputer architectures have about an order of magnitude larger secondary memories than primary memories. Secondary memories such as disk drives are most appropriate for storing large programs and data sets that must be maintained over a period of time. Secondary memories like magnetic tapes are often used for archival or backup storage because of their very high density and low cost. Another major advantage to magnetic and optical storage is that it is non-volatile.

99CHAPTER FOUR

Memory Technologies and Interfacing

Sequential Access Memory

Sequential access memory has an access time that is dependent upon the location of the data that is to be accessed. This is best illustrated by using the most common sequential access device: a magnetic tape. The information is stored in a serial fashion onto the tape, and the only data that can be accessed at any instant is the data stored on the tape in contact with the read/write head. Thus when the head is positioned at the beginning of the tape, the entire length of the tape must pass by the head before the last item can be accessed.

Direct Access Memory

Direct access memory which is a sort of combination of random and sequential access methods, is used on disk drives to provide an intermediate access time to fill the gap between high-speed random and low speed sequential access devices.

The storage medium is disk shaped, and contains a magnetic film for standard “hard drive” or fixed magnetic disks. Optical disks use an ultra-thin optical metal film that can be written once with a high intensity laser or read back using a low power laser. Optical disks that can be erased and re-written use a magneto-optical film whose optical properties (light polarization angle) can be changed using a low power laser and a magnetic field.

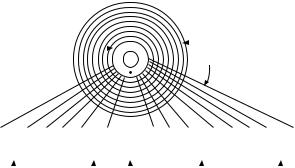

In each case, information is stored on concentric rings, called tracks on the disk. The information is stored sequentially on each track as it is on tape, but the read/write head

can be moved to select |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

the appropriate track. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Disks with multiple |

|

|

|

Highest |

|

|

|

|

|

|

|

Track Zero |

|

|

|

||||||

recording surfaces also |

Numbered Track |

|

|

|

|

|

|

|

|

(Outermost Track) |

|||||||||||

|

|

|

|

|

|

|

|

||||||||||||||

(Innermost Track) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

have multiple heads |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Rotation |

|

|

|

|

to read each surface, |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

so they are randomly |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

accessible by head and |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

track, and sectors are |

|

Data |

Gap |

ID |

Gap |

Data |

Pre- |

Pre- |

ID1 |

Gap |

Data1 |

Gap |

ID2 |

Gap |

Dat2a |

||||||

|

Index |

Index |

|||||||||||||||||||

sequentially accessed on |

|

|

|

|

|

|

|

|

|

Gap |

Gap |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

each track. Figure 4-4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

Index Mark |

|

|

|

|

|

|

|

|

||||

|

Sector |

Sector |

Sector |

|

Sector |

||||||||||||||||

illustrates this. |

|

|

|

|

|

|

|||||||||||||||

|

n-1 |

n |

|

|

|

|

1 |

|

|

2 |

|||||||||||