11. Лекция№11 Обзор современных сапр модулей эвт 35

Современные тенденции развития САПР электронных систем 36

Типовой маршрут проектирования 36

Новые тенденции в проектировании печатных плат 37

12. Лекция№12 Методы обеспечения надежности электронных систем 38

Выбор конструктивного использования компонентов и создание топологии 38

Производственные дефекты компонентов 38

Экранирование системы 38

Оценка предотвращения тепловых повреждений 39

Особенности теплового анализа проекта 39

Способы оценки надежности и качества функционирования

электронного оборудования 40

13. Лекция№13 Надежность изделия 42

Отбраковочные технологические испытания как средства повышения надежности партии интегральных микросхем 43

14. Лекция№14 Состав отбраковочных испытаний ИС в отечественной промышленности 46

Требования к отбраковочным испытания ИС за рубежом 47

15. Лекция№15 О подходе к выбору инструментальных средств для автоматизированного проектирования печатных плат 49

Решение проблемы проектирования печатных плат EDA инструментами 49

Процедура размещения и трассировки с учетом эффектов искажений сигналов 49

16. Лекция№16 Некоторые практические рекомендации для проектирования ПП в наносекундном диапазоне 52

Анализ наводов ЭМИ от высокочастотных электронных устройств 52

Анализ распределения температур по ПП 53

Особенности EDA инструм-ов для проект-я плат по технологии ТПМК 53

Современные EDA инструменты для проектирования ПП 54

17. Лекция№17 (продолжение лекции №16) 55

Выход на производство 55

От P-CAD к Accel EDA 56

Пути развития 56

Проектирование вычислительных устройств с помощью VHDL 56

Ход проектирования устройства с использование VHDL 57

18. Лекция№18 Технология разработки систем на кристалле 59

Вычислительные заготовки 59

19. Лекция№19 Программистская модель вычислителя VHDL 61

20. Лекция№20 Разработка микросхем на языке VHDL 64

Уровни кодирования на VHDL 65

20. Лекция№20 Разработка микросхем на языке VHDL 64

Уровни кодирования на VHDL 65

21. Лекция№21 Классификация и основные этапы изготовления

микросхем 67

Принципы формирования структур микросхемы 68

EUV литография 69

Лекция № 11 Обзор современных САПР модулей ЭВТ

|

№ |

Задачи |

Программа на ПК |

Фирма разработчик |

Фирма дистрибьютор |

|

1 |

Проектирование аналоговых и аналогово-цифровых устройств |

Design Lab |

Micro SIM |

Родник Софт |

|

2 |

Разработка печатных плат |

Accel EDA |

Accel Technologies |

Родник Софт |

|

P-CAD |

Accel Technologies и Protel |

Скан | ||

|

OR-CAD |

OR-CAD |

Скан | ||

|

Personal Architect |

Mentor Graphics |

Поинт | ||

|

Caddy Electronics |

Ziegler |

Поинт | ||

|

3 |

Трассировка печатных плат |

Spectra |

CCT |

Родник Софт |

|

MAX ROUT |

Or-cad |

Скан | ||

|

Neiro Rout |

Protel Technologies |

Родник Софт | ||

|

FR ROUT |

Д. Феофанов |

Точка опоры | ||

|

4 |

Моделирование цифровых устройств |

Active Cad |

Aldec |

Родник Софт |

|

Work View |

VLS |

Родник Софт | ||

|

Or-cad simulate |

Or-cad |

Скан | ||

|

5 |

Синтез цифровых микросхем с программируемой логикой |

Act-step 6 |

Xilings |

Родник Софт, Скан |

|

MAX4 |

Altera |

Родник Софт, Скан | ||

|

Design service |

Accel Technologies |

Гамма | ||

|

6 |

Анализ тепловых режимов, надежности и прогностическая оценка характеристик печатных плат |

Beta Soft |

DynamicSoft |

Родник Софт |

|

Prec |

International Analytic |

Родник Софт | ||

|

7 |

Моделирование печатных плат с учетом паразитных помех / эффектов |

Polaris |

MicroSim |

Родник Софт |

|

Board Sim |

HypperLyax |

Родник Софт | ||

|

8 |

Синтез и моделирование устройств СВЧ |

Micro Wave Success |

Compact Software |

Скан |

|

HP Soft |

Hewlett Packard |

Скан, Радис | ||

|

9 |

Подготовка печатных плат к производству |

CAM 350 |

Advanced Technologies |

Родник Софт |

|

PC-Gerber |

Router Solution |

Родник Софт | ||

|

CAM-CAD |

|

Родник Софт |

Система Cadenceв состоянии решать все эти задачи. К этому уровню подходит и системаMentorGraphics.

Современные тенденции развития САПР электронных систем (на примере систем фирмы Mentor Graphics)

В настоящее время развитие средств автоматизации проектирования электронных систем определяются тремя основными факторами:

быстрый рост емкости кристаллов и функциональных возможностей кристалла. Считается, что этот рост подчиняется закону Мура: приблизительное удвоение числа транзисторов на кристалле каждые 2 года.

увеличение доли потребительского сектора в общем объеме выпускаемых электронных изделий.

до последнего времени главной целью было получение требуемых характеристик устройства реализующихся на кристалла. Главной характеристикой являлась производительность, в то время как длительность разработки и выпуска изделия на рынок не имели решающего значения.

большинство современных систем ЭВТ с функциональной точки зрения представляет собой баланс между программной и аппаратной частями.

обычно эти части разрабатываются отдельно друг от друга. В настоящее время, когда на весь цикл разработки устройства выделяется не более полугода (до запуска в производство), разработка программной и аппаратной частей производятся параллельно на основе технологий сквозного параллельного и нисходящего проектирования.

Верхний уровень проектирования включает функционально-логическое проектирование и верификацию полученных схем. Для цифровых и цифро-аналоговых систем особенностью является то, что с увеличением емкости кристалла до нескольких десятков тысяч вентилей и более, перестает работать обычный подход проектирования на вентильном уровне. Моделирование на вентильном уровне становится неприемлемым как с точки зрения затрат инженерного труда, так и с точки зрения требуемых ресурсов ЭВМ. Поэтому в настоящее время основной технологией моделирования является моделирование с помощью языков высокого уровня VHDLиVERILOG.

Типовой маршрут проектирования

в программном пакете RENOIRосуществляется графический ввод и генерация описания проекта на языкахVHDLиVERILOG.

в пакете ModelSim, предназначенного для моделированияVHDL,VERILOGи смешанных описаний проекта, производится моделирование работы реального устройства.

с помощью пакета LeonardoSpectrumвыполняется синтез логических схем на базе библиотек всех современных изготовителей ПЛНС (программируемые логические интегральные схемы) и АНС (аналоговые схемы).

перечисленные пакеты стали сегодня стандартом. Программное обеспечение берется на сайте.

В настоящее время резко возросла доля аналогово-цифровых проектов. Если в 1999 их доля была 22%, то в этом году рост прогнозируется до 67%. В области проектирования подобных систем одной из популярных является система Advance. В неё входят:

пакет аналогового моделирования AdvanceEldo;

пакет программно смешанного моделирования AdvanceMS;

пакет программного моделирования в разно частотном диапазоне AdvanceRfic.

Также в системы входят библиотеки моделей для телекоммуникационных приложений advanceCOMLIB.

В качестве входных языков системы advanceиспользуютсяVHDLиVERILOG. Также может использоваться С++.

Библиотеки системы включают модели аналогово-цифровых фильтров, фаз инверторов, конверторов данных, модуляторов, демодуляторов и цифровых блоков различного функционального назначения.

При параллельном проектировании программной и аппаратной частей необходима разработка виртуального прототипа, который на сегодняшний день создается с помощью пакета SiamlessCVE. Данный пакет позволяет отладить систему на различных этапах проектирования, оптимизировать проект, тоесть вносить изменения в проект на самых ранних этапах проектирования.

Среда пакета SiamlessCVEобеспечивает все функции программной и аппаратной средств, отладчиков исходного кода, просмотр содержимого регистров и памяти, окно просмотра принципиальных схем и логический анализатор. В этой среде возможно выполнение программ на языках С, С++ иAssembler. В настоящее время этот пакет поддерживает 60 микропроцессорных моделей и более 10 моделирующих программ.

На сегодня новые тенденции используют технологии повторного проектирования, тоесть используют проработанные проектные решения в виде поставки средств интеллектуальной собственности.

В системе MentorGraphicsв библиотеке макросов системы содержится более 30 компонентов, реализующих процессоры, контроллеры периферии, различные устройства цифровой обработки сигналов, кодеры и декодеры, шинные интерфейсы, мультимедийные сетевые схемы.

Новые тенденции в проектировании печатных плат

Система MentorGraphicsсодержит полный набор средств проектирования печатных плат: средства размещения, топологический редактор, средства трассировки и выдачи данных для изготовления платы и пакетInterConnecticsдля проектирования сверхбыстродействующих печатных плат. Все программы объединены в пакетBoardStation. Этот пакет позволяет производить размещение компонентов на плате, анализ электрических характеристик, включая анализ целостности формы сигнала, реальных задержек и помех, и может производить трассировку соединений с учетом межплатных соединений. Основным достоинством пакета является совмещение процессов размещения и трассировки соединений с одновременным анализом параметров результирующих соединений, что позволяет избежать повторных циклов при проектировании. Главной целью проектирования является выделение узловых наиболее трудоемких точек проектирования и направление всей интеллектуальной мощи на решение задач в этих точках с интеграцией всего маршрута проектирования в целом.

Лекция № 12 Методы обеспечения надежности электронных систем

Выбор конструктивного использования компонентов и создание топологии

На правильную работу электронных схем влияет технология монтажа компонентов на коммутационном поле, способы размещения и соединения компонентов между собой. Необходимо учитывать межплатные соединения. Для снижения уровня помех компоненты должны группироваться по уровню мощности и рабочим частотам. Печатные проводники должны иметь прямую форму (минимальное количество изгибов) и быть более короткими, так как в длинных проводниках различные паразитные помехи (емкостные и индуктивные наводки), а также может возникать эффект резонанса. Необходимо выделять отдельные слои для проводников земля и питание, а также контролировать ширину печатных проводников и зазоры между ними. Для предотвращения повреждения компонентов статическими зарядами, которые возникают при соприкосновении рук с печатной платой, проводники и компоненты устанавливаются на достаточном расстоянии от краев платы. Целесообразно, если позволяет пространство платы рядом с сигнальными проводить защитные проводники, обеспечивающие утечку заряда на землю.

Производственные дефекты компонентов

закоротка контактов конденсаторов гибридной микросхемы;

различные перемычки.

Для устранения этих дефектов производится испытание компонентов на воздействия температуры пайки, чтобы выявить и отбраковать изделия с избыточным количеством паяльной пасты.

Экранирование системы

Применяется для снижения воздействия электро0-магнитных помех. Принцип работы экрана заключается в поглощении или отражении электромагнитных и электростатических полей. На низких частотах магнитное поле поглощается, на высоких – отражается. Для защиты от низкочастотных магнитный полей рекомендуется использовать экраны из немагнитных материалов (алюминий, медь и т.д.). Материалы с высокой магнитной проницаемостью (железо, железоникелевые сплавы) используются для защиты от низкочастотных электромагнитных полей. Магнитная проницаемость этих материалов снижается с ростом частоты. Поэтому при высоких частотах эти экраны не эффективны.

Для экранирования экран должен быть сплошным вокруг всей системы / устройства. Допускается наличие отверстий диаметров, не превышающим λ/2, где λ – минимальная длина волны сигнала. В противном случае отверстия играют роль целевых антенн. Разъемы на плате тоже могут выполнять роль антенн, и их рекомендуется закрывать поглощающим материалом.

Все изолирующие материалы должны иметь достаточную диэлектрическую прочность. Необходимо экранировать кабели, соединяющие данную систему с другой. При этом оплетка кабеля должна иметь качественный контакт с корпусом. Для складирования электронных модулей необходимо использовать пластиковые пакеты с металлизированным покрытием, которые имеют высокую стойкость к воздействию температуры и влажности.

Оценка предотвращения тепловых повреждений

На начальном этапе проектирования необходимо наряду с анализом электронной схемы проводить тепловой анализ проекта, так как в системе существуют тепловые потоки от переходов в окружающую среду. Предельная температура переходов для полупроводниковых устройств общего назначения составляет 150 градусов. Чем ниже рабочая температура перехода, тем выше надежность устройства. Снизить температуру переходов во время работы оборудования можно с помощью специальных теплоотводов, охлаждающих вентиляторов или отверстий для естественной вентиляции. Эти меры применяются и для охлаждения других элементов схемы (конденсаторов, транзисторов, резисторов, реле и т.д.). Дополнительным испытанием тепла могут быть электрические нагрузки, которые должны быть выявлены в начале процесса проектирования. На тепловую нагрузку влияет температура окружающей среды. Для предотвращения влияния рассчитывается рабочий диапазон, а также проводятся тепловые испытания компонентов и всего устройства в целом.

Особенности теплового анализа проекта

Тепловой анализ проекта является неотъемлемым этапом проектирования, который выполняется в самом начале процесса проектирования, так как на более поздних стадиях проекта наличие теплового воздействия может вызвать пересмотр всего проекта.

Первым и наиболее важным моментом является выбор таких элементов, которые соответствуют рабочему диапазону температур заданным в техническом задании.

Второе – равномерное размещение тепловыделяющих элементов на коммутационном поле.

Третье – установка теплоотводов и организация вентиляции.

Необходимо учитывать, что мероприятия по обеспечению нормального теплового режима не должны приводить к неоправданному увеличению стоимости всего устройства, а должен быть выбран разумный компромисс.

К другим рекомендательным действиям по обеспечению нормального теплового режима относят:

чувствительность к нагревающим элементам (электролитические конденсаторы и полупроводниковые приборы необходимо размещать отдельно от интенсивных источников тепла, таких как проволочные резисторы, мощные диоды, транзисторы, регуляторы напряжения, установленные на тепло отводах);

вокруг теплоотводов должны быть созданы хорошие условия для циркуляции воздуха;

необходимо иметь в виду, что интенсивность охлаждения теплоотвода тем выше, чем выше площадь поверхности;

при необходимости можно делать вентиляционные отверстия, диаметр которых не должен приводить к источнику помех;

расчет тепловыделения необходимо производить для наиболее жестких условий эксплуатации;

необходимо учитывать, что установка теплоотводов и вентиляторов сама по себе поглощает внутреннее пространство устройства, что приводит к ухудшению условий вентиляции;

требования к охлаждению должны определяться назначением оборудования и степенью его надежности;

расчет тепловых процессов в системе производится с помощью автоматизированных систем, которые обладают необходимыми средствами для моделирования тепловых режимов;

как правило, проводится съемка рабочего макета печатной платы с помощью тепловизора в условиях предельной нагрузки с целью выявления наиболее тепловыделяющих частей и их расформирования по площади платы.

При разработке платы необходимо учитывать как тепловые воздействия, возникающие при работе схемы, так и тепловые воздействия, которым будет подвергаться плата или устройство в процессе пайки.

Способы оценки надежности и качества функционирования электронного оборудования

Надежности изделия необходимо прогнозировать до его запуска в производство. Для прогнозирования необходимы следующие данные:

обеспеченность инструкциями, измерительными приборами и испытательными стендами;

контроль качества материалов, полуфабрикатов и деталей, поставляемых внешними поставщиками;

классификация дефектов и качественных характеристик выпускаемых изделий;

систематический выборочный контроль изделий по показателям качества;

контроль над особыми условиями и видами производства;

наблюдение за нестандартными материалами и учет статуса их годности;

проведение специальных испытаний без разрушения проверяемых изделий.

При сопоставлении запланированного качества, определенного конструкторско-технологической документацией, и качества готового изделия соответствующая классификация дефектов определяется регламентирующими документами: технологическими инструкциями (карты, маршруты) и инструкциями по приемке изделия, тоесть их проверки, контроля и аттестации. Таким образом, формируются требования к стандартизованному уровню качества.

К числу основных стандартизованных оценок качества относят:

допустимый процент дефектов на 1 изделие, если оно сложное или дефектных изделий на партию из 100 штук, если изделие простое;

уровень среднего выходного качества, которое устанавливают на основе расчета плана выборочного контроля или ускоренных испытаний;

допустимое число взвешенных дефектов, приходящихся на одно изделие.

Для расчета причинных оценок используют:

статические данные за некоторые предшествующие периоды для расчета средних значений параметров качества и обоснования стандартизованных норм;

данные, накопленные в процессе опытов, исследований или испытаний для расчета норм качества для изделия и аналогов;

значение параметров, характеристик, технические требования, предъявленные к качеству изделия, в том числе данные анализа затрат на обеспечение качества.

Современная практика показывает, что:

общий уровень качества изделия при отсутствии стандарта примерно на 25% ниже, чем при действующем стандарте;

целесообразно установить стандарт, используя данные предшествующих периодов в пределах до 80% от расчетного среднего значения;

наиболее предпочтительными для расчета стандартов представляются данные, полученные на основе опытов и испытаний. Стандарты, основанные на технических требованиях, нормах и рассчитанных ранее значений параметров, дают большой выигрыш потребителю и чрезмерно ограничивают производителя;

экономически выгодные оценки, нормы и стандарты качества, учитывающие минимум затрат на обеспечение качества, рассчитываются путем поиска оптимальных решений в конкретных условиях производства изделия.

Лекция № 13 Надежность изделия

Надежность изделия должна обеспечиваться во время всего срока эксплуатации изделия. Динамика процесса эксплуатации изделия представляется 3-мя фазами: отладкой, эффективной нормальной работой и старением (период ремонтов).

Отладка:характеризуется коротким периодом времени, резким сокращением числа отказов, благодаря замене некачественных деталей, устранению ошибок сборки.

Нормальная работа:характеризуется длительным временем, включающим гарантийный срок безотказной работы. На этом этапе уровень отказов очень низкий и они носят случайный характер. Этот период обеспечивает ценовую политику производителя и риск потребителя.

Старение:характеризуется высоким уровнем отказов в связи с износом элементов, старением материалов, изменением их прочностных свойств.

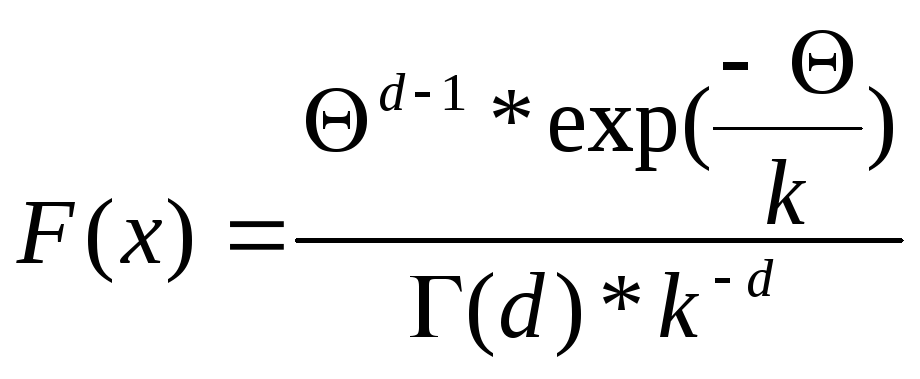

Отказ на каждом этапе эксплуатации изделия описывается с помощью отдельных законов распределения случайных величин. Для описания первой фазы наиболее часто используется гамма распределение, для второй фазы – экспоненциальное распределение, для третей фазы – нормальное распределение или суперпозиция нормального и экспоненциального распределения. Для оценки надежности выполняется преобразование распределений для получения плотности распределения вероятности отказов.

Гамма распределение

![]()

После преобразований

Где x– случайная величина,a,b– параметры распределения, Г – гамма функция,k– формообразующий параметр кривой распределения,d– частота появления отказа, Θ – срок службы изделия.

Планом выборочного контроля изделия по сроку службы можно представить в виде планов контроля безотказности, добавив внешнюю нагрузку и приняв в качестве допущения, что после фазы отладки следующая фаза подчиняется экспоненциальному распределению. При этом возможны следующие варианты организации испытаний с целью оценки безотказности как среднего срока службы изделия:

испытания заканчиваются после фиксации заранее установленного срока отказов. При этом используются значения приемлемого и неприемлемого срока службы изделия для сравнения;

испытания заканчиваются по истечении заданного времени Tс заменой или без замены оставшихся элементов. Извне задаются следующие параметры: объем выборкиN, приемлемый срок службы изделия, установленное время проведения испытанийT.

По результатам испытаний для определенного вида изделия могут составиться сводные данные для различных режимов и периодов эксплуатации. Если далее оценивается надежность изделия, относящихся к типу изделий для которых уже составлены справочные данные по испытанию, выбираются соответствующие показатели надежности без нового проведения испытаний, что экономит временные затраты при производстве изделия.

Отбраковочные технологические испытания как средства повышения надежности партии интегральных микросхем

К качеству и надежности интегральных схем предъявляются высокие требования, независимо от места использования. Подсчитано, что при доле дефективности партии интегральных схем в пределах 0,01%, тоесть 100 схем на 1 млн. постоянных процентов отказов печатных плат, на которых смонтировано 100 интегральных схем, составляет более 9%. При дефективности партии интегральных схем в пределах 1% выход годных печатных плат составит 63,4%, тоесть брак составит 36,6%.

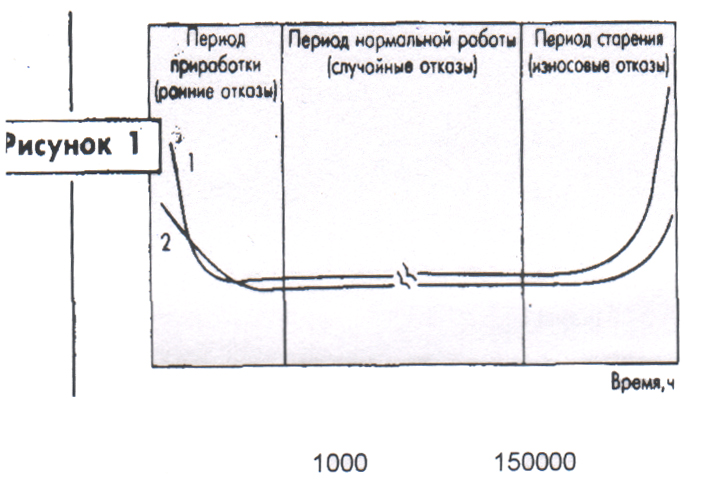

Надежность ИС при эксплуатации характеризуется кривой зависимости интенсивности отказов λ от времени.

Первая зона (1) – период обработки, вторая зона (2) – нормальная работа, третья зона (3) – отказ/износ.

На этой кривой видно относительно высокое значение λ. В период ранних отказов сравнительно низкое и постоянное значение в период эксплуатации, и возрастающая интенсивность в период износа.

Ранние отказы возникают, как правило, вследствие конструктивных и технологических недостатков. В нормальном условии работы этот период длится до 1 тыс. часов (6 недель). На окончание этапа указывает выравнивание кривой интенсивности отказов. Интенсивность отказов в период приработки имеет тенденцию к уменьшению по мере совершенствования конструкции и технологии интегральных схем.

В настоящее время общепринятыми считаются 2 направления увеличения надежности выпускаемых интегральных схем:

Выявление и удаление изделий с отказами действительными и потенциальными из готовой партии до поставки потребителям.

Устранение причин отказов за счет совершенствования конструкций и технологий изготовления, тоесть воздействие на процесс производства посредством обратной связи, тоесть передачи информации от эксплуататоров в производство, а это ведет к разработке бездефектных технологий. Этот метод является наиболее эффективным.

Одним из эффективных способов повышения надежности партии ИС является выходной контроль партии на заводе изготовителя, тоесть проведение отбраковочных испытаний. Считается, что случайных отказов интегральных схем не бывает. Каждый имеет причину и является следствием приложенной нагрузки. Для того, чтобы отбраковочные испытания были эффективнее, необходимо знать, какие нагрузки и как ускорить появление отказов.

График

влияния отбраковочных испытаний на

интенсивность отказов, где:

График

влияния отбраковочных испытаний на

интенсивность отказов, где:

0 –момент поставки заказчику, 1 –без отбраковочных испытаний, 2 – только электрические испытания, 3 – стабилизирующая тренировка, циклические температурные испытания и проверка электрических параметров, 4 – стабилизирующая тренировка, циклические температурные испытания и проверка электрических параметров, а также тренировка в утяжеленных режимах.

На сегодня применяются такие виды отбраковочных испытаний:

контроль внешнего вида;

электрические испытания;

повышение температуры;

термоциклы;

вибрация;

одиночные удары;

многократные удары;

центрифуга;

испытания на герметичность;

рентгеноскопия;

тепло энерго тренировка; 12. энергоциклы; 13. повышение влажности.

Многие различные по природе дефекты приводят к одним и тем же механическим отказам. Многие одинаковые механизмы отказов ускоряются различными нагрузками и многие различные механизмы отказов одними и теми же нагрузками. В частности воздействие на ИС повышенной температурой и термоциклы ускоряют отказы.

Термоциклы (попеременный нагрев и охлаждение) хорошо выявляют негерметичность корпуса. А также выявляются напряженные места конструкции, склонные к образованию дефектов корпуса ИС. Помимо тепловых и термоциклических испытаний используют механические испытания с постоянной или изменяющейся нагрузкой, которые могут выявить дефекты монтажа кристалла, внутренних соединений, соединений корпуса ИС или внешних выводов. В общетехнических (ОТУ) и технических условиях (ТУ), как правило, указывается состав обязательных отбраковочных испытаний, их режимы и последовательности. Заводы изготовители интегральных схем расширяют состав испытаний в начальный период серийного производства. Их число снижается по мере сбора статистики. Может корректироваться вся программа испытания, но кроме тех, которые указываются как обязательные в ОТУ и ТУ.

Лекция № 14 СОСТАВ ОТБРАКОВОЧНЫХ ИСПЫТАНИЙ ИС В ОТЕЧЕСТВЕННОЙ ПРОМЫШЛЕННОСТИ

Во всех отечественных регламентирующих документах по выпуску ИС имеется указание, что в процессе изготовления должны проводиться 100% отбраковочные испытания. Состав обязательных 100% испытаний включает до 20 видов по СОТУ, не менее 10 видов по ОТУ на ИС с приёмкой заказчика и не менее 10 видов по требованию на ИС широкого применения. Методика и условия испытаний описаны в ОСТ.

Таблица: Виды и методы отбраковочных испытаний.

|

Вид испытаний, технологическая операция |

Условия испытаний |

Состав испытаний [6] [7] [8] |

|

Визуальный контроль кристалла |

Увеличение в 200 раз Увеличение в 100 раз Увеличение в 80 раз |

+ + + |

|

Контроль монтажа кристалла |

По ТД* |

+ + + |

|

Контроль прочности крепления кристалла |

Выборочно по две схемы от каждой установки в начале схемы и через каждые два часа |

+‑ ‑ |

|

Контроль прочности сварного соединения |

Выборочно по две схемы от каждой установки в начале схемы и через каждые два часа |

+ + - |

|

Визуальный контроль сборки перед герметизацией |

Увеличение не менее, чем в 32 раза |

+ + + |

|

Термообработка сборки перед герметизацией |

48ч при 150 С |

+ + + |

|

Герметизация |

В контролируемой инертной среде |

+ -- |

|

Термообработка для стабилизации параметров |

24 ч при верхнем значении температуры по ТУ |

+ + + |

|

Испытания на воздействие изменения температуры среды |

10 циклов от –60 до +150"С 10 циклов от –60 до верхнего значения температуры по ТУ |

+ - + + |

|

Испытания на воздействие линейного ускорения |

ЗООООg |

+- - |

|

Контроль свободного перемещающихся частиц внутри корпуса по уровню шума |

По ТД |

+- - |

|

Промежуточные электрические испытания: контроль статистических параметров при нормальных климатических условиях |

По ТД |

+ + + |

|

Электротермотренировка |

240 ч (для МДП – схем), 168 ч (для биполярных схем) |

+ + + |

|

Промежуточные электрические испытания: контроль статистических параметров при нормальных климатических условиях |

По ТД |

+ + + |

|

Электротермотренировка при обратном смещении |

72 ч. Устанавливается в ТУ на отдельные МОП и линейные ИС, в которых возможны поверхностные явления |

+- - |

|

Заключительные электрические испытания: Проверка статистических, динамических параметров и функционирование при нормальных климатических услов.; пониженной рабочей темп, среды; повышенной рабочей темп, среды |

По ТД |

+ + + + + - + + - |

|

Рентгеновский контроль |

По ТД |

+ - - |

|

Проверка герметичности |

Для полых корпусов |

+ + + |

|

Контроль внешнего вида |

По ТД |

+ + + |

В технически обоснованных случаях по согласованию со службой контроля качества допускается иная последовательность отбраковочных испытаний, а вместо проверки статических параметров (параметров постоянного тока) при крайних значениях температуры проводят проверку параметров при нормальных климатических условиях по нормам, обеспечивающим установленные значения параметров при критических значениях температуры.

При разработке регулирующего воздействия, связанного с коррекцией состава, методов или условий проведения отбраковочных испытаний, вырабатываемых на основе информации о причинах отказов ИС, учитывается взаимосвязь между причинами отказов и видами отбраковочных испытаний, с помощью которых выявляются эти виды отказов.

Требования к отбраковочным испытания ИС за рубежом

Наиболее отработанной в настоящее время является методика отбраковочных испытаний, предусмотренная стандартом США MIL-STD-883.

Таблица: Последовательность отбраковочных испытаний ИС по США MIL-STD-883

|

Метод испытания и его номер по МIL – STD –883 |

Значение параметров воздействия для классов надёжности Условия испытания А Условия испытания В Условия испытания С | ||

|

Визуальный контроль перед герметизацией |

Проводится |

Проводится |

Проводится |

|

Выдержка при высокой температуре, 1008 |

150 С |

150°С |

150°С |

|

Тепловой удар, 1011 |

10 или 5 ударов от 0 до+100°С |

— |

— |

|

Теплоциклирование, 1010 |

10 циклов от –65 до +150°С |

10 циклов от –65 до+150°С |

10 циклов от –65 до +150°С |

|

Механический удар |

20000g |

- |

- |

|

Центрифугирование, 2001 |

ЗООООg |

ЗООООg |

ЗООООg |

|

Герметичность, 1014 |

Проверяется |

Проверяется |

Проверяется |

|

Электрические параметры при крайних температурах |

Измеряются |

|

|

|

Термоэлектротренирвка |

125 С, 240ч |

125 С, 168ч |

- |

|

Рентгенографический контроль,2021 |

Проводится |

— |

— |

|

Контроль внешнего вида,2009 |

Проводится |

Проводится |

Проводится |

Требования по отбраковочным испытаниям классифицируются по трём уровням качество и надежности:

класс А — включает только схемы повышенной надёжности, предназначенные для работы в жестких режимах внешних воздействии;

класс В — включает надежные для промышленного применения схемы (и некоторые типы схем для военном аппаратуры), предназначенные для работы в менее жёстких условиях, когда главным требованием является стабильность параметров в течение длительного времени;

класс С — включает схемы для условий работы, когда воздействующие факторы не являются определяющими и на первое место ставится минимальная стоимость.

Военный стандарт МIL-STD-883 явился основой для разработки большого числа программ обеспечения надёжности РЭА, изготовляемой различными фирмами США и других стран.

Опыт использования ИС в аппаратуре показывает, что внедрение отбраковочных испытаний существенно повышает средний уровень надёжности партий ИС, однако для ряда схем некоторые предусмотренные стандартом отбраковочные испытания оказываются недостаточными. Кроме того, некоторые из принятых в настоящее время отбраковочных испытаний имеют отдельные недостатки.

Таблица: Характеристики отдельных видов отбраковочных испытаний

|

Отбраковочные испытания

|

Преимущества

|

Недостатки

|

|

Визуальный контроль при помощи растрового электронного микроскопа |

Обеспечивает видеозапись наихудших случаев нарушения целостности покрытия |

Субъективный приёмочный критерий. Дорогостоящий метод, требует затрат времени |

|

Выдержка при высокой температуре |

Стабилизирует коэффициент усиления транзисторов. Помогает выявить проколы в оксиде и дефекты, связанные с нестабильностью оксида |

Неэффективна для отбраковки большей части МОП ИС |

|

Тепловой удар |

Выявляет дефекты, связанные с негерметичностью корпуса, а также дефекты систем печатных плат и проволочных соединений |

Возможно повреждение корпуса больших размеров |

|

Механический удар |

Гарантирует стойкость ИС к рассчитанным механическим напряжениям |

Дорогостоящий метод, требует затрат времени. Возможно повреждение корпуса. |

|

Постоянное ускорение |

Гарантирует стойкость печатных и проволочных соединений к заданным механическим напряжениям. Даёт хорошие результаты для систем металлизации с золотыми выводами |

Неприменим для всех систем с алюминиевыми выводами в виду малой величины вызываемых усилий. Дорогостоящий метод, требует затрат времени. Возможно повреждение корпуса. |

С учётом рассмотренных выше недостатков отдельных отбраковочных испытаний, фирма SOLID STATE SCIENTIFIC для устранения потенциально ненадёжных КМОП ИС серий 4000, 4400, 4500 проводит в процессе изготовления следующие отбраковочные испытания ИС в герметичных керамических корпусах:

визуальный контроль перед герметизацией;

выдержка при температуре 200°С в течении 24 часов;

термоциклирование (10 циклов от –65 до +150°С);

функциональные электрические испытания;

измерение электрических параметров;

термоэлектротренировка при температуре 125°С в течение 168 часов.

В таблице представлены для примера состав и стоимость 100-% отбраковочных испытаний толстоплёночных гибридных схем, выпускаемых фирмой ВЕСКМАNN INSTRUMENT.

Таблица: Отбраковочные испытания толстоплёночных гибридных схем, выпускаемых фирмой ВЕСКМАNN INSTRUMENT.

|

Вид испытаний |

Условия |

Метод по МIL – STD –883 |

Стоимость испытания одной схемы, фунты стерлингов |

|

Визуальный контроль до герметизации |

Национальные ТУ Уровень А Уровень В Уровень С |

2000 Уровень А 2010 Уровень В 21 10 Уровень С |

0,1 |

|

Термостабилизация |

150 С Уровень А, 48ч Уровень В, 24ч |

1008 |

0,08 |

|

Термоциклирование |

10 циклов от –55 до 125°С Уровни А и В |

1010 |

0,17 |

|

Термоудар |

15 циклов от –55 до 125 С Уровень А |

1011 |

0,12 |

|

Центрифугирование |

20000д, 1 мин. Уровень А |

2001 |

0,22 |

|

Механический удар |

1 импульс, 1500д, 1 мс Уровень А |

2002 |

0,30 |

|

Вибрация |

20д при 50 Гц 96 ч (по 32 ч на плоскость) |

2005 |

0,50 |

|

Вибрация переменной частоты |

20д при 20 Гц – 20 кГц, 3 цикла (на каждую плоскость) |

2007 |

0,30 |

|

Рентгенография |

Негатив в одной плоскости Уровень А |

2012 |

0,15 |

|

Электротермотрени ровка |

Номинальная мощность, 168 ч при 125°С |

1015 |

0,70 |

|

Проверка на грубые течи |

До 103 см3/с, фреон, 30 с |

1014 |

0,06 |

|

Проверка на тонкие течи |

107 см3/с, гелиевый масс-спектрометр Уровни А и В |

1014 |

0,10 |

|

Прогон по температурному диапазону в электрическом режиме |

Испытания на функционирование, воздействие фреона на граничных температурах |

- |

0,07 |

Лекция № 15 О подходе к выбору инструментальных средств для автоматизированного проектирования печатных плат

Один из ключевых вопросов для организации интегрированной САПР/АСТПП/САИТ (для каждой проектной процедуры есть несколько алгоритмов, в системе которых выбирают наиболее рациональный) это выбор EDA(electronicdesignautomation) инструментов проектирования.

Основными факторами, которые принимаются во внимание при определении базового EDAинструмента, являются:

возможность решения широкого спектра задач конструирования печатных плат ЭВТ;

наличие интерфейса между выбираемым инструментом и используемым на предприятии (P-CAD,Caddy,MentorGraphics,Cadence,AccelEDA);

возможность выполнения проектов для сегодняшних и перспективных технологий производства ЭВТ, включая проектирование заказных интегральных схем и технологию с поверхностно – монтируемыми компонентами (ТПМК);

возможность использования локальных сетей предприятия;

наличие интерфейса с EDAинструментами, используемыми другими отечественными и зарубежными предприятиями, имеющими совместные проекты;

стоимость выбираемого инструментального средства.

Решение проблемы проектирования печатных плат EDA инструментами

Применение СБИС с высокими тактовыми частотами (свыше 50 ГГц) и ТПМК коренным образом изменило подход к проектированию ПП. Разработчику приходится анализировать широкий круг задач, включая: временные задержки сигналов, эффекты их взаимодействия при отражениях, искажения франтов тактовых импульсов, рассеиваемую мощность, электромагнитное излучение и влияние указанных параметров на размещение элементов и трассировку межсоединений на плате.

Процедура размещения и трассировки с учетом эффектов искажений сигналов

При работе в наносекундном диапазоне цифровые сигналы по своей форме приближаются к аналоговым. Кроме этого при анализе искажения сигналов необходимо учитывать временные задержки при их передаче, паразитные положительны и отрицательные выбросы, перекрестные помехи и случайные превышения логических порогов срабатывания. Причиной этих искажений являются паразитные цепи, обусловленные особенностями корпусов компонентов, разъемов, собственной и взаимной емкостью, и индуктивностью проводников и металлических отверстий в многослойных ПП, а также отсутствием согласованного выходного сопротивления передающего устройства с нагрузочным, включая сопротивление печатного проводника. Так как сегодняшняя плата это трехмерная структура, то и выбирать инструмент надо с учетом возможности проведения расчетов в 3-х мерном пространстве. Таким образом, процедуры размещения и трассировки должны выполняться в зависимости от временного анализа сигналов, зависящих от топологии передающих линий и моделей монтируемых на плате элементов.

Сегодня существуют 2 подхода к решению этой задачи:

Синтез межсоединений;

интерактивный процесс трассировки с возможностью многократной реализацией цикла "трассировка – анализ – трассировка".

Синтез межсоединений

IC(interconnectsynthesizer) состоит из 3-х модулей:

модуль исходных правил, задающих временные отношения и допустимые искажения сигналов;

интерактивный планировщик, размещающий компоненты или их группы в зависимости от исходных правил;

инструмент анализа сигналов и трассировки, использующий информацию от всех предыдущих модулей.

Список исходных правил включает допустимые величины временных задержек сигналов, завалов франтов импульсов, времен установки, перекрестных помех, положительных и отрицательных выбросов и фона сигнальных шин и шин питания. Все исходные данные о проекте можно вести в редакторе SchematicEditor, применяемогоEDAинструмента, или вHDL(hardwaredescriptionlanguage) формате.ICанализирует описание схемы и ограничения и на основе этого анализа определяет пути трассировки. При этом выполняется моделирование, основанное на решении нелинейных уравнений передающих линий. Иерархический планировщик может группировать элементы в соответствии с заданными требованиями. При замене компонента осуществляется пересчет параметров всех сигналов и выдается сообщение и нарушении, если они появляются.

Для моделирования эффектов искажения сигналов на ПП требуются модели входных выходных буферов элементов передающих и принимающих сигналов.

На практике используется 2 формата описания этих моделей: SPICEформат иIBIS(inputoutputbufferinformationspecification) или формат поведенческого описания. Некоторые компании предлагаютSPICEмодели производимых или интегральных схем, однако, они не всегда отслеживают модификации схем. При моделировании ПП с сотнями или тысячами входных выходных буферов используемыеSPICEмодели становятся неэффективными из-за больших затрат машинного времени. Поэтому на сегодня наибольшее распространение получили модели вIBISформате, основанные на вольтамперных характеристиках устройства, данные о времени нарастания и спада сигнала на его выходе и информации об упаковке вентилей на уровне выводов. Поведенческие модели требуют значительно меньших затрат машинного времени, чемSPICEмодели, и позволяют пересчитывать множество нелинейностей, обусловленных конструкцией буферов.

IBIS, как стандарт для поведенческих моделей, был введен фирмойIntel. В настоящее время многие фирмы производители интегральных схем иEDAинструментов поддерживаютIBISмодели совместимые с большинством платформ моделирования. КомпанияZEELANTechnology, входящая сегодня вMentorGraphics, предлагаетIBISмодели примерно 8800 компонентов, которые используются большинствомEDAинструментов. Если в библиотеке отсутствует та или иная модель он может создать её, используя инструментIBISGoldenParser. Также компанияHyperLynxпредлагает редакторVisualIBISEditor, который можно получить поInternet.

Интерактивный процесс трассировки с возможностью многократной реализацией цикла "трассировка – анализ – трассировка"

Производится с использованием инструмента PCB/MCMSignalIntegrityфирмойPacificNumerics, который считывает БД трассированной платы в 3Dструктуре, рассчитывает частотно зависимые сопротивления, собственные взаимные емкости и индуктивности для каждой трассы и переходного отверстия и создает файл вSPICEформате. Этот файл совместно с моделями элементов используется для моделирования любымEDAинструментом, содержащимSPICE. Если выявляется нарушение допустимых уровней, то об этом сообщается пользователю. Затем плата снова перетрассируется. Снова повторяется процедура анализа и трассировка, пока не будет нарушений.

В настоящее время оба подхода к конструированию ПП широко используется, однако, финансовые трудности и технические трудности иногда определяют выбор второго пути, хотя, наиболее перспективным является первый подход.

Лекция № 16 Некоторые практические рекомендации для проектирования ПП в наносекундном диапазоне

В несогласованных линиях связи (что, как правило, бывает при соединении печатных проводников выхода одной ИС с входом другой) возникают недопустимые наложения сигналов из-за отражений, если логический перепад на выходе источника сигнала отработается раньше, чем на этот выход возвращается первый отраженный фронт сигнала от приемника.

Критической является передающая линия, длина которой определяется из выражения:

Lкр=tp / 2*Tp [мм]

где tp– длительность фронта импульса [нс],Tp– задержка распространения сигнала в линии [нс/мм].

Ориентировочные длины линий связи для интегральных микросхем различного типа имеют следующие значения в мм:

|

№ |

ТИП ИС |

Критическая длина проводника [мм] |

|

1 |

Стандартные ТТЛ |

373,6 |

|

2 |

ТТЛ с диодом Шотке |

142 |

|

3 |

ЭСЛ |

186,7 |

|

4 |

КМОС схема |

52,3 |

|

5 |

ЭСЛ с временем нарастания 0,5 нс. |

37,4 |

|

6 |

GaAS |

22,4 |

Анализ наводов ЭМИ от высокочастотных электронных устройств

Уровень электромагнитного излучения (ЭМИ) зависит от тактовой частоты, скоростей нарастания и спада импульсного сигнала, положительных и отрицательных паразитных выбросов, длины и конфигурации печатных проводников. Сейчас разрабатывается 2 модели ЭМИ ПП: дифференциальная и обычная.

Дифференциальная модель обусловлена наличием петель на ПП. Эта петля образуется током, протекающим от передатчика по печатному проводнику к приемнику и обратно по земляному проводу. Это излучение можно уменьшить, сокращая токовую петлю за счет конструирования проводника как можно наименьшей длины.

Обычная модель ЭМИ обусловлена палением напряжения на печатном проводнике, которое определяется по проводнику током. Часть этого тока могут составить такие утечки, обусловленные паразитными емкостями передающих линий. Для уменьшения этой составляющей ЭМИ необходимо уменьшить длину проводника и минимизировать паразитные емкости.

Современные EDAинструменты используют следующую методологию расчета ЭМИ ПП:

анализ поперечного сечения печатных проводников и разработка модели передающих линий;

создание модели цепи для каждой трассы, включая приемники и передатчики;

расчет токов в трассах;

преобразование временной зависимости рассчитанных токов в частотную с целью получения соответствующего спектра;

использование теории "антенн" для вычисления электрического поля на заданном расстоянии от ПП.

Современные EDAинструменты для вычисления ЭМИ ПП различаются стоимостью, возможностями и точностью вычислений. Сегодня наиболее низкую стоимость имеет инструментSpectroSim, примерно 1000$, использующий частотный анализ токов на уже оттрассированной плате, и далее, используя эти данные, определяются трассы, которые являются источниками ЭМИ помех. Пользователь может контролировать параметры трассировки, такие как ширина диапазона частотами и его центр. Далее данные представляются в логарифмическом виде. Инструмент используетсяIBISмоделями приемника и передатчика или модели из собственной библиотеки.

Наиболее дорогостоящий инструмент AnsoftMaxwellSiEminence, он стоит 50000%. Позволяет производить расчет анализа ЭМИ с расчетом искажения сигналов. Для расчета перекрестных помех, задержек при передаче сигнала, отражений сигналов. ИспользуяSpiceмодели буферов. При анализе ЭМИ производится расчет электромагнитного поля в трехмерном пространстве и для различных времен нарастания и спадов импульсов.

Анализ распределения температур по ПП

При работе на высоких частотах увеличивается мощность рассеяния, что необходимо учитывать, так как уменьшается расстояние между элементами на плате и расстояние между элементами и платой, и потому что уменьшаются размеры элемента. Для принятия решения о необходимости принудительного воздействующего охлаждения или использования специальных теплоотводящих конструкций нужна информация о распределении температур по поверхности платы. Эта информация предоставляется программами исследования температурного диапазона, использующими модели ПП и элементы.

Наиболее распространенным элементом является BetaSoftBoard(компанияDynamicSoftAnalysis) в который входит 2500 моделей элементов. На экране проявляется цветная карта распределения температур. Этот инструмент исследует тепловое излучение, конвекцию и теплопроводность.

Особенности EDA инструментов для проектирования плат по технологии ТПМК

Многие инструменты, ориентированные на обычные ПП, не приемлемы для ТПМК, так как элементы устанавливаются по обе стороны платы. Значит, алгоритмы размещения должны давать возможность перемещать элементы по одной из поверхностей, но и перемещаться между поверхностями. При этом необходимо обеспечивать визуализацию топологии верхней и нижней стороны платы одновременно.

Программы трассировки должны обеспечивать сочетание различных приемов проектирования: варьировать ширину и шаг печатных проводников, что позволяет использовать менее узкие дорожки и увеличивать расстояние между ними, там, где это необходимо. Также имеют место особенности при проектировании межслойных переходов шин питания. Сегодня из этой ситуации выходят, применяя интерактивыне методы трассировки.

Современные EDA инструменты для проектирования ПП

AllegroStudio(производительCadenceDesignSystems) на сегодня наиболее полный для проектирования ПП от этапа разработки проекта до выхода на производство.AllegroStudioполностью совместим со всеми пакетамиcadenceи включает в себя:

conceptHDLдля иерархического создания проекта и схемного вывода;

PELibrarianдля создания библиотек управления;

система топологического проектирования AllegroPCBдля размещения, трассировки и выхода на производство ПП;

редактор Specctraдля интерактивной полуавтоматической трассировки;

авто трассировщик Specctraдля контурной автоматической трассировки.

Создание проекта Concept HDL

ConceptHDL – это многоуровневая смешанная среда проектирования, которая позволяет разработчику вводить информацию как на поведенческом, так и на структурном уровне описания проекта.ConceptHDL обеспечивает согласованную работу групп разработчиков, поддерживая технологию нисходящего проектирования. Он предоставляет графические средства управления иерархией и конфигурации проекта. Браузер компонентов позволяет быстро найти требуемый для проекта элемент на основе логических или функциональных ограничений. В дополнение функция глобального поиска дает возможность быстро локализовать определенные элементы или отследить желаемые сигналы по схемным листам на любых иерархических уровнях проекта.

Управление библиотеками PE Librarian

Включает 3 пакета:

создание описания логических элементов;

создание конструкций физических элементов;

управление модификациями и версиями библиотечных данных.

Библиотека Allegroпозволяет воспроизводить физические корпуса элементов, контуры ПП и чертежи с детальной установкой размеров для выхода на производство.

Система топологического проектирования PCB

В систему вводится понятие "концепция проектирования" или управления исходными правилами. С помощью механизма встроенных правил, разработчики могут сконцентрироваться на физической топологии, в то время как инженерные требования поддержки и контроля автоматизируются. Конструкторы могут разделять плату на области, в которых отдельно будут контролироваться электрические, температурные и конструктивные исходные правила. Любые изменения на физическом уровне топологии путем нажатия одной кнопки передаются на уровень схемного ввода. Следовательно, схема и ПП полностью соответствуют друг другу.

Берет на себя все функции размещения и топологического проектирования.

Лекция № 17 (Продолжение лекции №16)

Интерактивный трассировщик Specctra(фирма "Cooper and Chyan")

Редактор трассировки Specctraпозволяет использовать при редактировании проводников и межслойных переходов уникальные возможности: функцииplowing,showing,ghosting. При прокладке новых трасс свойствоplowingпозволяет автоматически "расталкивать" существующие трассы в стороны. Используя свойствоshowing, конструктор может сдвигать сегменты трасс или переходные контакты на существующие трассы и продолжать трассировку поверх и через другие выводы и переходные контакты. Свойствоghostingпозволяет делать оценку сценариев типа "что будет, если". Когда элемент трассы (сегмент) или переходные контакты сдвигаются курсором, окружающей трассы отталкиваются и высвечиваются динамические.

Разработчик оценивает изменение, перед тем как согласиться с новой конфигурацией. Многоуровневая отмена действий позволяет вернуться к предыдущим конфигурациям трассы. При размещении переходных контактов при тактах спектра высвечивает близлежащие дозволенные места и позволяет разработчику добавлять переходы двойным щелчком мыши. Поддерживается как ортогональная трассировка, так и под любым углом.

Свойство criticпозволяет удалять лишние изгибы трасс в определенной области или по всей плате для улучшения возможности производства.

Авто трассировщик Specctra

Автоматический трассировщик Specctraсоздан для работы с печатными платами высокой плотности. Его диагональные алгоритмы трассировки работают как в бессеточном, так и в сеточном режиме и обеспечивают высокую степень завершения трасс и способы работать с областями нестандартных размерностей, которые ранее требовали ручной трассировки.

Оба трассировщика Specctra(автоматический и интерактивный) тесно интегрированы сAllegroPCBчерез интерфейсSPIF. Это позволяет передавать ограничения и правила проектирования изConceptHDLиAllegroPCBв автоматизированный трассировщикSpecctraдля их выполнения.

В AllegroStudioтрассировщик позволяет трассировать до 6 сигнальных слоев. А вообще, трассировщик предлагается без ограничений числа сигнальных слоев.

Выход на производство

Система AllegroStudioобеспечивает следующие возможности для производства:

уменьшение ступенчатости проводников и удаление лишних отводов;

улучшение соединений в площадке и центрирование проводников между площадками;

автоматическая трассировка каплевидных контактных площадок;

автоматическое удаление шелкотрафарета со сверловочных отверстий и контактных площадок;

автоматическое удаление лишних переходных контактов;

переименование обозначений элементов на схеме или плате в соответствии с заданным пользователем критерием;

автоматическая генерация спецификации материалов;

подготовка сборочных чертежей для сверления и производства;

автоматическая простановка размеров;

обеспечивает растровые форматы Gerber,DPFиMDAдля фотоплоттеров;

поддержка стандартного формата Gerber;

поддержка интерфейсов DXFиIDF;

чтение файлов, фототрафаретов и списков цепей для создания интеллектуальных БД.

От P-CAD к Accel EDA

В настоящее время наиболее распространенным является продукт P-CAD8.5 (MasterDecision).

Этот продукт объединяет лучшие свойства пакетов P-CADиTangoPro. Этот пакет состоит из двух отдельных пакетов:AccelP-CADPCBдля проектирования плат высокой сложности иAccelTangoProдля проектирования плат малой и средней сложности.

При вводе списка цепей осуществляется автоматически извлечение из библиотеки корпусов компонентов с автоматической упаковкой по логическим элементам для последующего размещения. В процессе размещения конструктор может выделять связанные границы компонентов.

AccelEDAиспользуют различные трассировщики, как сеточные, так и бессеточные, собственный разработчик и два высокопроизводительных автотрассировщикаSpectra. ВAccelEDAпроектирование печатных плат не ограничено исходными правилами в отличие отAllegroStudio.

Пути развития

Главная проблема проектирования печатных плат в настоящее время – неадекватность моделирования в горизонтальной и вертикальной областях. Моделирование с горизонтальной плоскости основывается на моделях, содержащих информацию о компонентах (физическая, электрическая, тепловых режимов) включая информацию об искажении сигналов электромагнитных помехах и другие. Моделирование вертикальной плоскости предполагает исследование интегральных схем, пассивных компонентов и самой печатной платы в единой программе исследования, которая в настоящее время отсутствует.

Необходим поиск новых стандартов, пригодных для моделирования в горизонтальных и вертикальных областях. Необходимы новые EDAинструменты или расширение существующих, позволяющие проектировать печатные платы, используя сложные модели в единой среде.

Проектирование вычислительных устройств с помощью VHDL

С помощью VHDLпроще и быстрее вести и проверить большой проект.

Десятью строками VHDLможно описать как 1 так и 100 тысяч элементов. Микросхемы с интеграцией более 10 тысяч вентилей разрабатываются только с помощьюVHDL, так как задача масштабна.

Проект на VHDL– это объединение структуры вычислительного устройства и алгоритма его функционирования. Для вычислительного устройства, описанного наVHDL, не обязательно выполнять проверку правильности функционирования с помощью макетирования. Чтобы проверить правильность работы вычислительного устройства достаточно запуститьVHDLпрограмму в симулятореVHDL. Современные САПР преобразуютVHDLв комплект документации для изготовления работоспособного устройства. Проект наVHDLсамодокументированный, тоесть не требует дополнительного технического описания, или в виде схемы.

Отсутствие ошибок при проектировании достигается за счет автоматической проверки правильности функционирования устройства на основе его VHDLописания. Синтаксическая проверка моделирования и компиляция в логическую схему быстро выявляет ошибки проекта.

Разработанный на VHDLпроект является универсальным. Описание блока (устройства) наVHDLможет быть использовано во многих других проектах. При этом многие структурные и функциональные параметры блока могут быть настраиваемыми: разрядность, объем памяти, элементная база, состав блока и структура межсоединений.

Проект на VHDLразработанный на одной элементной базе переносится без труда на другую элементную базу. Проект наVHDLэто долгоживущий проект, так как проект делается под определенную элементную базу, которая каждые полтора года меняется, а средстваVHDLпозволяют переходить на более современную элементную базу, то проект может использоваться десятилетиями.

VHDLэто универсальное средство описания вычислительных устройств на уровнях:

алгоритмическом;

структурном;

регистровых передач;

потоков данных (Dataflow);

логическом;

аналоговых схем.

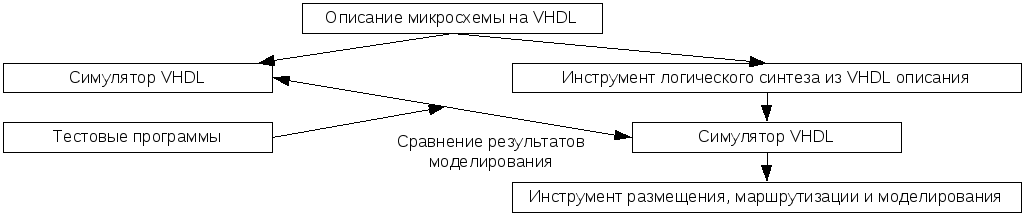

Ход проектирования устройства с использование VHDL

разрабатывается / описывается вычислительное устройство в виде поведенческой модели, на которой отрабатывается задуманный алгоритм функционирования с его проверкой;

поведенческая модель вручную перерабатывается в синтезируемую модель вычислительного устройства, описываемую на уровне регистровых передач.

Такая модель после трансляции компилятором-синтезатором дает проектную документацию в виде файлов описания схемы вычислительного устройства на уровне вентилей (EDIFфайл –electronicdistributioninternationalformat). При этом автоматически выполняется логическая оптимизация вычислительного устройства. Одновременно этот файл автоматически преобразуется вVHDLмодель вычислительного устройства на уровне вентилей;

проект вычислительного устройства в виде EDIFфайла поступает на вход любой современной САПР для изготовления интегральных схем.

Эти САПР выполняют замену вентилей на библиотечные элементы, их размещение на плоскости кристалла, трассировку межсоединений, проектирование масок, проверку соответствия проектным нормам и т.д. В результате получаются файлы с проектной документацией для изготовления кристалла с его печатной моделью, учитывающей задержки, как в вентилях, так и в межсоединениях.

Эта модель тоже описана на VHDL.

Стоимость ошибок при проектировании СБИС очень высока, особенно на ранних этапах, поэтому все этапы проектирования (алгоритмический, структурный, логический и технологический) сопровождаются моделированием вычислительного устройства с помощью испытательного стенда. Этот стенд представляет собой VHDLмодель, составными частями которой будут модели тестируемого внешнего устройства, модель генератора текстовых сигналов и логического анализатора.

На всех этапах может использоваться один и тот же стенд и файл.

В микроэлектронной индустрии наибольшее развитие получил язык Verilog. VHDL более универсальный и гибкий язык, но он проигрывал в быстродействии языку Verilog, особенно при моделировании на уровне вентилей и транзисторов. VHDL получил более широкое распространение в университетах и исследовательских центрах, т.к. он более строгий, стройный, универсальный и расширяемый язык. В VHDL есть пакеты для аналогового моделирования и моделирования многозначной логики. VHDL дешевле, чем Verilog. Все современные САПР имеют компиляторы как с Verilog, так и с VHDL.

VHDL - стандартный и общепринятый язык для все современных производителей БИС. Разработаны компиляторы, транслирующие VHDL-программы в эквивалентные им Verilog-программы.

Все современные САПР обеспечивают размещение и трассировку на основе VHDL-описания. Можно легко производить стыковку VHDL-приложения для различных блоков, разработанных разными фирмами и разработчиками, в различных сочетаниях.

VHDL-стандарт будущего.

Лекция № 18 Технология разработки систем на кристалле

Число транзисторов на кристалле СБИС с каждым днем увеличивается на 60%. На сегодня увеличение степени интеграции в большей степени исчерпана. С определенного момента времени то оборудование, которое размещалось на одной печатной плате, стало возможно разместить на одном кристалле. Причем, это становится выгодным благодаря уменьшению общей стоимости числа необходимым микросхем, энергопотребления и повышения надежности.

Сегодня на одном кристалле размещается не только конкретное функциональное устройство (например, центральный процессор) но и другие, такие как АЦП, ОЗУ, ПЗУ,, блок цифровой обработки сигналов, интерфейсные узлы и т.д., дополняющие его до завершенного устройства. Сегодня эти устройства называют Systemonthechip(SOC) или система на кристалле (СНК).

СНК – это, как правило, заказная СБИС. Чтобы разработка СНК себя окупала, необходимо реализовать десятки и сотни тысяч СБИС. Проект вычислительной системы на ПЛИС (программируемая логическая интегральная схема), может быть выгодным при партии от 10 до 100 экземпляров. Такая разработка в 2 раза и более быстрее чем разработка СБИС по времени, поэтому это основная элементная база СНК.

Наиболее трудоемкими этапами проектирования СНК выступают этапы структурированного проектирования и верификации, в соответствие вычислительной системы заданному алгоритму функционирования. Поэтому эффективность САПР микросхем и производительность разработчиков, выполняющих проектирование на уровне регистровых передач, растет примерно на 20% в год. Начиная с середины 90-х годов, производительность разработчиков стала отставать от роста сложности СНК.

Первым решением этой проблемы было предложено использование библиотечных вычислительных модулей (Intellectualpropertycores). Эти модули являются типовыми и могут настраиваться на решение конкретных задач.

Второй подход к решению задачи – это разработка САПР совместного проектирования аппаратно-программного обеспечения. Такие системы получили название HardwareSoftwareCodesign. Архитектура СНК включает в себя микропроцессорное ядро с периферийными устройствами в различном сочетании. Обычно, процедура разработки вычислительного устройства с такой архитектурой состояло из 3-х последовательных этапов:

разработка математического обеспечения микропроцессора;

проектирование электрической схемы;

стыковка математического обеспечения с аппаратной частью.

Для ускорения выполнения проектирования разрабатывают САПР, который не только совместно выполняет эти этапы, но и производит моделирование работы СНК и её верификацию в комплексе. Такая САПР может включать в себя трансляцию с языка высокого уровня с автоматическим разделением вычислительных задач между микропроцессорным ядром, спецпроцессорами и другими периферийными устройствами.

Вычислительные заготовки

В крупных фирмах, которые долго занимаются разработкой СБИС, а теперь перешли на выпуск СНК, разработали большие библиотеки стандартных модулей ОЗУ, АЛУ, периферийных устройств.

При разработке СНК, как правило, часть блоков разрабатываются заново, а часть берется из библиотеки. Условием записи модуля / блока в библиотеку является:

ясное описание блока;

хороший интерфейс;

документация на него;

комментарий;

испытательный стенд с надежными тестами.

Продажа обычно подлежит лицензии на разработку данного блока или всей СНК. Вычислительные заготовки различаются по гибкости своей настройки под условия потребителя:

гибкие – описанные языком описания аппаратуры VHDLна уровне регистровых передач;

жесткие – логическая схема и EDIFфайл;

твердый – маски под определенную технологию и прошивки ПЛИС.

Гибкие заготовки, как правило, настраиваются в широком диапазоне и не зависят от технологий. Выигрыш от их применения, это не только уменьшение стоимости СНК, но и уменьшение его энергопотребления. Чтобы проект был принят как гибкая заготовка, он должен иметь:

исчерпывающую ясную документацию;

текст описания на VHDLилиVerilogв хорошем стиле, для синтеза заготовка должна быть настраиваемой на технические условия потребителя;

хорошие средства верификации в виде стендов, исчерпывающих тестов и иногда опытных макетов;

четкая методика того, как вычислительное устройство вставлять в СНК, включающую надежные скрипты (это программа на макроязыке САПР, автоматизирующее тестирование и создание жесткой и твердой заготовки).

На сегодня наиболее рациональным способом считается (переход от идеи к железу) сборка СНК из имеющихся вычислительных заготовок. Есть платные и бесплатные библиотеки заготовок. Бесплатный банк заготовок создан по инициативе организаций, содействующих развитию технологий СНК, а также инженеров, желающих поделиться результатами.

Лекция № 19 Программистская модель вычислителя VHDL

Составление программы VHDLозначает программирование модели вычислителя, выполняющего эту программу. Алгоритм, описанный наVHDL, представляет собой некоторое множество вычислительных процессов, организованных на определенные модели вычислителя. Кроме того, в симуляторах используются модели вычислителя с точки зрения эмуляторов. При синтезе логических схем рассматривается аппаратная модель реализацииVHDL, тоесть модель, реализуемая в СБИС или ПЛИС.

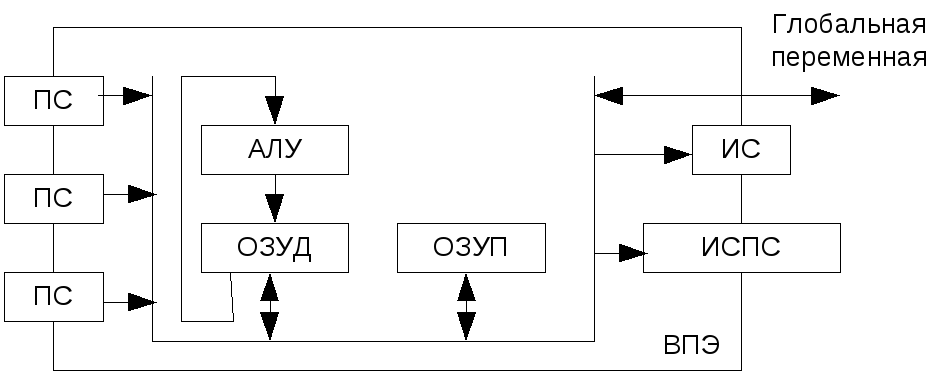

Наиболее полно программистская модель вычислителя VHDLописана в руководстве к стандарту языка. В нем, параллельно с описание синтаксиса и семантики всех языковых конструкций, проводится объяснение их реализации в модели вычислителя. В отличие от большинства современных языков программирования, языкVHDLоснован на параллельной многопроцессорной модели. Нижний уровень модели образует архитектура виртуального процессорного элемента (ВПЭ), а верхний уровень – множество ВПЭ, объединенных некоторой запрограммированной системой межпроцессорных связей. Структура ВПЭ состоит из АЛУ, ОЗУ данных, ОЗУ программы и определенного числа источников (ИС) и приемников сигналов (ПС).

АЛУ выполняет такой же набор процедур, какой требуется для реализации большинства языков программирования. Кроме того АЛУ выполняет многие другие процедуры специфические для VHDL. Это процедуры над данными с производственной заданной разрядностью и с многозначным логическим представленным разрядом. При этом постоянно проверяется корректность результатов процедуры и фиксирования ошибки: выход за заданный диапазон представления числа, несовпадение типов операндов и результатов.

В ОЗУД находятся переменные, участвующие в вычислениях. Переменные имеют статические адреса, но при необходимости можно реализовать динамический доступ к переменным. Источники и приемники служат для общения с внешним миром. При поступлении сигнала на вход приемника, он фиксирует это событие. В приемнике находится как текущее, так и предыдущее состояние сигнала. При выполнении действия с идентификатором сигнала как с операндом выполняется чтение приемника сигнала. После выполнения операнда присваивания источник генерирует сигнал.

В ОЗУП находятся программы в виде цепочки операторов, включая условные операторы, выполняющиеся последовательно друг за другом. Но на операторах WAITвыполнение программы останавливается. Операндами оператораWAITявляется выбор всех сигналов, так называемый список чувствительности или заданный промежуток времени задержки или некое выполнение логического условия. ОператорWAITожидает появления внешнего события (приход сигнала), удовлетворяющего некоторым условиям или ждет истечения периода задержки. Далее программа выполняется опять.

При выполнении оператора WAITв источниках сигнала генерируются сигналы, каким было присвоено некоторое значение. При достижении последнего операнда программа переходит на первый.

Отдельным входом / выходом является шина передачи глобальных переменных. Глобальная переменная может приниматься, тоесть участвовать как операнд или передавая из ПЭ как результат процедуры присваивания в производственные моменты времени. В VHDLне предусмотрены механизмы синхронизации передачи глобальных переменных, поэтому их применение очень ограничено.

К ВПЭ можно подключить дисковую память. При этом операторы открытия, чтения, записи. Закрытия файлов используются аналогично другим языкам.

Верхний уровень программной модели составляет множество ВПЭ, объединенных линиями связи для передачи сигналов между ними. Общим для всех виртуальных процессов является консоль для связи с операторами программ, дисковая память и ОЗУ глобальных переменных.

Число ВПЭ равно числу процессов в программе VHDLпосле её компиляции, а линий межпроцессорных связей столько, сколько необходимо для выполнения программы.

Как и в других языках VHDLсигнал используется одним вычислительным процессом для сообщения другим вычислительным процессам факта использования некоторого события.

Кроме того, сигнал используется для передачи исходных и промежуточных данных между процессами. При использовании VHDLпрограммы, выбранные сигналы можно записать в своем развитии и затем воспроизвести в виде временных графов и таблиц.

При запуске программы на исполнение все переменные принимают заданное начальное значение. Затем во всех ВПЭ начинают свое использование вычислительные процессы. При достижении операторов WAITпроцессорные элементы генерируют вычислительные сигналы и останавливаются. Эти сигналы, пройдя через соответствующие им линии связи к другим ВПЭ, запоминают в них продолжение вычислительных процессов. Такое функционирование вычислительной системы может продолжаться неопределенно долго, пока ни будет восстановление консоли. В большинстве программVHDLодни из процессов является ведущим и задает поток возбужденных состояний сигналов для других процессов. Например, этот процесс может быть моделью синхрогенератора, тогда ВПЭ генерирует возбужденного сигнала, возбуждающего смежные с ним процессы. Поэтому модель вычислителя реализацииVHDLможно трактовать как некий волновой процесс со специализированной структурой.

Если в процессе не используется оператор WAITс установленной задержкой, то цикл запуска / остановки этого процесса выполняется практически мгновенно (с некой Δ задержкой). Δ – малый промежуток времени одинаковый для всех процессов.

Основным назначением консоли является вывод сообщения на экран, которое генерируется специальными операторами assertиreport. ВПЭ могут иметь производственный доступ записи / чтения к памяти глобальных переменных. Эти переменные служат дополнительным средством связи между ВПЭ, так как внутренние переменные ВПЭ не доступны для других элементов вычислительной системы. ВПЭ функционируют асинхронно относительно друг друга. Значит, невозможно задать однозначный порядок доступа глобальной переменной от нескольких ВПЭ без задания механизма синхронизации. Поэтому корректное использование глобальных переменных возможно, если они используются как константа, или запись в них выполняется только одним ВПЭ. Причем, момент записи безразличен относительно вычислительных процессов в других ВПЭ.

При программировании на VHDLнеобходимо учитывать следующее:

все процессы выполняются параллельно;

одновременно исполняемые процессы образуют фронт волны запусков, этот фронт передвигается с временным шагом, равным Δ задержки;

все параллельные операторы языка VHDLпреобразуются в функционально эквивалентные операторы процессов, поэтому данная вычислительная модель годится для любойVHDLпрограммы;

структура вычислительной модели остается неизменной после компиляции программы. Эта структура не зависит от сигналов и переменных изменяемых в процессе дополнения программы. Она не может перестраиваться динамически;

область действия всех переменных, кроме глобальных, ограничена операторами процессов. Вне процессов переменные не доступны. Порядок доступа к глобальным переменным непредсказуем. Их лучше не использовать.

Лекция № 20 Разработка микросхем на языке VHDL

Разработка VHDLописания микросхем: данный этап соответствует разработке описания устройства с точки зрения алгоритмов его функционирования на языкеVHDL. Как правило, используется концепция модулей, тоесть микросхема делится на несколько логических структур.

В сложных схемах их число может быть очень большим. В описании модуля указываются характеристики входных / выходных данных и алгоритмы взаимосвязи. Понятие модуль взято из языка Verilog, которое допускает описание модуля, а языкVHDLдопускает несколько описаний. Структура модулей иерархическая. Каждый модуль включает в себя экземпляры других модулей, выполняющих более простые процедуры. Сама микросхема также является модулем со своими входами и выходами. Например, надо разработать сумматор. Сначала разработчик описывает одноразрядный двоичный сумматор с тремя входами (2 слагаемых и перенос) и двумя выходами (результат и перенос). Для описания многоразрядного сумматора описывается модуль, который включает необходимое число модулей, описывающих многоразрядный сумматор.

Результатом синтеза является логическая схема устройства (уровень логических элементов NetList), при создании которого, созданное описание модулей заменяется логическими элементами из библиотеки элементов, и вNetListописываются связи между этими элементами. Состав модулей в библиотеке зависит от используемого базиса. Полузаказные микросхемы (FPGA) с точки зрения инженера состоят из блоков гораздо более крупных, чем логический вентиль. Синтез происходит уже в этих блоках, а не в вентилях.

HDLязыки имеют достаточно развитые средства описания задержек работы библиотечных модулей (логический элемент или блок) и другие временные характеристики для конкретных типов микросхем.

Далее происходит моделирование микросхемы по исходному описанию и по результатам синтеза. Так как исходное описание не учитывает конкретных временных характеристик элементов / блоков, а инженер часто описывает асинхронные процессы (триггеры, срабатывающие по уровню, а не по фронту синхросигнала; синхронизаторы в одном модуле, срабатывающие по разным фронтам синхросигналам), то возникает несоответствие результатов естественного и синтезируемого описания микросхемы.

Инженер устраняет причины такого несоответствия, корректируя исходное описание, проводит синтез и опять сверяет результаты. В зависимости от сложности разрабатываемого устройства число итераций может быть очень большим.

После совпадения результатов моделирование передается инструментам синтеза более низкого уровня. Так как NetListописан уже в терминах устройств, которые уже можно реализовать в виде аппаратуры (в виде кристалла), то дальнейшая разработка идет в сторону размещения этих устройств на кристалле с учетом требования маршрутизации соединений. На основе этих результатов получают "маски" для изготовления микросхем. Если схема содержит в себе цифровые и аналоговые элементы, то по этим маскам ещё раз проводится моделирование, но уже для аналоговой части. Если есть помехи, то они устраняются путем размещения элементов и маршрутизации.

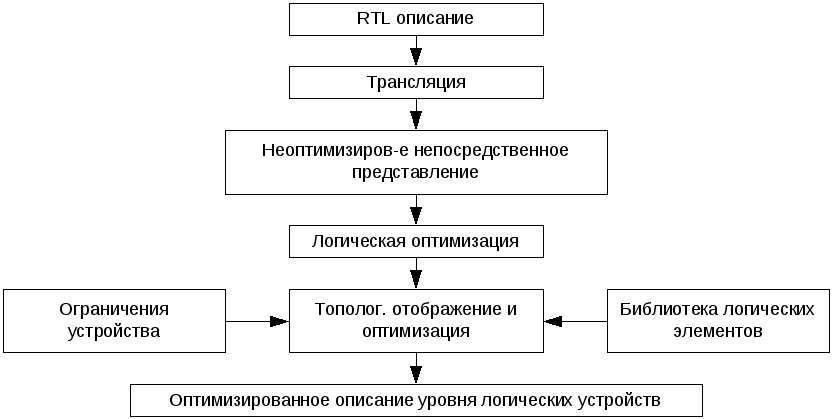

Уровни кодирования на VHDL

уровень транзисторов (switchlevel).HDLязыки позволяют описывать устройства в понятиях отдельного МДП (MOS) транзистора и шин земля и питание. Потребность в таком описании возникает редко из-за большого уровня интеграции транзисторов в современных микросхемах. Применять этот уровень необходимо с большим вниманием, учитывая, что для разных базисов и для полузаказных интегральных схем результат может очень сильно отличаться от задуманного.

уровень логических элементов (GateLevel). Наиболее часто применяемый. Описание микросхемы производится в понятиях инверсное "и", инверсное "или" и так далее. Далее синтезирующая программа приводит всю логику к базису, описываемому в библиотеке элементов. Данный уровень применяется для разработки небольших устройств.

уровень передачи данных (Data flow level = Register transfer level). Так как число логических элементов может быть очень большим, то описание устройства происходит в понятиях передачи данных между регистрами. Далее программа логического синтеза переводит это описание на уровень логических элементов.

Последовательность перевода

Трансляция RTLописания микросхемы – это переводRTLописания во внутреннее представление. При этом ограничения, такие как площадь, временные характеристики и энергопотребление не учитываются.

Неоптимизированное описание 0 это описание, соответствующее внутренним структурам данных, инструментов логического синтеза.

Логическая оптимизация – это упрощение логических выражения с использованием различных методов оптимизации.

До этапа топологического отображения описание устройства не завесило от метода его изготовления. На данном этапе программа синтеза переводит разработанное описание на язык конкретных элементов с учетом особенностей их производства. Логические элементы (ячейка) могут быть как обычными элементами цифровой логики, так и макро ячейками (мультиплексор, триггер, сумматор и т.д.)

Из этих блоков строится микросхема.

Каждая логическая ячейка сначала получает свою физическую интерпретацию, вычисляются временные характеристики в формате, понимаемом инструментом синтеза.

Описание ячейки включает:

функциональность ячейки;

занимаемая ею площадь;

временные характеристики и характеристики энергопотребления.

Такие описания находятся в библиотеке элементов.

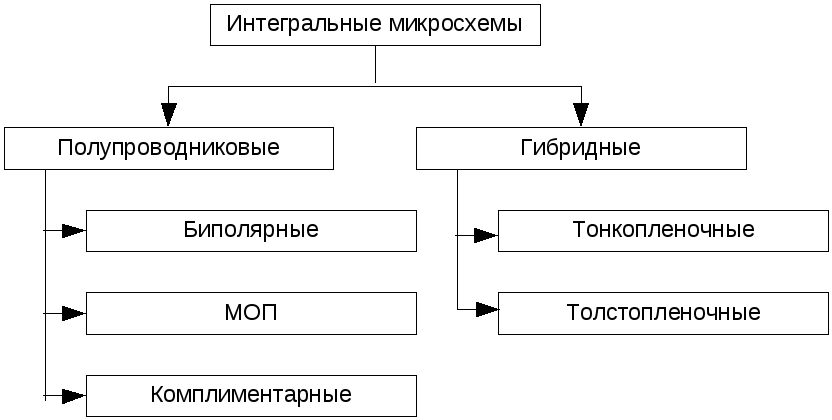

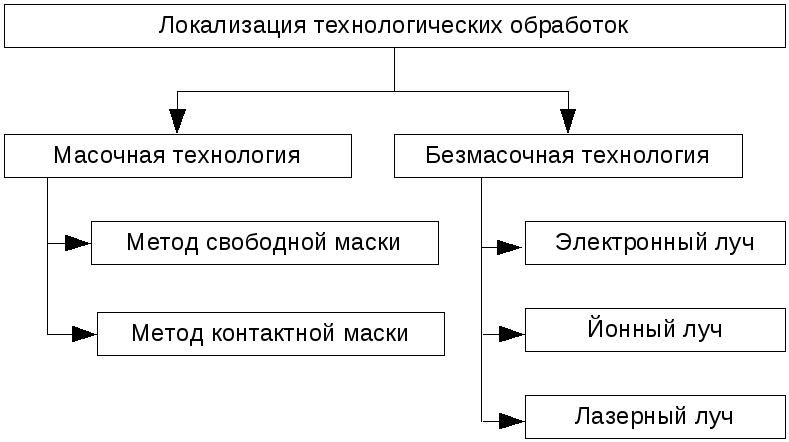

Лекция № 21 Классификация и основные этапы изготовления микросхем

По конструктивно технологическому исполнению структур интегральные микросхемы подразделяются на 2 основные разновидности: полупроводниковые и гибридные. Полупроводниковой называют микросхему, все элементы и межэлементные соединения которой выполнены в объеме и на поверхности полупроводниковой пластины, формируется она на основе биполярных или МОП - транзисторов. Пленочной называют микросхему, все элементы и межэлементные соединения и контактные площадки которой выполнены на диэлектрической подложке в виде пленок. По этой технологии могут изготавливаться многокристальные интегральные схемы. Гибридной называют микросхему, содержащую помимо элементов, представляющих собой нераздельные от диэлектрической подложки конструктивное целое, компоненты и / или кристаллы.