Режими роботи таймерів-лічильників

Рисунок 1 - Режими роботи таймерів-лічильників

Режим 0 Переведення будь-якого Т/С в режим 0 робить його схожим на таймер КМ1816ВЕ48 (восьмибітний лічильник), до входу якого під’єднаний п'ятибітний дільник частоти. Роботу Т/С в режимі 0 на прикладі T/C1 ілюструє рис.17а. У цьому режимі таймера регістр має розрядність 13 біт. При переході зі стану "всі одиниці" у стан "всі нулі" встановлюється прапорець переривання від таймера TF1. Вхідний дозволений синхросигнал таймера 1 (надходить на вхід Т/С1), коли керуючий біт TR1 установлений в 1 або керуючий біт GATE (блокування) дорівнює 0, або на зовнішній вивід запиту переривання INT1 надходить рівень 1. Установка біта GATE в 1 дозволяє використовувати таймер для вимірювання тривалості імпульсного сигналу.

Режим 1 Робота будь-якого Т/С у цьому режимі така сама, як і в режимі 0, за винятком того, що регістр таймера має розрядність 16 біт.

Режим 2 У цьому режимі робота організована таким чином, що переповнення (перехід зі стану "всі одиниці" у стан, "всі нулі") восьмибітного лічильника TL1 призводить не тільки до установки прапорця TF1 (див. рис.17б), але й автоматично перезавантажує в TL1 вміст старшого байта (TH1) таймерного регістра, яке попередньо було задано програмним шляхом. Перевантаження залишає вміст TH1 незмінним. У режимі 2 Т/С0 і Т/С1 також працюють абсолютно однаково.

Режим 3 У режимі 3 Т/С0 і Т/С1 працюють по-різному. Т/С1 зберігає незмінним свій поточний зміст. Роботу Т/С0 ілюструє рис.17в. У режимі 3 TL0 і TH0 функціонують як два незалежних восьмибітних лічильника. Роботу TL0 визначають керуючі біти Т/С0 (С/Т, GATE TR0), вхідний сигнал INT0 і прапорець переповнення TF0. Роботу TH0, який може виконувати тільки функції таймера (підрахунок машинних циклів мікро-ЕОМ), визначає керуючий біт TR1. При цьому TH0 використовує прапорець переповнення TF1. Режим 3 використовується в тих випадках, коли потрібна наявність додаткового восьмибітного таймера або лічильника подій. Можна вважати, що в цьому режимі мікроЕОМ 8051 має у своєму складі три таймера/лічильника. У разі ж, якщо Т/С0 використовується в режимі 3, Т/С1 може бути або вимкнений, або переведено в режим 0, 1 або 2, або може бути використаний послідовним портом як генератор частоти передавання.

14. Spi-інтерфейс мікроконторлера

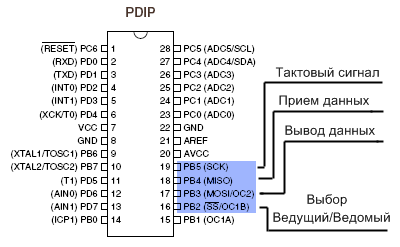

Інтерфейс SPI (SerialPeripheralBus) - інтерфейс для обміну даними між мікросхемами. Придуманий компанією Motorola, але в даний час використовується в продукції багатьох виробників. Шина SPI організована як "ведучий-підлеглий". В якості ведучого найчастіше виступає мікроконтролер. Зовнішні пристрої підключені до ведучого є підлеглими (веденими). Якщо з'єднати два мікроконтролера по шині SPI, то вони можуть по черзі стає ведучим чи веденим. Головне, що в конкретний момент часу на шині SPI тільки один пристрій може бути провідним. Розглянемо на прикладі mega8 які ніжки в МК пов'язані з шиною SPI і що вони означають

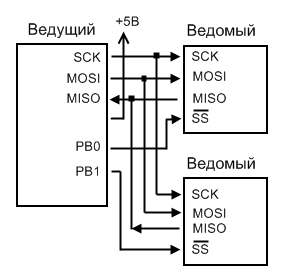

Підключення пристроїв до ведучого зрозуміло з малюнка нижче

При завантаженні значення в регістр даних SPI ведучого він відразу ж починає генерувати тактовий сигнал на SCK і побітно висувати дані на виведення MOSI, який з'єднаний з входами MOSI ведених пристроїв. Ведене пристрій отримає дані, тільки якщо на виведенні SS присутній низький рівень. Т.ч. ми можемо підключити до шини SPI мікроконтролера кілька SPI пристроїв і використовуючи додаткові ніжки МК вибирати конкретний пристрій з яким ми хочемо в даний момент працювати. Висновок SS ведучого можна конфігурувати як вихід і використовувати його як вихідний контакт. Якщо ж він налаштований як вхід, його необхідно підключити до шини живлення. Якщо на виводі SS ведучого пристрою з'явиться низький рівень, то він переходить у режим веденого.

Взагалі, зручний цей інтерфейс тим, що з ним дуже просто працювати. Давайте розглянемо регістри МК, пов'язані з шиною SPI

SPDR - регістр даних, містить посилається або приймається байт.

SPCR

Біт 7 - SPIE: дозвіл переривань. Переривання генерітся, якщо цей біт встановлений і встановлено біт глобального дозволу переривань регістра SREG (6-й біт).

Біт 6 - SPE: включення SPI. Перед будь-якими діями з SPI цей біт повинен бути встановлений в "1".

Біт 5 - DORD: порядок передачі даних. Якщо цей біт встановлений в "1" то молодший біт даних передається першим. Якщо цей біт скинутий в "0" - старший біт даних передається першим.

Біт 4 - MSTR: вибір режиму роботи. Якщо встановлений в "1", то обраний режим ведучого, якщо в "0" - режим веденого. Якщо SS налаштований як вхід і на нього подано низький рівень, у той час як біт MSTR встановлений в "1", тоді цей біт скинеться в "0" і біт SPIF регістра SPSR (див. нижче) встановиться в "1".

Біт 3 - CPOL: полярність тактового сигналу. "0" - під час очікування на SCK присутній низький рівень. "1" - під час очікування на SCK присутній високий рівень.

Біт 2 - CPHA: фаза тактового сигналу. Якщо цей біт встановлений в "1", то дані зчитуються по спадающему фронту SCK, якщо в "0" - по наростаючому фронту SCK.

Таким чином установкою цих біт ми можемо вибирати один з чотирьох режимів роботи шини SPI.

При з'єднанні МК з яким-небудь пристроєм, дивіться уважно в документації на пристрій режими які воно підтримує. Провідне і підлегле пристрої працюють в різних режимах не сумісні.

Біти 1:0 - SPR1: SPR0: швидкість передачі (частота тактування). Тільки для пристроїв в режимі ведучого. Якщо МК налаштований на роботу в якості веденого, установка цих біт не матиме жодного ефекту. У таблиці нижче можна подивитися які значення потрібно записати в ці біти, щоб встановити потрібну швидкість передачі (Біт SPI2X в регістрі SPSR)

SPSR

Біт 7 - SPIF: прапор переривання. Встановлюється по завершенні передачі. Переривання генерітся якщо встановлено біт SPIE регістра SPCR і біт I регістру SREG.

Біт 6 - WCOL: прапор колізій запису. Встановлюється в "1" при спробі запису в регістр SPDR до закінчення передачі.

Біт 0 - SPI2X: біт подвійної швидкості SPI. Якщо SPI сконфігурований як ведучий, тоді ми можемо працювати з подвійною частотою. Але якщо SPI сконфігурований як ведений, то ми не можемо розраховувати на подвійну швидкість роботи SPI.

Тепер розглянемо приклад ініціалізації МК, як майстра і функцію передачі байта.

# Define DDR_SPI DDRB

# Define DD_MOSI 3

# Define DD_MISO 4

# Define DD_SCK 5

# Define SPE 6

# Define MSTR 4

# Define SPR0 0

# Define SPIF 7

voidSPI_MasterInit ()

{

DDR_SPI = (1 << DD_MOSI) | (1 << DD_SCK) ;/ / налаштовуємо на вихід

SPCR = (1 << SPE) | (1 << MSTR) | (1 << SPR0) ;/ / вкл SPI, ведучий, частота fck/16

}

/ / Функція передачі байта

voidSPI_MasterTransmit (charcData)

{

SPDR = cData ;/ / починаємо передачу

while (! (SPSR & (1 << SPIF))) ;/ / чекаємо поки передача завершиться

}

Ну і щоб, не лазити зайвий раз у даташит :) функції ініціалізації МК веденим і функція прийому байта.

voidSPI_SlaveInit ()

{

DDR_SPI = (1 << DD_MISO) ;/ / налаштовуємо на вихід MISO, решта на вхід

SPCR = (1 << SPE) ;/ / включаємо SPI

}

/ / Функція прийому байта

charSPI_SlaveReceive ()

{

while (! (SPSR & (1 << SPIF))) ;/ / чекаємо якщо зайнятий

return SPDR ;/ / повертаємо байт даних

}

Вектор переривання в WinAVR записується так - SPI_STC_vect. Якщо хочемо використовувати переривання, тоді повинні встановити відповідні біти в регістрах і викликати оброблювач переривання

ISR (SPI_STC_vect)

Інтерфейс SPI може бути реалізований програмно на будь-яких ніжках МК, але краще користуватися вбудованим в МК.