- •Курсовая работа по курсу

- •Разработка и описание структурной схемы эвм.

- •Центральный процессор

- •Система прерываний

- •Описание блока синхронизации и таймера

- •Клавиатура

- •Монитор

- •Прямой доступ к памяти (пдп)

- •Основная память

- •Контроль памяти по Хэммингу

- •Разработка функциональной схемы кэШа команд и данных

- •Литература

МИНИСТЕРСТВО ОБРАЗОВАНИЯ И НАУКИ РФ

НОВОСИБИРСКИЙ ГОСУДАРСТВЕННЫЙ ТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ

Кафедра ВТ

Курсовая работа по курсу

«Организация ЭВМ»

Группа: АМ-110

Студент: Полуцыганова Т.А.

Преподаватель: Гребенников В.Ф.

Дата:

г. Новосибирск

2004 г.

Содержание:

1.Цель курсового проекта 2

2.Задание на курсовой проект. 2

3.Разработка и описание структурной схемы ЭВМ. 4

3.1. Центральный процессор 5

3.2.Система прерываний 6

3.3.Описание блока синхронизации и таймера 8

3.4.Клавиатура 10

3.5.Монитор 11

3.6.Прямой доступ к памяти (ПДП) 12

3.7.Основная память 14

3.8.Контроль памяти по Хэммингу 16

4.Разработка функциональной схемы КЭШа команд и данных 18

Литература 23

Цель курсового проекта

Целью курсового проектирования является углубление и закрепление теоретических знаний студентов, приобретение навыков разработки узлов ЭВМ на структурном, функциональном и алгоритмическом уровнях.

Задание на курсовой проект.

Курсовой проект посвящен разработке структурной схемы гипотетической ЭВМ, функциональной схемы и алгоритма работы конкретного блока, входящего в состав этой ЭВМ.

В состав ЭВМ входят следующие блоки:

- центральное обрабатывающее устройство (ЦОУ);

- микропрограммное устройство управления (УУ);

- оперативная память (ОП);

- блок синхронизации (БС);

- система прерывания программ (СПП);

- таймер;

- система ввода-вывода (СВВ);

- монитор и клавиатура;

- НГМД;

- «Винчестер».

Основные параметры ЭВМ:

- адресность ЭВМ - двухадресная;

- длина команды – переменная;

- разрядность - не менее 16;

- емкость ОП - не менее 1 Мбайт.

Индивидуальные исходные данные на выполнение курсового проекта:

Структура - трехшинная, организация ОП - многоблочная, наличие КЭШа команд и данных, прерывания радиальные на макроуровне, организация В/В – ПДП, контроль памяти по Хэммингу. Разрабатываемый блок до уровня функциональной схемы – блок КЭШ.

Разработка и описание структурной схемы эвм.

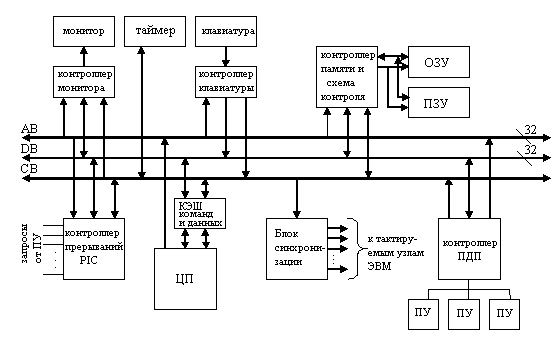

В соответствии с заданием организация ЭВМ трехшинная:

DB(шина данных) – обеспечивает обмен данными между всеми основными блоками ЭВМ, 32 разряда;

АВ (шина адреса) – используется для задания адреса памяти. Им может быть как адрес в ОЗУ, ПЗУ, так и адрес видеопамяти контроллера монитора – 32 разряда;

СВ (шина управления) – по ней осуществляется передача сигналов управления между блоками ЭВМ.

Такая структура обеспечивает 3 вида передачи данных:

процессор ↔память;

процессор ↔ интерфейс;

память ↔ интерфейс.

В первых двух случаях передачей данных управляет процессор. Память и интерфейс по управляющему сигналу от процессора осуществляют передачу данных.

Кэш команд

и данных

Рис. 1. Структурная схема ЭВМ

Центральный процессор

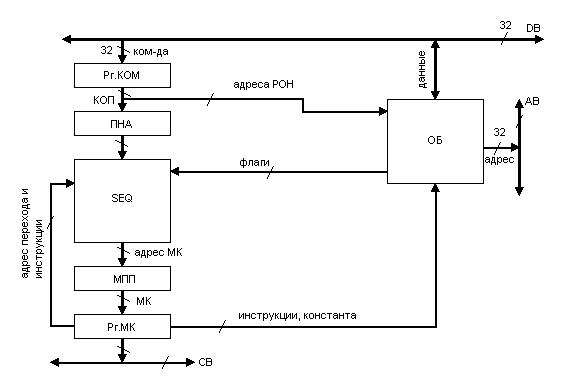

Процессор является основным блоком ЭВМ и содержит следующие части:

МУУ (микропрограммное устройство управления);

ОБ (операционный блок).

ОБ выполняет арифметические, логические и сдвиговые операции с данными заданной разрядности (до 32 разрядов). Имеет в своем составе АЛУ (арифметико-логическое устройство), файл регистров общего назначения, блок логики сдвигов, статусный регистр для хранения слова состояния процессора. Для взаимодействия с шинами ABиDBиспользуются буферные регистры (регистр входных данных, регистр выходных данных, адресный регистр).

МУУ управляет работой ОБ и всей ЭВМ в целом. За основу МУУ взят конвейер первого порядка с регистром микрокоманд (Рг.МК). Из регистра команд код операции (КОП) поступает на ПНА (преобразователь начального адреса). Полученный адрес поступает на SEQ (секвенсор). SEQ адресует МПП (микропрограммную память). Полученная микрокоманда (МК) записывается в Рг.МК. В момент, когда МК начинает выполняться, SEQ формирует адрес следующей МК. Для выбора адреса следующей микрокоманды используются источники:

ПНА;

регистр микрокоманд;

зависит от флагов;

стек.

Рис.2. Структурная схема процессора