- •Міністерство освіти і науки України

- •Практична робота №1 Вивчення будови пеом

- •Теоретичні питання

- •Практична робота №2 Вивчення будови процесора і організації пам’яті

- •Теоретичні питання

- •Практична робота №3 Дослідження логічних елементів

- •Теоретичні питання

- •Практична робота №4 Основи роботи з matlab

- •Теоретичні питання

- •Завдання до практичної роботи:

- •Практична робота №5 Написання програм з використанням умовних операторів

- •Теоретичні питання

- •Практична робота №6 Написання програм з використанням циклічних операторів

- •Теоретичні питання

- •Практична робота №7 Побудова графіків функцій

- •Теоретичні питання

- •Завдання до практичної роботи:

- •Практична робота №8 Рішення алгебраїчних і трансцендентних рівнянь в середовищі matlab

- •Теоретичні питання

- •Варіанти алгебраїчних та трансцендентних рівнянь

- •Практична робота №9 Рішення систем рівнянь в середовищі matlab

- •Теоретичні питання

- •Варіанти систем алгебраїчних рівнянь

- •Практична робота №10 Загальні відомості про програмний комплекс simulink. Побудова простих моделей

- •Теоретичні питання

- •Варіанти завдань

- •Порядок роботи над завданнями:

- •Практична робота №11 Моделі алгебраїчних об'єктів. Форматування об’єктів моделей

- •Теоретичні питання

- •Варіанти завдань.

- •Практична робота №12 Маскування підсистем в Matlab/Simulink

- •Теоретичні питання

- •Варіанти завдань.

- •Список літератури

- •Для нотаток навчально-методичне видання

- •Тир.__ прим. Зам.______

- •43018, М. Луцьк, вул. Львівська, 75

Практична робота №1 Вивчення будови пеом

Мета: Ознайомлення з будовою ПЕОМ

Теоретичні питання

Основою будь якої комп’ютерної системи є друкована плата з головним процесором, або мікроконтролером і підтримуючими мікросхемами. Друковані плати поділяються на два класи:

одноплатні комп’ютери;

шинно-орієнтовані – це комп’ютери в яких центральна плата реалізує схему мінімальної конфігурації, а інші функції реалізуються за допомогою багато чисельних допоміжних плат. Всі головні компоненти з’єднуються паралельними провідниками, які називаються шинами. Центральна плата до якої приєднуються всі інші називається материнською платою, а приєднувальні плати дочірніми.

Системна плата. Системна плата була розроблена фірмою IBM і прийнята за основний стандарт для розробки дочірніх плат. Основні підтримуючи схеми були розташовані на материнській платі. Ця багатофункціональна реалізація плати відобразилась в її розвитку, як системна плата. В системній платі немає відео адаптера, аналогового-цифрових перетворювачів (АЦП), цифро-аналогових перетворювачів (ЦАП) та інших дочірніх плат.

Мікропроцесор – складний програмнокерований пристрій, призначений для обробки цифрової інформації та керування процесом цієї обробки, виконаний у вигляді однієї чи кількох інтегральних мікросхем підвищеного ступеня інтеграції.

Пам’ять – це елемент необхідний мікропроцесору для здійснення будь-яких операцій, крім того пам’ять визначає як програмується сам процесор і рівень складності розв’язуваних задач. Пам’ять ділиться на два класи : основна і зовнішня. Основна – це пам’ять до якої комп’ютер або мікропроцесор може безпосередньо звернутися таку пам’ять називають ОЗП (оперативна). Доступ до нової пам’яті отримують за допомогою адресної шини, або портів вводу-виводу. Так-як будь-яку частину цієї пам’яті, будь-який її байт може бути знайдений в будь-який момент часу, то її називають пам’ять з прямим доступом RАM. Пам’ять яка потребує більш значних часових затрат на доступ називається зовнішньою – ця пам’ять забезпечує більш тривале збереження інформації і являється базисом на якому формується комп’ютерна система. Зовнішня пам’ять в багато разів може перевищувати основну пам’ять, але доступ до зовнішньої пам’яті не може комп’ютерною системою оброблятися одразу.

Кеш-пам’ять – використовується для прискорення доступу до оперативної пам’яті.

BIOS (постійна пам’ять) – базова система вводу – виводу, система зашита в пам’ять комп’ютера і вона визначає його базові характеристики, тобто з якою операційною системою даний комп’ютер буде працювати, які тестові прикладні програми, що комп’ютер може зробити без запуску програм з диска, або носія інформації, як комп’ютер буде реагувати на специфічні команди або ситуації.

Рисунок 1.1 – Структура і принцип функціонування комп’ютерних систем

Основним елементом комп’ютерної системи являється процесор в склад якого входять:

пристрій керування вибору команд з пам’яті і їх виконання;

АЛП (арифметико – логічний пристрій) – який виконує операції над даними;

Регістри – здійснюють тимчасове зберігання даних і стану процесора;

Схема для керування і зв’язки з підсистемами пам’яті і модулями вводу-виводу.

Процесор складається з наступних регістрів і АЛП:

Лічильник команд – він призначений для організації звернення до комірки пам’яті в якій зберігається програма. В кінці кожного циклу виконання команди лічильник вказує адрес комірки пам’яті в якій містить наступну команду програми

Регістр команд – використовується для зберігання команди , яка безпосередньо виконується машиною. Код команди пересилається з регістра команд в пристрій керування комп’ютерної системи і декодується. Після цього відбувається дія по реалізації команди.

Регістр адреса – зберігає значення виконуючого адреса комірки пам’яті комп’ютерної системи, якщо машина здійснює вибір команди, то в регістр адресу пересилається зміст команди лічильника команд для вказування адресу пам’яті де зберігається команда.

Регістр даних – використовується для тимчасового зберігання слів при обміні інформації між пам’яттю і процесором.

Акумулятор – являється одним з основних елементів процесора. Комп’ютерна система може виконувати арифметичну, або логічну операцію тільки над двома операндами одночасно коли один з операндів видаляється з пам’яті в регістр даних, а другий операнд знаходиться в акумуляторі процесора.

Регістр переносу – це однорозрядний регістр , який виступає в якості продовження акумулятора і який заповнюється при його переповненні. Цей регістр використовується також для організації циклічних зсувів.

Структурна схема ЕОМ. ЕОМ призначені для опрацювання інформації і відображення результатів опрацювання.

Рисунок 1.2 – Структурна схема ЕОМ

Під час рішення задачі програма й операнди (числа, над якими провадяться операції) знаходяться в оперативній пам'яті (ОЗП). В процесі рішення задачі АЛП постійно взаємодіє з ОЗП, передаючи в ОЗП проміжні і кінцеві результати й одержуючи з ОЗП операнди дії всіх частин ЕОМ при рішенні задача здійснюється під впливом керуючих сигналів, які виробляються пристроєм керування відповідно до програми, записаної в ОЗП.

ПЗУ призначено для збереження стандартних програм.

Існує ще понад ОЗП (СОЗП), що має малий обсяг і високу швидкодію. СОЗП застосовується для короткочасного збереження операндів і проміжних результатів.

Якість ЕОМ визначається: обсягом ОЗП (тобто кількістю одночасно збережених в ОЗП двійкових слів); швидкодією, обумовленою кількістю операцій в секунду. Після виконання задачі, програма і результати через пристрій виводу записуються в зовнішній ЗП. У якості зовнішніх ЗП використовуються магнітна стрічка, магнітний диск, магнітний барабан. Програма вводиться в ОЗП з зовнішніх ЗП або з клавіатури через пристрій вводу.

Вузли ЕОМ. Вузли ЕОМ класифікуються на:

комбінаційні – це вузли, вихідні сигнали яких визначаються тільки сигналом на вході, що діє в дійсний момент часу (дешифратор). Вихідний сигнал дешифратора залежить тільки від двійкового коду, поданого на вхід у даний момент часу. Комбінаційні вузли називають також автоматами без пам'яті.

послідовні (автомати з пам'яттю) – це вузли, вихідний сигнал яких залежить не тільки від комбінації вхідних сигналів, що діють у дійсний момент часу, але і від попереднього стана вузла (лічильник).

програмовані вузли функціонують у залежності від того, яка програма в них записана. Наприклад, якщо програмується логічна матриця (ПЛМ), що у залежності від пропаленої в ній програми може виконувати функції суматора, дешифратора, ПЗУ.

Суматор.

Рисунок 1.3 – Суматор

Суматор може бути побудований як комбінаційна схема – послідовний суматор і як послідовна схема – суматор, що накопичує. Суматор здійснює додавання цифр розрядів слів і цифр переносу по правилах додавання по модулю 2. Робота суматора строго регламентована відповідно до таблиці:

Таблиця 1.1 – Результати роботи суматора

-

ai

bi

Pi

Si

Pi+1

0

0

0

0

0

0

0

1

1

0

0

1

0

1

0

0

1

1

0

1

1

0

0

1

0

1

0

1

0

1

1

1

0

0

1

1

1

1

1

1

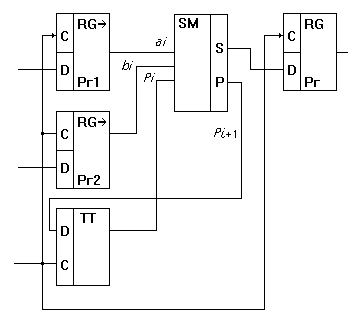

Рисунок 1.4 – Послідовний суматор

Послідовний суматор здійснює додавання операндів і цифр переносу порозрядно, починаючи з молодшого розряду. Основою його схеми є однорозрядний суматор. Додавання проводиться в однорозрядному суматорі SM. Цифри i-того розряду що складається і цифра переносу з молодшого розряду передаються на вхід суматора одночасно з приходом тактового імпульсу. Регістри 1 і 2 використовуються для прийому і збереження цифр i-того розряду операндів. У D - тригері зберігається цифра переносу з молодшого розряду. Регістр 3 приймає і береже цифру i-того суми. З приходом тактового імпульсу з регістрів 1, 2 і D - тригера розряду що складаються і цифра переносу надходить на вхід однорозрядного суматора. Одночасно регістр 3 звільняється для прийому цифри суми.

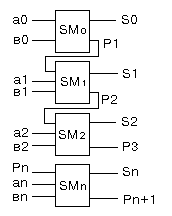

Рисунок 1.5 – Паралельний суматор

В паралельному суматорі всі розряди операндів додаються одночасно, але швидкодія знижується за рахунок часу передачі цифри переносу з молодшого розряду.

Арифметико-логічний пристрій (АЛП). АЛП призначено для виконання арифметичних і логічних операцій над операндами. АЛП класифікуються таким чином:

По засобам дій над операндами. Бувають АЛП послідовної і паралельної дії. У послідовних АЛП дії над операндами провадяться послідовно розряд за розрядом починаючи з молодшого. У паралельних АЛП всі розряди операндів опрацьовуються одночасно.

По виду оброблюваних чисел АЛП можуть робити операції над двійковими числами з фіксованої або плаваючої комою і над двійково-десятковими числами.

Кожна десяткова цифра записується чотирма розрядами двійкового коду.

1971 0001 1001 0111 0001

АЛП при дії над двійково-десятковими числами повинні містити схему десяткової корекції. Схема десяткової корекції перетворить отриманий результат таким чином, щоб кожний двійково-десятковий розряд не містив цифру більше 9.

При записі числа з фіксованою комою кома фіксується після молодшого розряду, якщо число ціле, і перед старшим, якщо число менше 1.

При записі чисел із плаваючою комою виділяється ціла частина, що називається мантисою, і показник ступеня, що характеризує положення коми.

37 і 0.37 - із фіксованої комою

37*10^-2 - із плаваючої комою

3. По організації дій над операндами розрізняють блокові і багатофункціональні АЛП.

У блокових АЛП окремі блоки призначені для дій над двійково-десятковими числами, окремо для дій над числами з фіксованої комою, окремо з плаваючої комою.

У багатофункціональних АЛП ті самі блоки опрацьовують числа з фіксованої комою і двійково-десяткові числа.

Багатофункціональні АЛП.

Рисунок 1.6 – АЛП

Клапани К1 і К2 об'єднують суматори 1, 2 і 3 для дій над числами з фіксованої комою.

Для дій над числами з плаваючої комою клапан К2 об'єднує суматори 2 і 3 для опрацювання мантис, а клапан К1 від’єднує перший суматор від другого. Суматор 1 опрацьовує порядки.

4. За структурою АЛП бувають із безпосередніми зв'язок і багатозв’язковими.

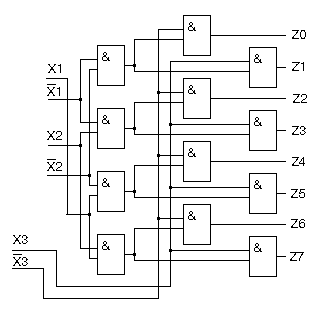

Дешифратор. Дешифратор призначений для перетворення двоичного коду на вході в керуючий сигнал на однім із виходів. Якщо входів n то вихідних шин повинно бути N = 2^n.

|

X1 |

X2 |

X3 |

Z0 |

Z1 |

Z2 |

Z3 |

Z4 |

Z5 |

Z6 |

Z7 |

|

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

|

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

|

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

|

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

Дешифратори можуть бути лінійні, у яких усі перемінні Х1, Х2, Х3 подаються на вхід одночасно.

Рисунок 1.7 – Дешифратор лінійний

Їх швидкодія більше, але більш 3-х перемінних одночасно подати не можна, тому частіше застосовуються багатокаскадні дешифратори. Кількість елементів в кожному такому розряді більше, ніж у попередньому.

На вхід першого каскаду подається одне слово, на вхід такого каскаду друге слово і результати кон’юнкцій, зроблених у першому каскаді.

Найпростіший лінійний дешифратор можна побудувати на діодній матриці:

Рисунок 1.8 – Дешифратор (діодна матриця)

У цій схемі використовується негативна логіка. При подачі "1" на анод діода він закривається. Якщо закриті всі 3 діода, які під’єднанні до однієї горизонтальної лінії, то на цій лінії потенціал - Е, що відповідають рівню "1".

Багатокаскадний дешифратор можна організувати у такий спосіб:

Рисунок 1.9 – Багатокаскадний дешифратор

Два лінійних дешифратора опрацьовують по 2 слова. В останньому каскаді утворяться кон’юнкції вихідного сигналу АЛП першого каскаду. Багатокаскадні дешифратори мають меншу швидкодію.

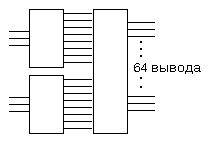

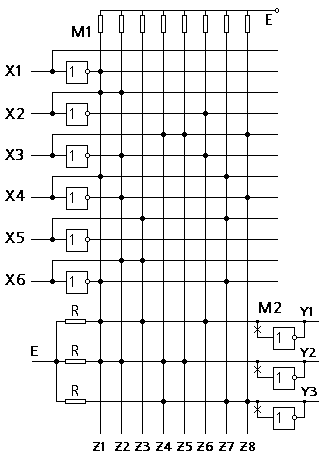

Програмована логічна матриця (ПЛМ).

Рисунок 1.10 – ПЛМ

ПЛМ є вузлом ЕОМ, функціонування якого визначається програмою, записаної в нього. ПЛМ може використовуватися в якості дешифратора ПЗУ.

При записі програми в ПЛМ пропалюються плавкі запобіжники, що з'єднують транзистори МДП із шинами матриці. Матриця М1 називається матрицею кон’юнкції. На горизонтальні шини подаються змінні. На вертикальних шинах утворяться кон’юнкції. На вертикальних шинах з'являється одиничний сигнал тільки тоді, коли всі транзистори, включені у вузли матриці до цієї шини закриті. У вузлах матриці включаються транзистори МДП.

Пропалювання програми відповідно до призначення матриці складається в тому, що пропалюється плавкий запобіжник і транзистор, підєднується до вузла матриці. Якщо на входи транзисторів подати нулі, то вони будуть закриті. Матриця М2 називається матрицею диз'юнкції. На її горизонтальних шинах з'являється сигнал у тому випадку, якщо знімати сигнал через інвертор.

Суматор, який накопичує. Суматор, який накопичує , є автоматом із пам'яттю, тобто слова можуть приходити по черзі в довільні моменти часу і запам'ятовуватися в лініях затримки або в тригерах. Такий суматор застосовується в асинхронних пристроях, які не прив'язані до тактів тактового генератора.

Рисунок 1.11 – Суматор, що накопичує

З приходом що складається аi=1 елемент "АБО" встановлюється в "1", тригер встановлюється в "1". Якщо bi=1 і приходить через який час після ai, то воно запам'ятовується в лінії затримки й одночасно bi перекидає тригер у "0". На інверсному виході тригера встановлюється "1", отже на другу схему "І" подаються дві одиниці, отже на виході другої схеми "АБО" формується цифра переносу в старший розряд, рівна "1". Якщо Pi=0, то цифра суми, що знімається з прямого виходу тригера, дорівнює "0". Якщо Pi=1, то сума Si=1.

-

ai

bi

Pi

Si

Pi+1

0

0

0

0

0

0

0

1

1

0

0

1

0

1

0

0

1

1

0

1

1

0

0

1

0

1

0

1

0

1

1

1

0

0

1

1

1

1

1

1

Інтерфейс. Пристрої обчислювальної системи з'єднуються один з одним за допомогою уніфікованих систем зв'язку, названих інтерфейсом. Інтерфейс являє собою систему шин, що узгоджують пристрої, алгоритми всіх частин, які забезпечують зв'язок в ЕОМ між собою. Від характеристик інтерфейсу залежить швидкодія і надійність ЕОМ. Інтерфейс повинний бути стандартизований із тим, щоб він забезпечував зв'язок процесора й оперативної пам'яті з будь-яким периферійним пристроєм (ПП). Необхідне перетворення формату даних повинно проводитися в ПП. Алгоритми функціонування інтерфейсу і керуючого сигналу АЛП також повинні бути стандартизовані.

Типи інтерфейсу:

1. Інтерфейс ОЗП - через нього провадиться обмін даними між ОЗП і процесором, між ОЗП і каналами вводу - виводу. Головним в обміні даними, тобто починаючу операцію обміну, є процесор і канали вводу - виводу, а виконавцем - ОЗП. Цей інтерфейс є швидкодіючим. Інформація через нього передається словами і напівсловами.

2. Інтерфейс із процесором - через нього відбувається обмін інформацією між процесором і каналами вводу - виводу. Головний - процесор, виконавець - канали. Інтерфейс є швидкодіючим. Обмін інформацією через нього відбувається словами і напівсловами.

3. Інтерфейс вводу-виводу. Через нього відбувається обмін інформацією між каналами вводу - виводу й пристроями керування ПК. Обмін інформацією проводиться байтами. Його швидкодія менше, ніж у перших двох типів.

4. Інтерфейс периферійних апаратів (ПА). Через нього відбувається обмін інформацією між пристроями керування ПК і самими ПК. Він не може бути стандартизований, тому що ПК дуже різноманітні.

По цифровому каналі зв'язку сигнал може передаватися паралельно або послідовно. Паралельна передача цифрового сигналу потребує окремі лінії для кожного розряду, але є більш швидкодіючі. При послідовній передачі цифрові сигнали передаються послідовно по одній лінії зв'язку. По засобам передачі інформації в часі інтерфейс може бути синхронний і асинхронний. Синхронний характерний постійної тимчасовою прив’язкою, а асинхронний - без постійної тимчасової прив'язки. При синхронній передачі даних сигнали, що синхронізують, МП задають тимчасовий інтервал, в момент якого зчитується інформація з одного датчика. Тимчасовий інтервал визначається найбільшим часом затримки в системі передача даних і максимальним часом перетворення аналогового сигналу в цифровий. Асинхронна передача даних характеризується наявністю керуючих сигналів: "Готовність до обміну", вироблюваний датчиком вихідної інформації; "Початок обміну", "Кінець обміну", "Контроль обміну", вироблювані МП. При такій організації обміну автоматично встановлюється раціональне співвідношення між швидкістю передачі даних і розмірами затримки сигналів у каналі зв'язку.

Обмін даними між оперативною пам'яттю і периферійними пристроями (ПП).

Рисунок 1.12 – Схема обміну даними

1. Програмно керований обмін даними. У цьому випадку передача даних від ПП в пам'ять і обернено проводиться через МП відповідно до мікропрограми, записаної в ОЗП, МП керує обміном і операція обміну відбувається так само, як і операція основної програми. При програмному керуванні передачею даних процесор "відривається" від виконання основної програми на весь час операції вводу - виводу, отже знижується продуктивність ЕОМ. Для вводу блока даних необхідно занадто багато операцій, таких як перетворення форматів, адресація в пам'яті, визначення початку і кінця блока даних. В результаті швидкість передачі даних знижується. Дешифратор визначає номер ПП, із яких буде відбуватися обмін даними відповідно до програми. Мультиплексор передає дані від одного з ПП відповідного номера через МП в ОЗП. Після того, як дешифратор визначив номер ПА і МП надіслав запит про обмін даними, МП чекає сигнал готовності від ПП. Демультиплексор передає дані з ОЗП на одне з ПП.

Рисунок 1.13 – Програмно-керований обмін даними

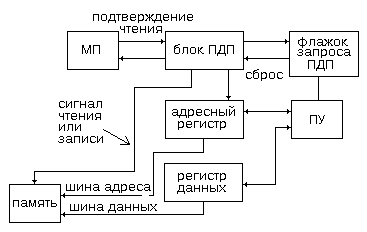

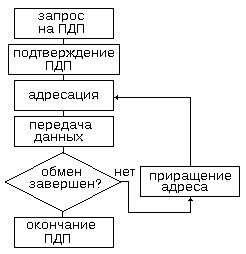

2. Обмін даними з використанням прямого доступу до пам'яті (ПДП). При цьому МП звільняється від участі в обміні даними. ОЗП зв'язується з МП і з апаратурою, що керує обміном даних різними шинами. Обміном даними цілком управляють за допомогою апаратних засобів. Ініціатором обміну даними являється

Рисунок 1.14 – Схема прямого доступу до пам’яті

ПП, що надсилає запит про обмін даними на прапорець запиту ПДП. Прапорець запиту активізує блок ПДП. Блок ПДП посилає в пам'ять сигнал читання або запису і визначає осередок ОЗП, із яким почнеться обмін даними. Блок ПДП посилає ці сигнали, після того, як одержить від МП сигнал підтвердження. Регістр даних передає дані з ОЗП в ПП і з ПП в ОЗП. При ПДП процесор звільняється від керування операціями вводу - виводу і може паралельно виконувати основну програму. ПДП забезпечує більш висока швидкодія і більш високу продуктивність роботи ЕОМ.