- •(Технический университет) Кафедра «Электроника и электротехника» курсовая работа

- •Исходные данные для проектирования.

- •П та1 ринцип работы схемы.

- •Технология изготовления схемы.

- •3. Топология и разрез транзисторов.

- •Расчет параметров элементов схемы.

- •Расчет емкостей.

- •Емкости перекрытия каналов

- •Емкости p-n переходов

- •5. Расчет с помощью программы p-Spice.

- •5.1. Передаточная характеристика схемы.

- •Параметры схемы

- •5.2. Переходная характеристика схемы.

- •Используемая литература.

5. Расчет с помощью программы p-Spice.

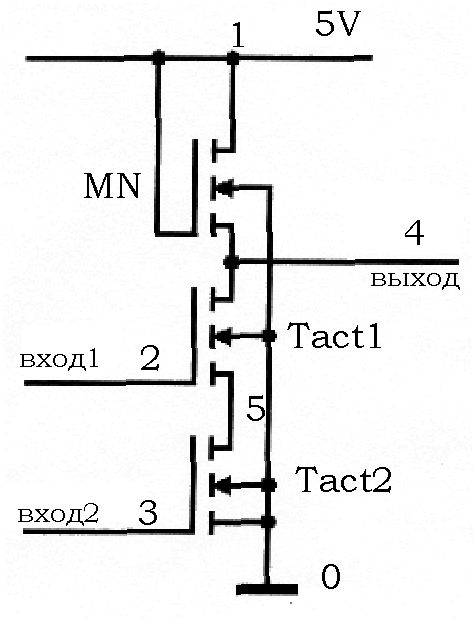

Перед расчетом необходимо обозначить узлы и элементы схемы:

5.1. Передаточная характеристика схемы.

Входной файл:

KP_nMOS_static

Vpit 1 0 5V

Vin1 2 0 5V

Vin2 3 0 5V

MN 1 1 4 0 nmosn

Mact1 4 2 5 0 nmosa

Mact2 5 3 0 0 nmosa

.model nmosn nmos(level=1 Vto=1.33 Uo=450 Tox=100n W=6u L=24u

+CBS=0.664pF CBD=0.664pF CGBO=6.37e-10 CGDO=3.54e-10 CGSO=3.54e-10)

.model nmosa nmos(level=1 Vto=1.33 Uo=450 Tox=100n W=30u L=6u

+CBS=0.929pF CBD=0.929pF CGBO=3.186e-9 CGDO=3.54e-10 CGSO=3.54e-10)

.op

.DC Vin1 0 5 0.01

.print DC v(4)

.probe

.end

В

В

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

Параметры схемы

Из полученного графика находим:

Уровень

логической единицы:

![]()

Уровень

логического нуля:

![]()

Логический

перепад:

![]()

Порог

переключения:

![]()

![]()

Помехоустойчивость

по положительной помехе:

![]()

Помехоустойчивость

по отрицательной помехе:

![]()

5.2. Переходная характеристика схемы.

Входной файл:

KP_nMOS_trans

Vpit 1 0 5V

Vin1 2 0 pulse(0.218 3.668 10u 10u 20u 150u 323u)

Vin2 3 0 3.668V

C1 4 0 15pF

MN 1 1 4 0 nmosn

Mact1 4 2 5 0 nmosa

Mact2 5 3 0 0 nmosa

.model nmosn nmos(level=1 Vto=1.33 Uo=450 Tox=100n W=6u L=24u

+CBS=0.664pF CBD=0.664pF CGBO=6.37e-10 CGDO=3.54e-10 CGSO=3.54e-10)

.model nmosa nmos(level=1 Vto=1.33 Uo=450 Tox=100n W=30u L=6u

+CBS=0.929pF CBD=0.929pF CGBO=3.186e-9 CGDO=3.54e-10 CGSO=3.54e-10)

.op

.tran 0.1u 400u

.print tran v(4) v(2) i(vpit)

.probe

.end

![]()

![]()

![]()

![]()

![]()

![]()

![]()

Параметры схемы

Из

полученного графика находим:

![]()

Длительность задержек:

![]()

![]()

![]()

Длительность фронтов:

![]()

![]()

5.3. Статическая и динамическая мощности, потребляемые схемой.

Входной файл для определения тока потребления такой же, как и для динамики.

Из графика видно, что ток потребления при логической единицы на выходе равен нулю:

![]()

Тогда, для определения статической мощности воспользуемся формулой:

![]()

Динамическая мощность.

Частота переключения

![]()

Для определения динамической мощности воспользуемся формулой:

![]()

6. Топология всей схемы.

Хм-м-м-м, а это в отдельном файле.

7. Сравнение с аналогами, выпускаемыми промышленностью.

В качестве схемы для сравнения использовались цифровые базовые матричные кристаллы на основе n-МОП-структур типа К1801ВП1.

|

Параметр схемы |

Не менее |

Не более |

Данная схема |

|

Напряжение питания, В |

4,75 |

5,25 |

5 |

|

Напряжение

логического нуля

|

— |

0,4 |

0,218 |

|

Напряжение

логической единицы

|

2,7 |

— |

3,668 |

|

Ток потребления, мкА |

— |

300 |

22,55 |

|

Максимальная входная частота, кГц |

— |

8 |

3,095 |

|

Среднее время задержки, мкс |

5,5 |

7,5 |

5,8905 |

Используемая литература.

-

У. Тилл, Дж. Лаксон. Интегральные схемы. Материалы, приборы, изготовление. М. 1985.

-

Валиев К.А., Кармазинский А.Н., Королев М.Р. Цифровые схемы на МДП-транзисторах. М. 1971.

-