- •Московский государственный институт электроники и математики

- •Изучение статических и динамических характеристик логических интегральных транзисторно-транзисторных схем.

- •Москва 1999

- •1. Цели работы:

- •2. Краткие теоретические сведения.

- •3. Описание стенда.

- •Рабочее задание.

- •Требования к отчету по выполняемой работе.

- •5. Контрольные вопросы.

- •6. Рекомендуемая литература.

МИНИСТЕРСТВО ОБЩЕГО И ПРОФЕССИОНАЛЬНОГО

ОБРАЗОВАНИЯ РОССИЙСКОЙ ФЕДЕРАЦИИ

Московский государственный институт электроники и математики

(Технический университет)

Кафедра электроники и электротехники

Изучение статических и динамических характеристик логических интегральных транзисторно-транзисторных схем.

Методические указания

к лабораторной работе

Москва 1999

1. Цели работы:

Целями лабораторной работы являются:

Изучение особенностей режимов работы и параметров интегральных ТТЛ-схем;

Исследование передаточных характеристик ТТЛ-схем;

Исследование переходных характеристик схем, характеризующих быстродействие схемы;

Приобретение навыков работы с интегральными схемами;

Приобретение навыков расчета схем с помощью программы схемотехнического анализа РSPICE.

В данной работе исследуется полупроводниковая интегральная микросхема 155 серии (155 ЛАЗ).

Лабораторная работа выполняется на лабораторном стенде УМ -16 с использованием осциллографа OI -55, вольтметров универсальных В7-26, миллиамперметра.

Интегральными схемами транзисторно - транзисторной логики называются логические схемы, во входной цепи которой используются многоэмиттерные транзисторы. На их основе были разработаны ТТЛ схемы со сложным инвертором. Использование сложного инвертора в ТТЛ схемах позволяет увеличить коэффициент разветвления по выходу, повысить помехоустойчивость, снизить стоимость схем.

2. Краткие теоретические сведения.

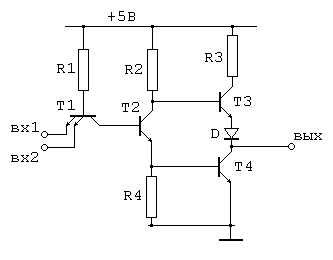

Рассмотрим работу элемента ТТЛ со сложным инвертором, принципиальная схема которого представлена на рис. 1. Пусть на один вход подается напряжение, изменяющееся от 0 до уровня логической единицы, на остальные входы поданы постоянные логические единицы. При Uвх=0 ток коллектора МЭТ равен нулю, поэтому потенциалы на базах транзисторов T2 и T4 и эти транзисторы закрыты. Потенциал базы транзистора T3 высок и поэтому транзистор T3 открыт, на выходе схемы - высокий уровень напряжения, соответствующий логической единице.

С ростом входного напряжения схемы Uвх не меняется до тех пор, пока не начнет открываться транзистор T2. Тогда появляется ток коллектора T2 и потенциал коллектора T2 изменяется на величину DUк2=B2Iб2R2, это изменение через эмиттерный повторитель передается на выход схемы. Когда входное напряжение превысит сумму порогов открывания транзисторов T2 и T4, ток базы T2 резко возрастает, потенциал коллектора T2 резко уменьшается и выходное напряжение падает. При выходном напряжении, превышающем напряжение на эмиттерных переходах транзисторов T2 и T4 в режиме насыщения (около 1,2 - 1,4 В ), транзистор T3 закрывается и выходное напряжение становится равным напряжению насыщения Uкэнас транзистора T4.

Рис. 1.

Основные характеристики схемы ТТЛ со сложным инвертором приведены на рис. 2.

На первом участке передаточной характеристики, при U 4вх 0<U 4бо2 0, выходное напряжение равно напряжению логической единицы:

Uвых=U1=E-Uбо3-Uдо

где: Uбо - порог открывания транзистора, Uдо - напряжение на открытом диоде.

На втором участке передаточной характеристики, при Uбо2<Uвх<Uбо2+Uбо4, выходное напряжение уменьшается на величину:

DUвых=-(R2/R4)DUвх,

где: DUвх=Uвх-Uкн1-Uбо3, Uкн1- напряжение на коллекторе насыщенного транзистора T1.

Для третьего участка ( при Uбо2+ Uбо4<Uвх<Uвх+Uбн)

DUвых=-R2(R4+rвх)/( R4 rвх) DUвх,

где: rвх - входное сопротивление транзистора T4.

Уровень логического нуля на четвертом участке передаточной характеристики ( при Uвх>Uбн2+Uбн4) определяется:

DUвых =U0=Uбк4.

Входная характеристика схемы Iвх=f(Uвх) имеет три участка (рис. 2,б). При 0<Uвх<Uбо2+Uбо4 входной ток вытекает из схемы и его абсолютная величина равна:

Iвх=(E-Uбн1-Uвх)/R1,

При Uвх>Uбо2+Uбо4 ток, текущий через сопротивление R1, разветвляется: часть продолжает вытекать из схемы, а другая часть течет в базу транзистора T2. На третьем участке входной характеристики ток втекает в схему и определяется током обратносмещенного эмиттерного p-n - перехода:

Iвх=(E-Uбн1- Uбн2- Uбн4)bi1/R1.

Важной характеристикой схемы является зависимость тока источника питания от входного напряжения (Iпит=f(Uвх)), показанная на рис. 2в. Токи, потребляемые в режимах логического нуля и логической единицы значительно меньше, чем при переключении. Если хотя бы на одном входе Uвх=U0, то:

Iпит =(E-Uбн1- Uвх)/ R1,

если на всех входах Uвх=U0 то:

Iпит =(E- Uбн2- Uбн4- Uбн1)/ R1+(E- Uкн2- Uбн4)/R2.

При переходе из состояния логического нуля в логическую единицу и наоборот ток источника питания резко возрастает и его максимальная величина равна:

Iпитmax=(E-Uбэ2-Uбэ4-Uкб1)/ R1+(E-Uкэ2-Uбэ4)/ R2+(E-Uкэ3-Uдо-Uкэ4)/R3.

В состояниях логического нуля и логической единицы потребляемая мощность равна, соответственно:

Pп1=EIпит1, Pп0=EIпит0.

Задержка выключения схемы определяется временем рассасывания носителей заряда в транзисторах T2 и T4 и величиной емкости нагрузки Cн. Задержка включения определяется фронтом транзистора T3 и емкостью Cн.

Uвых

I

II

II

III

IV

Uвх

Iвх а)

Iвх а)

III Uвх

II

I

o

Iвх

Iпит б)

Uвх

в)

Рис.2

а) - передаточная характеристика;

б) - входная характеристика;

в) - зависимость тока потребления от входного напряжения;