- •Методические указания

- •1. Цель и практическое содержание методических указаний

- •2.2. Регистры и стек 32-разрядных процессоров Регистры

- •Регистры общего назначения

- •2.3. Организация памяти

- •Типы адресов

- •Режимы адресации

- •2.4. Прерывания и исключения

- •2.5. Основные понятия Защищенного режима работы процессора

- •2.6. Механизмы страничной переадресации

- •Базовый механизм страничной переадресации.

- •Режим pse

- •Режим pae.

- •2.7. Примеры команд 32-разрядного процессора

- •3. Задание на выполнение работы

- •Варианты задания

- •4. Содержание отчета по курсовой работе

- •5. Оформление пояснительной записки

Режим pse

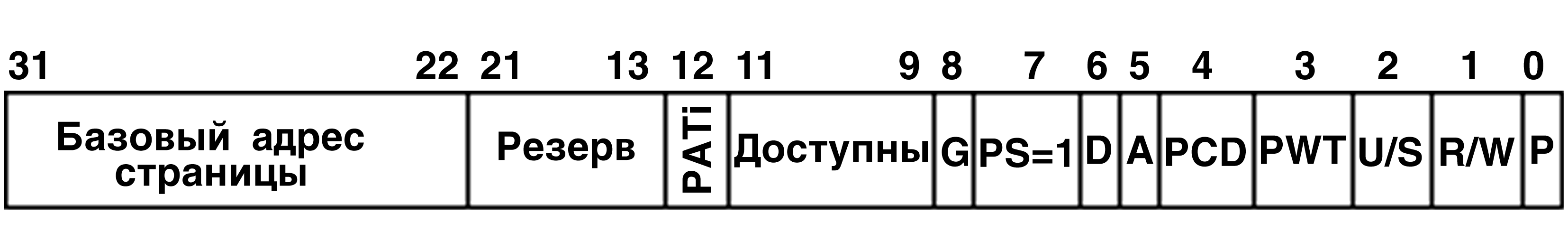

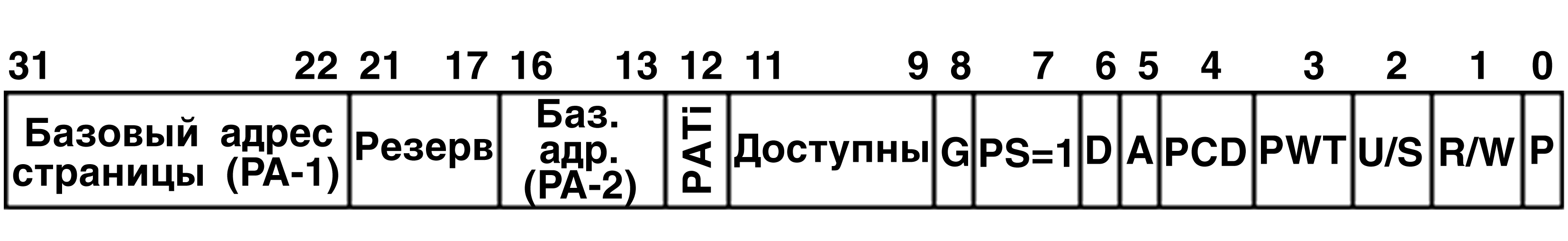

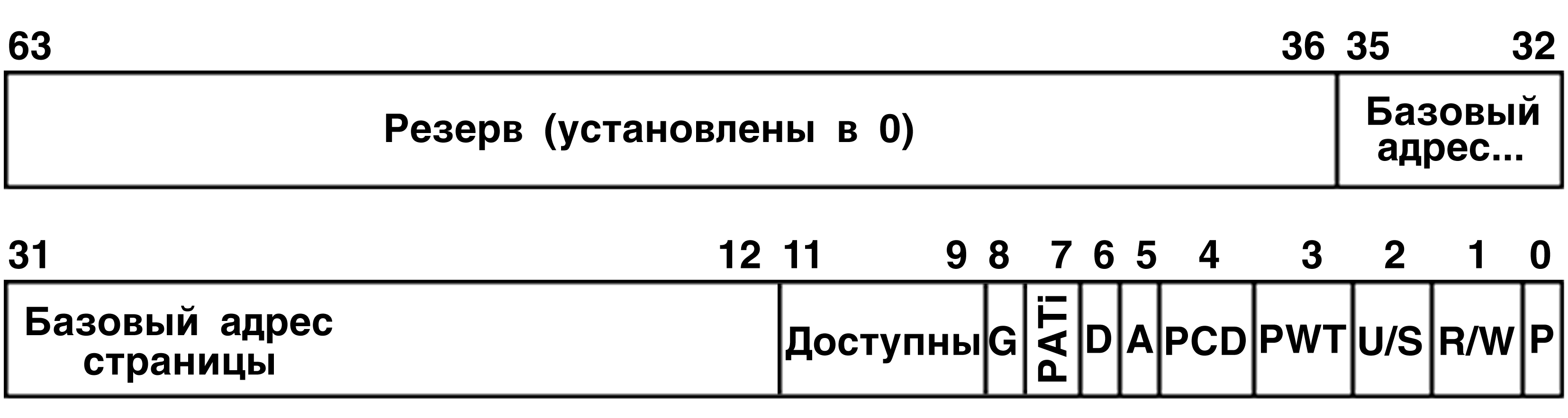

Процессоры Pentiumи выше кроме стандартных страниц 4 Кбайт могут оперировать и страницами размером 4 Мбайт, что позволяет уменьшить накладные расходы на обслуживание страничного режима при возросших потребностях программ в памяти. Расширение размера страницы (PageSizeExtension) разрешается установкой битаPSEв регистреCR4. ПриCR4.PSE=0 страничное преобразование работает по базовой схеме (см. рис. 5). ПриCR4.PSE=1 процессор анализирует бит 7, определенный теперь какPS(PageSize- размер страницы) строки каталога страниц (PDE). ЕслиPDE.PS=0, эта строка ссылается на таблицу страниц размером 4 Кбайт, и обработка идет по схеме, представленной на рис. 5. ЕслиPDE.PS=1, то биты [12:31] этой строки являются базовым физическим адресом страницы размером 4 Мбайт - здесь ступень таблицы страниц исключена (рис. 8). Формат строки каталога (PDE) для страницы с расширенным размером приведен на рис. 9. В процессорахPentiumIIIпоявилась возможность использования 36-битной физической адресации для страниц размером 4 Мбайт - режимPSE-36. ФорматPDEдля таких страниц приведен на рис. 10.Здесь ранее неиспользуемые биты [13:16] хранят старшие 4 бита (РА-2) физического адреса А[36:32] (прежде они должны были быть нулевыми). Новый битPATiиспользуется для задания атрибута страниц.

Рис.9.

СтрокаPDEдля страницы

4Мб и 32-разрядного физического адреса

Рис.9.

СтрокаPDEдля страницы

4Мб и 32-разрядного физического адреса

Рис. 8. Страничная переадресация в режиме PSE

Рис. 10. Строка каталога (PDE) для страницы 4 Мбайт для 36-битного физического адреса (PSE-36).

Режим pae.

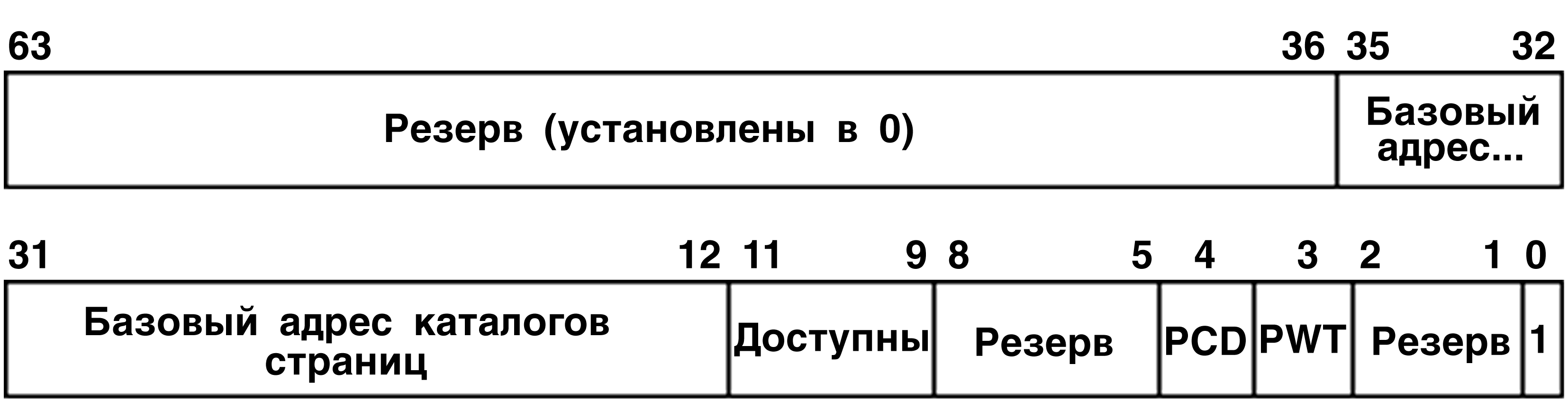

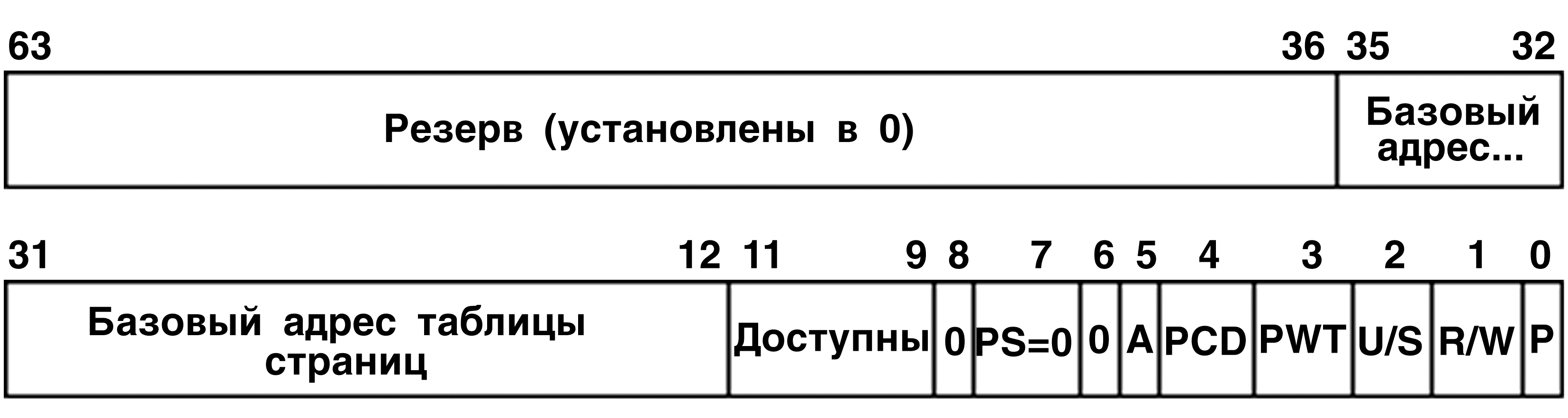

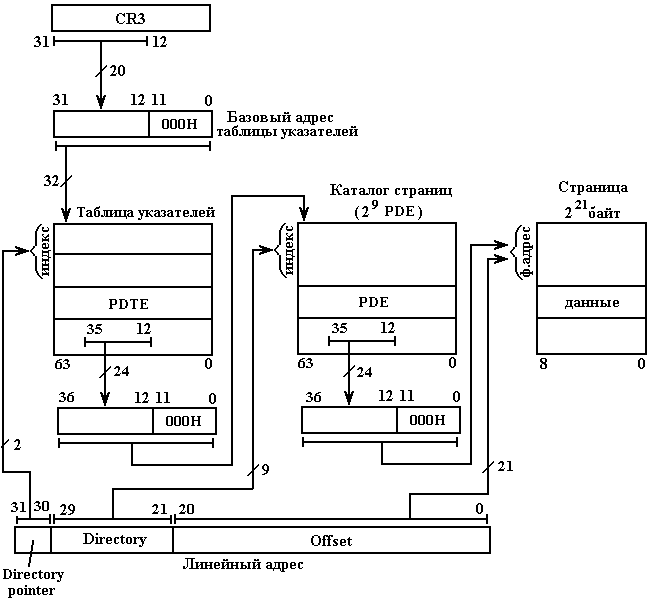

Все процессоры Р6 поддерживают расширение физического адреса (PhysicalAddressExtensions) до 64 Гбайт. Это расширение включается установкой бита РАЕ в регистреCR4, при этом расширениеPSEстановится недоступным (битPSEигнорируется). Здесь блок страничной переадресации оперирует уже 64-битными элементами (рис. 11-14).

Р ис.

11.PDPTE. Строка таблицы

указателей на каталоги.

ис.

11.PDPTE. Строка таблицы

указателей на каталоги.

Рис. 12. PDE4K. Строка каталога для страницы 4 Кбайт.

Рис. 13. PTE4K. Строка таблицы для страниц 4 Кбайт.

Рис. 14. PDE2M. Строка каталога для страниц 2 Мбайт

32-битный регистр CR3 хранит указатель (PageDirectoryBasePointer) на маленькую таблицу 64-битных указателей, находящуюся в первых 4Гбайт памяти. Два старших бита [30:31] линейного адреса выбирают из этой таблицы указатель на одну из 4 таблиц каталогов.

Рис.

15. Страничная переадресация в режимеPAEдля страниц 4 Кбайт.

Рис.

15. Страничная переадресация в режимеPAEдля страниц 4 Кбайт.

Следующие 9 бит [21:29] линейного адреса выбирают элемент из этой таблицы, который, в зависимости от бита PS, может быть как ссылкой на таблицу страниц (PS=0), так и базовым адресом страницы памяти (PS=1). ПриPS=0 биты [12:20] линейного адреса выбирают страницу размером 4 Кбайт из таблицы, а биты [0:11] являются смещением в этой странице. ПриPS=1 [20:0] линейного адреса являются смещением внутри страницы размером 2 Мбайт. Схемы страничного преобразования для режима РАЕ приведены на рис. 15 и 16, а структура элементов - на рис. 16. Для задания атрибута страниц в элементы, описывающие страницы, введен новый битPATi.

Рис.

16. Страничная переадресация в режиме

PAE

для страниц 2 Мбайт.

Рис.

16. Страничная переадресация в режиме

PAE

для страниц 2 Мбайт.