- •Методические указания

- •1. Цель и практическое содержание методических указаний

- •2.2. Регистры и стек 32-разрядных процессоров Регистры

- •Регистры общего назначения

- •2.3. Организация памяти

- •Типы адресов

- •Режимы адресации

- •2.4. Прерывания и исключения

- •2.5. Основные понятия Защищенного режима работы процессора

- •2.6. Механизмы страничной переадресации

- •Базовый механизм страничной переадресации.

- •Режим pse

- •Режим pae.

- •2.7. Примеры команд 32-разрядного процессора

- •3. Задание на выполнение работы

- •Варианты задания

- •4. Содержание отчета по курсовой работе

- •5. Оформление пояснительной записки

2.6. Механизмы страничной переадресации

Страничное управление (Paging) памятью является средством организаций виртуальной памяти с подкачкой страниц по запросу (Demand-PagedVirtualMemorу). В отличие от сегментации, которая организует программы и данные в модули различного размера, страничная организация оперирует с памятью как с набором страниц одинакового размера. В момент обращения страница может присутствовать в физической оперативной памяти, а может быть выгруженной во внешнюю (дисковую) память. При обращении к выгруженной странице памяти процессор вырабатывает исключение #PF- отказ страницы,а программный обработчик исключения (часть ОС) получает необходимую информацию для свопинга - «подкачки» отсутствующей страницы с диска.

Многие процессоры шестого поколения имеют разрядность шины адреса 36 бит, что позволяет адресовать до 64 Гбайт физической памяти. Поскольку архитектура 32-разрядных процессоров предполагает разрядность линейного адреса только 32 бит, старшие 4 бита могут появиться только в результате работы блока страничной переадресации. Без использования дополнительных возможностей переадресации (РАЕ или РSE-36) биты внешней шины адреса А[32:35] принудительно обнуляются.

Базовый механизм страничной переадресации.

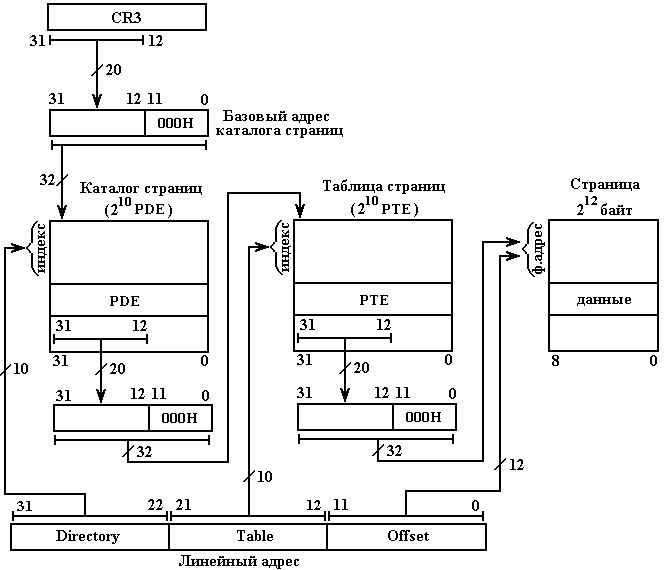

Входной информацией для блока страничной переадресации (БСП) является: линейный адрес, который выбирается из SDC[64:95] и выставляется на ША к БСП. Базовый механизм страничного управления памятью использует двухуровневую табличную трансляцию линейного адреса в физический (рис. 5).

Рис.

5. Базовый механизм страничной

переадресации.

Рис.

5. Базовый механизм страничной

переадресации.

Механизм имеет три части:

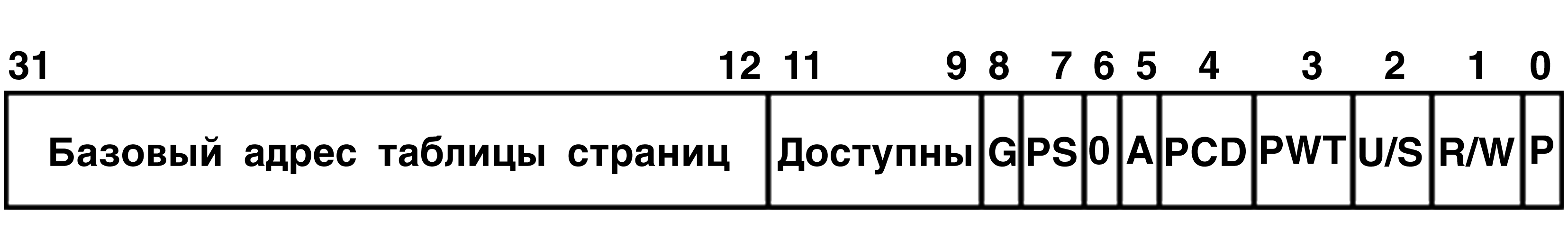

- каталог страниц(PD) размером 4 Кбайт содержит 1024 32-разрядных строки (PDE). Каждая строка (рис. 6) содержит 20 старших бит адреса таблицы следующего уровня (младшие биты этого адреса всегда нулевые) и признаки (атрибуты) этой таблицы. Индексом поиска в каталоге страниц являются 10 старших бит линейного адреса (А22-А31).

Рис.

6. Строка каталога (PDE).

Рис.

6. Строка каталога (PDE).

- таблицы страниц(PT) также имеет 1024 строки РТЕ (PageTableEntry) аналогичного формата (рис. 7), но эти строки содержат базовый физический адрес (PageFrameAddress) и атрибуты самих страниц. Индексом поиска в таблице являются биты А12-А21 линейного адреса.

Рис.

7. Строка таблицы (PTE).

Рис.

7. Строка таблицы (PTE).

- сами страницы(PF).

Табл. 10.

Биты атрибутов строк PDE каталога и PTE таблицы

|

Бит |

Действие |

|

P |

Бит присутствия. Р=1 означает возможность использования данной строки для трансляции адреса. Бит присутствия вхождений в таблицы, используемые текущим исполняемым кодом, должен быть установлен. Программный код не должен его изменять «на ходу». Если Р=0, то все остальные биты доступны операционной системе и могут использоваться для получения информации о местонахождении данной страницы. |

|

A |

Признак доступа, который устанавливается перед любым чтением или записью по адресу, в преобразовании которого участвует данная строка. |

|

D |

Признак, который устанавливается перед операцией записи по адресу, в преобразовании которого участвует данная строка. Таким образом помечается использованная — «грязная» страница, которую в случае замещения необходимо выгрузить на диск. |

|

OS Reserved |

Программно использует ОС. Оно может хранить, например, информацию о «возрасте» страницы, необходимую для реализации замещения по алгоритму LRU (Least Recently Used — наиболее давно не использовавшаяся страница замещается первой). |

|

PWT |

Определяет политику записи при кэшировании |

|

PCD |

Запрещает кэширование памяти для обслуживаемых страниц или таблиц (используются на процессорах 486+). |

|

PS |

Задает размер страницы (только в PDE). При PS=0 страница имеет размер 4 Кбайт, PS=1 используется в расширениях РАЕ и PSE (см. ниже). |

Механизм включается установкой бита PG=1 в регистреCR0. РегистрCR2 хранитлинейный адрес отказа(PageFaultLinearAddress) - адрес памяти, по которому был обнаружен последний отказ страницы. Регистр СR3 хранитфизический адрес каталога страниц(PageDirectoryPhysicalBaseAddress). Младшие 12 бит адреса всегда нулевые (каталог выравнивается по границе страницы).Физический адресстроки таблицы получается из адреса страницы, взятого из таблицы, и младших 12 бит линейного адреса. Строки каталога и таблицы имеют следующие биты атрибутов (см. табл.10).

Обращение при каждой операции доступа к памяти к двум таблицам (PDиPT), расположенным в памяти, существенно снижает производительность. Для предотвращения этого замедления в процессор введенбуфер ассоциативной трансляцииТLB(TranslationLookasideBuffer) для хранения интенсивно используемых строк таблиц1.

Когда страничное управление разрешено (бит PG=1 вCR0), блок страничной переадресации получает 32-разрядный линейный адрес от блока сегментации. Его старшие 20 бит сравниваются со значениями из TLB, и, в случае обнаружения строки, физический адрес вычисляется по начальному адресу страницы, полученному из ТBL, а затем выводится на шину адреса. Если соответствующей строки вTLBнет, производится чтение строки из страничного каталога. Если строка имеет бит Р=1 (таблица присутствует в памяти), в ней устанавливается бит доступа А и производится чтение указанной ею строки из таблицы второго уровня. Если и в этой строке Р=1, процессор обновляет в ней биты А иD, вычисляет физический адрес и, наконец, производит обращение по этому адресу. Если на этих этапах встречается Р=0, вырабатывается исключение #PF, обработчик которого должен принять меры по загрузке затребованной страницы в оперативную память. Поскольку это включение классифицируется как отказ, после его обработки (успешной) повторяется доступ к затребованной ячейке памяти.

Обработчик исключения #PF, поддерживающий подкачку страниц по запросу, должен скопировать страницу с внешней (дисковой) памяти в оперативную, загрузить адрес страницы в строку таблицы и установить бит присутствия Р. Поскольку в TLB могла оставаться старая некорректная копия строки, необходимо объявить содержимое TLB недействительным (произвести очистку). После этого процесс, породивший исключение, может быть продолжен.

В первых 32-разрядных процессорах размер страницы составлял 4 Кбайт. Начиная с Pentium, появилась возможность увеличения размера страницы до 4 Мбайт, одновременно с использованием страниц размером 4 Кбайт (режимPSE). В процессорах Р6 был введен режим расширения физического адреса до 36 бит, при котором допустимы страницы размером 4 Кбайт и 2 Мбайт (режим РАЕ). ВPentiumIIIпоявилась возможность использования страниц размером 4 Мбайт с 36-битной физической адресацией (режимPSE-36). Режимом страничной переадресации управляют битыPGв регистреCRO, флагиPAEиPSEвCR4 и бит размера страницыPSвPDE- элементе каталога страницы (таблица 11).

Табл. 11.

Режимы страничной переадресации.

|

CR0.PG |

CR4.PAE |

CR4.PSE |

PDE.PS |

Размер страницы |

Разрядность физического адреса, бит |

Механизм страничной переадресации |

|

0

1 1 1 1 1 1 |

X

0 0 0 0 1 1 |

Х

0 1 1 1 X X |

Х

X 0 1 1 0 1 |

Линейный адрес равен физическому 4Кб 4Кб 4Мб 4Мб 4Кб 2Мб |

32

32 32 32 36 36 36 |

Трансляция не осуществляется базовый базовый PSE PSE-36 PAE PAE |