- •1.Усилители. Параметры и характеристики.

- •2.Линейные искажения в усилителях.

- •3.Нелинейные искажения в усилителях.

- •4. Переходная характеристика усилителя.

- •5.Амплитудно-фазовая характеристика усилителя.

- •6.Шумы в электронных схемах.

- •7.Расчет рабочей точки стандартных усилительных каскадов на бт.

- •8.Расчет рабочей точки стандартных усилительных каскадов на транзисторе с управляющим переходом.

- •9. Расчёт р.Т. Усилительных каскадов с индуцированным каналом.

- •10. Расчёт р.Т. Усилительных каскадов на транзисторе со встроенным каналом.

- •11. Обратные связи в усилителях.

- •12. Влияние обратных связей на коэффициент усиления.

- •13. Влияние обратной связи на стабильность работы усилителя.

- •14. Термостабилизация в усилительных каскадах.

- •15. Обратная связь в многокаскадных усилителях.

- •16. Однокаскадный усилитель на бт с оэ(Схема).

- •17.Однокоскадный усилитель rc-типа на биполярном транзисторе с общим эмиттером .Анализ параметров по переменному току.

- •18. Однокаскадный усилитель rc-типа на биполярном транзисторе с общим коллектором .Анализ параметров по переменному току.

- •19. Однокаскадный усилитель rc-типа на биполярном транзисторе с общей базой .Анализ параметров по переменному току.

- •20. Усилительный каскад с последовательной оос по напряжению.

- •21.Усилители постоянного тока. Назначение, параметры, основные особенности.

- •22.Методы борьбы с дрейфом нуля. Местные отрицательные обратные связи.

- •23.Методы борьбы с дрейфом нуля. Балансные (мостовые схемы).

- •24.Методы борьбы с дрейфом нуля.Дифференциальный каскад.

- •25. Метод модуляции-демодуляции.

- •26. Комбинированные методы борьбы с дрейфом нуля.

- •27. Операционные усилители.

- •28. Инвертирующий усилитель.

- •29. Неинвертирующий усилитель.

- •30. Применение оу для выполнения нелинейных операций.

- •31. Применение оу для моделирования математических операций.

- •32. Активные фильтры.

- •33 . Электронные ключи. Параметры и характеристики.

- •34 . Ключ на бт. Построение передаточной характеристики.

- •35. Улучшенные схемы ключей на бт.

- •36. Ключ на переключателе тока.

- •37. Ключ на полевых транзисторах.

- •38. Комплиментарный ключ.

- •39. Семейства логических элементов.

- •40. Ттл, ттлш –логика.

- •41. Дтл-логика.

- •42. Эсл-логика.

- •43-44. N-моп логика (элементы типов и-не и или-не).

- •44.P-моп логика.

- •45. Кмоп логика.

- •46. Триггерная ячейка.

- •47.Триггер с раздельными входами.

- •48.Интегральный триггер.

- •49.Rs–триггер.

- •50.Ms-триггер.

- •51.D- , т-триггеры

- •52. Jk-триггеры

- •53. Мультикомплексоры.

- •54.Преобразователи кодов.

- •55. Простейшие коды.

- •56. Усилитель мощности.

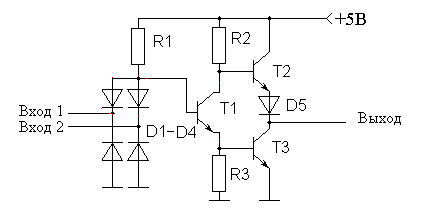

41. Дтл-логика.

Группа ДТЛ представляет собой сочетание диодных логических ячеек с транзисторным инвертором. Базовым лог.элементом всех серий ДТЛ является эл-т Шеффера(эл-т И-НЕ),реализующий операцию логического умножения с отрицанием.Принципиальная схема типового элемента 2И-НЕ диодно-транзисторной логики (ДТЛ) приведена на рис. 2. Если хотя бы на одном из входов (число которых может быть более двух) появляется уровень 0 (низкое напряжение), то соответствующий входной диод открывается и сигнал низкого напряжения практически закрывает транзистор Т1. При этом Т3 будет закрыт, а Т2 открыт и на выходе установится уровень 1 (высокий уровень). Для получения на выходе уровня 0 нужно, чтобы все входные диоды были закрыты, т.е. на входах должны быть уровни 1.

|

|

Рис. 2. Принципиальная

схема ДТЛ

Рис. 2. Принципиальная

схема ДТЛ

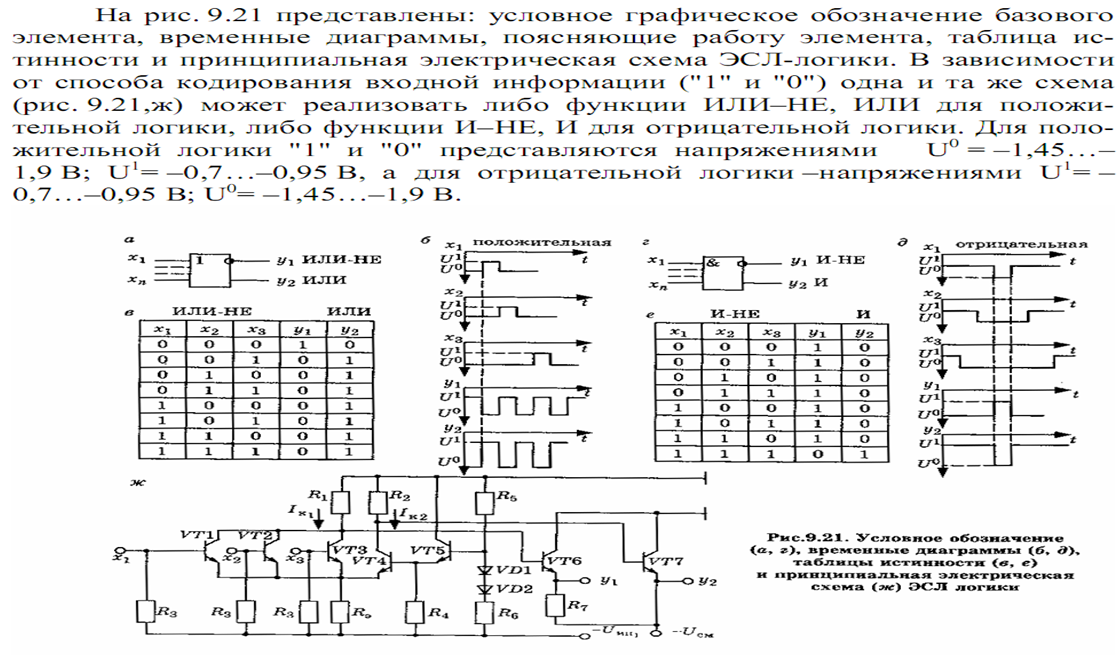

42. Эсл-логика.

Цифровые схемы ЭСЛ составляют схемы на переключателях тока с объединенными эмиттерами,обладающие по сравнению с другими типами цифровых схем,наибольшим быстродействием и большой потребляемой мощностью.

Большое быстродейсвие ЭСЛ обеспечивается:1)за счет работы транзисторов в ненасыщенном(линейном) режиме. 2)за счет применения на выходах схемы эммитерных повторителей,ускоряющих процесс заряда и разряда нагрузочных емкостей. 3)за счет ограничения перепада выходного напряжения,что приводит к снижению статической помехоустойчмвости.

Логический элемент состоит из трех частей: токового переключателя

(ТП), эмиттерных повторителей (ЭП), источника опорного напряжения (ИОН).

Рассмотрим принцип работы базового лог элемента для положительной логики. Если на все логические входы подается напряжение низкого уровня, соответствующее логическому нулю, то транзисторы VТ1–VТ3 закрываются, а транзистор VТ 4 открывается, так как напряжение на его базе становится выше, чем на базах входных транзисторов. Через открытый транзистор протекает ток Iк2, значение которого задается резистором Rэ, и создает падение напряжения на резисторе R2. Потенциал коллектора транзистора VТ4 при этом понижается и подается на вход эмиттерного повторителя, собранного на транзисторе VТ7. На выходе эмиттерного повторителя получается низкий уровень напряжения, соответствующий логическому нулю.

В это же время через резистор R1 левой ветви токового ключа протекает небольшой обратный ток Iк1. Потенциал коллектора транзистора VТ3 повышается и поступает на базу эмиттерного повторителя транзистора VТ6. На выходе транзистора VT6 имеем большой потенциал, логическую единицу, при этом выполняется логическая операция ИЛИ–НЕ.

43-44. N-моп логика (элементы типов и-не и или-не).

44.P-моп логика.

МОП (металл-оксид-полупроводник) — один из видов полевого транзистора, в котором управляющий электрод (затвор) отделён от канала слоем диэлектрика, в простейшем случае, оксида кремния.

МОП-транзистор с ндуцированным n(p)-каналом. МОП-транзистор, как и другие полевые транзисторы, управляется напряжением. МОП-транзисторы могут быть n-канальными или p-канальными, в первых используются электроны, во вторых — дырки. Логический МОП-элемент представляет собой несколько транзисторов, соединённых либо последовательно (для получения функции «И-НЕ»), либо параллельно (для получения функции «ИЛИ-НЕ»). Такой же транзистор, только постоянно включённый, служит нагрузочным резистором логического элемента. Увеличение сопротивления открытого канала этого транзистора уменьшает потребляемую мощность, но одновременно и скорость действия логического элемента. Управлять этим параметром можно, изменяя геометрические размеры, например, ширину канала.