- •Проектирование многоразрядного десятичного сумматора комбинационного типа

- •1. Цель и практическое содержание методических указаний

- •1.1. Цель работы

- •1.2. Краткое содержание

- •2. Теоретическая часть

- •2.1. Теория о двоично-десятичном кодировании и свойствах кодов

- •Примеры двоично-десятичных кодов

- •2.2. Сложение одноразрядных десятичных числе со знаком в двоично-десятичном коде

- •0.1000.0111.0101

- •2.3. Проектирование функциональной логической схемы и её реализация в заданном базисе логических элементов

- •2.3.1. Общие принципы

- •2.3.2. Проектирование логической схемы одноразрядного двоичного сумматора

- •2.3.3. Проектирование одноразрядного десятичного сумматора в коде 8421

- •2.3.4. Проектирование дополнительных схем

- •2.3.5. Построение функциональной схемы 3-х разрядного десятичного сумматора

- •2.4. Устройство управления многоразрядным сумматором

- •2.4.1. Проектирование распределителя сигналов

- •2.4.2. Получение общей схемы сумматора

- •2.5. Порядок оформления пояснительной записки

- •Литература

- •Приложение

- •Содержание

2.4.2. Получение общей схемы сумматора

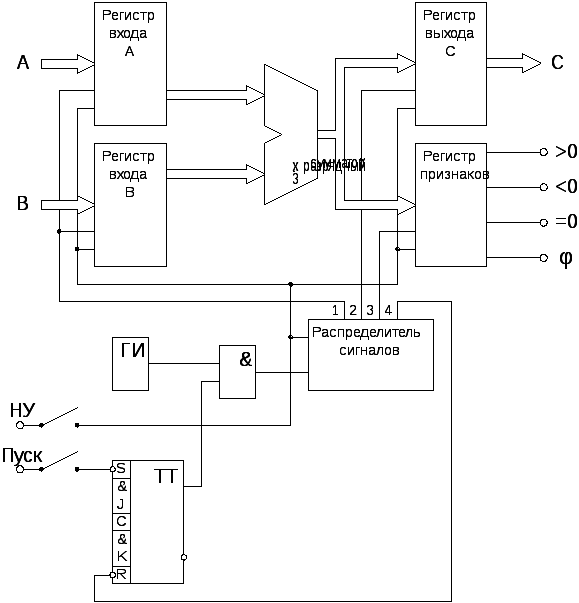

Общая структура 3-х разрядного десятичного сумматора с устройством управления представлена на рисунке 2.4.10.

Рис. 2.4.10. Общая структурная схема 3-х разрядного десятичного сумматора с устройством управления.

По сигналу НУ триггеры регистров и распределителя сигналов устанавливаются в состояние "0". По сигналу «Пуск» триггер пуска устанавливается в состояние "1" и импульсы с ГИ (генератор импульсов) через схему "И" поступают на распределитель сигналов. Последний вырабатывает управляющие сигналы СИ1, СИ2, СИ3 и СИ4. Сигнал СИ4 устанавливает триггер пуска в состояние "0" и отключает тем самым ГИ от распределителя сигналов.

2.5. Порядок оформления пояснительной записки

Исходные данные для проектирования

Количество десятичных разрядов.

Двоично-десятичный код, в котором находятся числа Система логических элементов.

Система логических элементов.

Критерий оптимальности элементов для проектирования логических схем.

Тип триггера для проектирования схемы управления.

Временные параметры синхронизирующей серии импульсов логических элементов.

Исходные данные задаются преподавателем на занятии.

Разработка алгоритма выполнения арифметических операций сложения и вычитания многоразрядных чисел в заданном двоично-десятичном коде.

Разработка алгоритма для одноразрядных десятичных чисел, получение величины коррекции и критерии ее ввода.

Обобщение полученного алгоритма на многоразрядные числа при выполнении операции сложения и вычитания.

Приведение шести примеров на следующие случаи сложения:

Положительная величина (+A) складывается с другой положительной величиной (+B) с получением положительного результата (+C) без переполнения (+A)+(+B)=(+C).

(+A)+(-B)=(+C).

(+A)+(-B)=(-C).

(-A)+(-B)=(-C).

(+A)+(+B)=(-C) — Переполнение разрядной сетки.

(-A)+(-B)=(+C) — Переполнение разрядной сетки.

Разработки функциональной схемы одноразрядного десятичного сумматора комбинационного типа:

Разработка оптимальной схемы (с точки зрения критерия оптимальности) одноразрядного двоичного сумматора с учетом заданного базиса логических элементов.

Разработка схемы коррекции.

Разработка схемы одноразрядного десятичного сумматора.

Разработка дополнительных схем для функционирования многоразрядного десятичного сумматора (все схемы проектируются в заданном базисе логических элементов с учетом критерия оптимальности).

Разработка преобразователя прямого кода в обратный для работы с отрицательными величинами.

Разработка схемы, фиксирующей переполнение разрядной сетки.

Разработка схемы для определения знака суммы.

Разработки функциональной схемы многоразрядного десятичного сумматора.

Разработка устройства управления для многоразрядного десятичного сумматора.

Разработка входных и выходных регистров хранения числовой информации, участвующей в операции сложения.

Разработка регистра признаков результата.

Расчет временных параметров устройства управления.

Разработка схемы для получения управляющих сигналов и схемы пуска выполнения операции сложения.

Общая структура схемы многоразрядного десятичного сумматора комбинационного типа с устройством управления.

Выводы по работе.