- •Глава1 Что такое цифровые микросхемы. Виды цифровых микросхем

- •Глава 2 Области применения цифровых микросхем

- •Глава 3 Условные графические изображения цифровых микросхем (гост)

- •Параметры цифровых микросхем

- •Уровни логического нуля и единицы

- •Входные и выходные токи цифровых микросхем

- •Параметры, определяющие быстродействие цифровых микросхем

- •Описание логической функции цифровых схем

- •Раздел 2

- •Логический элемент "и"

- •Логический элемент "или"

- •Глава 2 Диодно-транзисторная логика (дтл)

- •Глава 3 Транзисторно-транзисторная логика (ттл)

- •Логические уровни ттл микросхем

- •Семейства ттл микросхем

- •Глава 4 Цифровые логические микросхемы, выполненные на комплементарных моп транзисторах (кмоп) Логические кмоп (кмдп) инверторы

- •Логические кмоп (кмдп) элементы "и"

- •Логические кмоп (кмдп) элементы "или"

- •Особенности применения кмоп микросхем

- •Логические уровни кмоп микросхем

- •Семейства кмоп микросхем

- •Глава 5 Согласование цифровых микросхем различных серий между

- •Согласование микросхем из различных серий между собой

- •Согласование по току

- •Согласование микросхем с различным напряжением питания

- •Глава 6 Регенерация цифрового сигнала (Триггер Шмитта)

- •Раздел 3 Арифметические основы цифровой техники.

- •Глава 1

- •Арифметические основы цифровой техники

- •Системы счисления

- •Десятичная система счисления

- •Двоичная система счисления

- •Восьмеричная система счисления

- •Шестнадцатеричная система счисления

- •Глава 2 Преобразование чисел из одной системы счисления в другую

- •Преобразование целых чисел

- •Глава 3 Преобразование дробной части числа

- •Раздел 4

- •2. Законы отрицания a. Закон дополнительных элементов

- •B. Двойное отрицание

- •C. Закон отрицательной логики

- •3. Комбинационные законы

- •A. Закон тавтологии (многократное повторение)

- •B. Закон переместительности

- •Совершенная дизъюктивная нормальная форма (сднф)

- •Совершенная конъюктивная нормальная форма (скнф)

- •Глава 3 Дешифраторы (декодеры)

- •Десятичный дешифратор (декодер)

- •Семисегментный дешифратор

- •Глава 4 Шифраторы (кодеры)

- •Глава 5 Мультиплексоры

- •Особенности построения мультиплексоров на ттл элементах

- •Особенности построения мультиплексоров на кмоп элементах

- •Глава 6 Демультиплексоры

- •Раздел 5 Генераторы

- •Глава 1

- •Генераторы периодических сигналов

- •Усилительные параметры кмоп инвертора

- •Глава 2 Осцилляторные схемы генераторов

- •Глава 3 Мультивибраторы

- •Глава 4 Особенности кварцевой стабилизации частоты цифровых генераторов

- •Глава 5 Одновибраторы (ждущие мультивибраторы)

- •Укорачивающие одновибраторы

- •Расширяющие одновибраторы (ждущие мультивибраторы)

- •Раздел 6 Последовательностные устройства (цифровые устройства с памятью)

- •Глава 1

- •Триггеры

- •Глава 2 rs триггер

- •Синхронный rs триггер

- •Глава 3 d триггеры, работающие по потенциалу (статические d триггеры)

- •Глава 4 Явление метастабильности

- •Глава 5 d триггеры, работающие по фронту (динамические d триггеры)

- •Глава 6 t триггеры

- •Глава 7 jk триггер

- •Глава 8 Регистры

- •Параллельные регистры

- •Глава 9 Последовательные (сдвиговые) регистры

- •Глава 10 Универсальные регистры

- •Глава 11 Счётчики

- •Двоичные асинхронные счётчики

- •Двоичные вычитающие асинхронные счётчики

- •Глава 12 Недвоичные счётчики с обратной связью

- •Глава 13 Недвоичные счётчики с предварительной записью

- •Глава 14 Синхронные счётчики

- •Глава 15 Синхронные двоичные счётчики

- •Раздел 7

- •Современные виды цифровых микросхем.

- •Глава 1

- •Микросхемы малой степени интеграции (малая логика)

- •Глава 2 Программируемые логические интегральные схемы (плис).

- •Классификация плис

- •Глава 3 Программируемые логические матрицы.

- •Глава 4 Программируемые матрицы логики (pal).

- •Глава 5 Сложные программируемые логические устройства (cpld).

- •Внутреннее устройство cpld

- •Разработка цифровых устройств на cpld

- •Глава 6 Программируемые пользователем вентильные матрицы (fpga).

- •Раздел 8

- •Индикаторы.

- •Глава 1

- •Виды индикаторов.

- •Малогабаритные лампочки накаливания

- •Расчет транзисторного ключа

- •Глава 2 Газоразрядные индикаторы.

- •Глава 3 Светодиодные индикаторы.

- •Глава 4 Жидкокристаллические индикаторы.

- •Принципы работы жидкокристаллических индикаторов

- •Режимы работы жидкокристаллических индикаторов

- •Параметры жидкокристаллических индикаторов

- •Формирование цветного изображения

- •Формирование напряжения для работы жидкокристаллического индикатора

- •Глава 5 Динамическая индикация.

- •Раздел 9

- •Синтезаторы частоты.

- •Глава 1

- •Цифровой фазовый детектор.

- •Глава 2 Фазовый компаратор.

- •Глава 3 Цепи фазовой автоподстройки частоты.

- •Глава 4 Умножители частоты

- •Глава 5 Частотный детектор, построенный на основе фапч

- •Раздел 10

- •Особенности аналого-цифрового и цифро-аналогового преобразования.

- •Глава 1

- •Квантование аналогового сигнала по времени

- •Глава 2 Погрешности дискретизатора

- •Погрешность хранения

- •Погрешность выборки

- •Глава 3 Фильтры устранения эффекта наложения спектров (Антиалайзинговые фильтры)

- •Глава 4 Дискретизация сигнала на промежуточной частоте (субдискретизация)

- •Глава 5 Параллельные ацп (flash adc)

- •Глава 6 Последовательно-параллельные ацп

- •Глава 7 ацп последовательного приближения (sar adc)

- •Глава 8 Сигма-дельта ацп

- •Глава 9 Цифроаналоговые преобразователи (цап) с суммированием токов

- •Глава 10 Цифроаналоговые преобразователи r-2r

- •Раздел 11

- •11.1 Основные блоки цифровой обработки сигналов

- •Глава 1 Двоичные сумматоры

- •Глава 2 Умножители

- •Глава 3 Постоянные запоминающие устройства.

- •Глава 4 Цифровые фильтры.

- •11.2 Микросхемы прямого цифрового синтеза радиосигналов.

- •Глава 5 Фазовые аккумуляторы

- •Глава 6 Полярные модуляторы

- •Глава 7 Квадратурные модуляторы.

- •Глава 8 Интерполирующие цифровые фильтры.

- •Глава 9 Однородные интерполирующие цифровые фильтры.

- •Микросхемы цифрового приема радиосигналов

- •Глава 10 Квадратурные демодуляторы.

- •Глава 11 Децимирующие цифровые фильтры.

- •Децимирующий фильтр с конечной импульсной характеристикой

- •Глава 12 Однородные децимирующие цифровые фильтры.

- •Раздел 12 Примеры реализации цифровых устройств

- •12.1 Электронные часы

- •Разработка структурной схемы

- •Глава 2 Разработка принципиальной схемы

- •Глава 3 Разработка принципиальной схемы индикации часов

- •12.2 Последовательные порты

- •Глава 4

- •Глава 5

Децимирующий фильтр с конечной импульсной характеристикой

На рисунке 11.3.2 приведен пример амплитудно-частотной характеристики децимирующего фильтра. Этот фильтр способен подавить мешающие сигналы в полосе трех высокочастотных образов полезного сигнала.

То, что фильтр пропускает на выход только четвертую часть входного спектра, означает, что на выходе подобного фильтра можно снизить частоту дискретизации сигнала в четыре раза.

Глава 12 Однородные децимирующие цифровые фильтры.

Наиболее просто в цифровом виде реализовать рассмотренный нами ранее однородный фильтр, так как для его реализации не требуются умножители. Для однородного фильтра четвертого порядка эта формула выглядит следующим образом:

|

|

(1) |

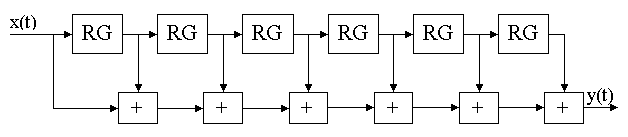

Структурная схема фильтра, реализующего формулу (1), приведена на рисунке 11.3.3.

Рисунок 11.3.3.

Структурная схема однородного фильтра

седьмого порядка

Рисунок 11.3.3.

Структурная схема однородного фильтра

седьмого порядка

При реализации такого фильтра потребуется 6 сумматоров. Во столько же раз уменьшится быстродействии цифрового фильтра. Можно несколько видоизменить структуру данного фильтра. Для сокращения количества выполняемых операций формула 1 может быть переписана в следующем виде:

|

|

(2) |

Эта формула может быть реализована за два действия:

|

|

(3) |

В таком случае для реализации фильтра потребуется два каскада. Первый каскад будет выполнять интегрирование, а второй — фильтр с конечной импульсной характеристикой всего с двумя ненулевыми коэффициентами, равными единице. Структурная схема нового фильтра приведена на рисунке 11.3.4.

Рисунок 11.3.4.

Структурная схема двухкаскадного

фильтра, эквивалентного фильтру,

приведенному на рисунке 11.3.3.

Рисунок 11.3.4.

Структурная схема двухкаскадного

фильтра, эквивалентного фильтру,

приведенному на рисунке 11.3.3.

В этой схеме максимальное время задержки сигнала определяется быстродействием сумматора и временем записи в регистр. Мы увеличили быстродействие почти в семь раз.

Ну а теперь вспомним, для чего нам потребовался фильтр. Правильно. Для уменьшения количества отсчетов в единицу времени. Так как операция децимации линейна, то вторую часть фильтра мы можем перенести на выход дециматора.

При таком схемном решении для формирования того же самого значения времени задержки нам потребуется только один регистр, так как на его вход тактовой синхронизации будет поступать частота в шесть раз меньше, чем частота синхронизации первого регистра. Получившаяся в результате всех преобразований структурная схема фильтра-дециматора приведена на рисунке 11.3.5.

Рисунок 11.3.5.

Структурная схема фильтра-дециматора,

эквивалентного фильтру, приведенному

на рисунке 11.3.3

Рисунок 11.3.5.

Структурная схема фильтра-дециматора,

эквивалентного фильтру, приведенному

на рисунке 11.3.3

Новая схема содержит всего два регистра и два двоичных сумматора, то есть данная схема получилась в три раза проще схемы однородного фильтра, приведенной на рисунке 11.3.4. Получившийся в результате преобразований фильтр трудно назвать однородным, однако для того, чтобы отобразить особенности его импульсной и амплитудно-частотной характеристик, сохраним название "однородный" и для этого фильтра..

Если по техническому заданию требуется еще больший коэффициент децимации по сравнению с рассмотренным выше случаем, то выигрыш при реализации однородного фильтра-дециматора по схеме, приведенной на рисунке 11.3.5, будет еще большим.

Хотелось бы напомнить, что при анализе характеристик однородного фильтра для получения приемлемого уровня подавления мешающего сигнала нам потребовалось включить друг за другом несколько каскадов.

Давайте включим последовательно друг за другом три фильтра-дециматора, как это показано на структурной схеме однородного фильтра, приведенной на рисунке 11.3.6.

Рисунок 11.3.6.

Структурная схема трехкаскадного

фильтра-дециматора

Рисунок 11.3.6.

Структурная схема трехкаскадного

фильтра-дециматора

На рисунке 11.3.7 приведена амплитудно-частотная характеристика четырехкаскадного однородного фильтра. Обратите внимание, что образ полезного сигнала сосредоточен около выходной частоты дискретизации.

Рисунок 11.3.7.

Амплитудно-частотная характеристика

четырехкаскадного однородного

фильтра-дециматора

Рисунок 11.3.7.

Амплитудно-частотная характеристика

четырехкаскадного однородного

фильтра-дециматора

Проанализировав амплитудно-частотную характеристику четырехкаскадного однородного фильтра можно определить, что этот фильтр обладает максимальным подавлением мешающих сигналов именно в полосе частот высокочастотных образов полезного сигнала. Четырехкаскадный однородный фильтр может обеспечить подавление мешающих сигналов, находящихся в зоне высокочастотных образов полезного сигнала до 90 дБ, что вполне достаточно для реализации 16-разрядного представления полезного сигнала.