- •Глава1 Что такое цифровые микросхемы. Виды цифровых микросхем

- •Глава 2 Области применения цифровых микросхем

- •Глава 3 Условные графические изображения цифровых микросхем (гост)

- •Параметры цифровых микросхем

- •Уровни логического нуля и единицы

- •Входные и выходные токи цифровых микросхем

- •Параметры, определяющие быстродействие цифровых микросхем

- •Описание логической функции цифровых схем

- •Раздел 2

- •Логический элемент "и"

- •Логический элемент "или"

- •Глава 2 Диодно-транзисторная логика (дтл)

- •Глава 3 Транзисторно-транзисторная логика (ттл)

- •Логические уровни ттл микросхем

- •Семейства ттл микросхем

- •Глава 4 Цифровые логические микросхемы, выполненные на комплементарных моп транзисторах (кмоп) Логические кмоп (кмдп) инверторы

- •Логические кмоп (кмдп) элементы "и"

- •Логические кмоп (кмдп) элементы "или"

- •Особенности применения кмоп микросхем

- •Логические уровни кмоп микросхем

- •Семейства кмоп микросхем

- •Глава 5 Согласование цифровых микросхем различных серий между

- •Согласование микросхем из различных серий между собой

- •Согласование по току

- •Согласование микросхем с различным напряжением питания

- •Глава 6 Регенерация цифрового сигнала (Триггер Шмитта)

- •Раздел 3 Арифметические основы цифровой техники.

- •Глава 1

- •Арифметические основы цифровой техники

- •Системы счисления

- •Десятичная система счисления

- •Двоичная система счисления

- •Восьмеричная система счисления

- •Шестнадцатеричная система счисления

- •Глава 2 Преобразование чисел из одной системы счисления в другую

- •Преобразование целых чисел

- •Глава 3 Преобразование дробной части числа

- •Раздел 4

- •2. Законы отрицания a. Закон дополнительных элементов

- •B. Двойное отрицание

- •C. Закон отрицательной логики

- •3. Комбинационные законы

- •A. Закон тавтологии (многократное повторение)

- •B. Закон переместительности

- •Совершенная дизъюктивная нормальная форма (сднф)

- •Совершенная конъюктивная нормальная форма (скнф)

- •Глава 3 Дешифраторы (декодеры)

- •Десятичный дешифратор (декодер)

- •Семисегментный дешифратор

- •Глава 4 Шифраторы (кодеры)

- •Глава 5 Мультиплексоры

- •Особенности построения мультиплексоров на ттл элементах

- •Особенности построения мультиплексоров на кмоп элементах

- •Глава 6 Демультиплексоры

- •Раздел 5 Генераторы

- •Глава 1

- •Генераторы периодических сигналов

- •Усилительные параметры кмоп инвертора

- •Глава 2 Осцилляторные схемы генераторов

- •Глава 3 Мультивибраторы

- •Глава 4 Особенности кварцевой стабилизации частоты цифровых генераторов

- •Глава 5 Одновибраторы (ждущие мультивибраторы)

- •Укорачивающие одновибраторы

- •Расширяющие одновибраторы (ждущие мультивибраторы)

- •Раздел 6 Последовательностные устройства (цифровые устройства с памятью)

- •Глава 1

- •Триггеры

- •Глава 2 rs триггер

- •Синхронный rs триггер

- •Глава 3 d триггеры, работающие по потенциалу (статические d триггеры)

- •Глава 4 Явление метастабильности

- •Глава 5 d триггеры, работающие по фронту (динамические d триггеры)

- •Глава 6 t триггеры

- •Глава 7 jk триггер

- •Глава 8 Регистры

- •Параллельные регистры

- •Глава 9 Последовательные (сдвиговые) регистры

- •Глава 10 Универсальные регистры

- •Глава 11 Счётчики

- •Двоичные асинхронные счётчики

- •Двоичные вычитающие асинхронные счётчики

- •Глава 12 Недвоичные счётчики с обратной связью

- •Глава 13 Недвоичные счётчики с предварительной записью

- •Глава 14 Синхронные счётчики

- •Глава 15 Синхронные двоичные счётчики

- •Раздел 7

- •Современные виды цифровых микросхем.

- •Глава 1

- •Микросхемы малой степени интеграции (малая логика)

- •Глава 2 Программируемые логические интегральные схемы (плис).

- •Классификация плис

- •Глава 3 Программируемые логические матрицы.

- •Глава 4 Программируемые матрицы логики (pal).

- •Глава 5 Сложные программируемые логические устройства (cpld).

- •Внутреннее устройство cpld

- •Разработка цифровых устройств на cpld

- •Глава 6 Программируемые пользователем вентильные матрицы (fpga).

- •Раздел 8

- •Индикаторы.

- •Глава 1

- •Виды индикаторов.

- •Малогабаритные лампочки накаливания

- •Расчет транзисторного ключа

- •Глава 2 Газоразрядные индикаторы.

- •Глава 3 Светодиодные индикаторы.

- •Глава 4 Жидкокристаллические индикаторы.

- •Принципы работы жидкокристаллических индикаторов

- •Режимы работы жидкокристаллических индикаторов

- •Параметры жидкокристаллических индикаторов

- •Формирование цветного изображения

- •Формирование напряжения для работы жидкокристаллического индикатора

- •Глава 5 Динамическая индикация.

- •Раздел 9

- •Синтезаторы частоты.

- •Глава 1

- •Цифровой фазовый детектор.

- •Глава 2 Фазовый компаратор.

- •Глава 3 Цепи фазовой автоподстройки частоты.

- •Глава 4 Умножители частоты

- •Глава 5 Частотный детектор, построенный на основе фапч

- •Раздел 10

- •Особенности аналого-цифрового и цифро-аналогового преобразования.

- •Глава 1

- •Квантование аналогового сигнала по времени

- •Глава 2 Погрешности дискретизатора

- •Погрешность хранения

- •Погрешность выборки

- •Глава 3 Фильтры устранения эффекта наложения спектров (Антиалайзинговые фильтры)

- •Глава 4 Дискретизация сигнала на промежуточной частоте (субдискретизация)

- •Глава 5 Параллельные ацп (flash adc)

- •Глава 6 Последовательно-параллельные ацп

- •Глава 7 ацп последовательного приближения (sar adc)

- •Глава 8 Сигма-дельта ацп

- •Глава 9 Цифроаналоговые преобразователи (цап) с суммированием токов

- •Глава 10 Цифроаналоговые преобразователи r-2r

- •Раздел 11

- •11.1 Основные блоки цифровой обработки сигналов

- •Глава 1 Двоичные сумматоры

- •Глава 2 Умножители

- •Глава 3 Постоянные запоминающие устройства.

- •Глава 4 Цифровые фильтры.

- •11.2 Микросхемы прямого цифрового синтеза радиосигналов.

- •Глава 5 Фазовые аккумуляторы

- •Глава 6 Полярные модуляторы

- •Глава 7 Квадратурные модуляторы.

- •Глава 8 Интерполирующие цифровые фильтры.

- •Глава 9 Однородные интерполирующие цифровые фильтры.

- •Микросхемы цифрового приема радиосигналов

- •Глава 10 Квадратурные демодуляторы.

- •Глава 11 Децимирующие цифровые фильтры.

- •Децимирующий фильтр с конечной импульсной характеристикой

- •Глава 12 Однородные децимирующие цифровые фильтры.

- •Раздел 12 Примеры реализации цифровых устройств

- •12.1 Электронные часы

- •Разработка структурной схемы

- •Глава 2 Разработка принципиальной схемы

- •Глава 3 Разработка принципиальной схемы индикации часов

- •12.2 Последовательные порты

- •Глава 4

- •Глава 5

Глава 4 Умножители частоты

Цепи фазовой подстройки частоты часто используются для умножения частоты. Раньше для этой цели использовались схемы генераторов гармоник с последующим выделением соответствующей гармоники узкополосным фильтром.

Намного лучше для этой цели подходит схема фазовой автоподстройки частоты. В этой схеме относительно просто можно изменять коэффициент умножения схемы изменением коэффициента деления в цепи обратной связи. Для умножения частоты используется либо цифровая, либо полностью цифровая схема фазовой автоподстройки частоты.

Умножители частоты в настоящее время обычно используются для увеличения внутренней тактовой частоты больших интегральных микросхем. В этих микросхемах цифровая схема фазовой автоподстройки частоты получила название аналогового умножителя тактовой частоты, а полностью цифровая схема ФАПЧ получила название цифрового умножителя частоты.

Для увеличения тактовой частоты цифровых микросхем чаще используется полностью цифровая схема умножения частоты, а для смешанных схем или схем, предназначенных для цифровой обработки сигналов предпочтительнее использование аналогового умножителя частоты. Это связано со спектральной чистотой выходного сигнала. Аналоговая схема обеспечивает более стабильное колебание, но при этом медленнее выходит на рабочий режим.

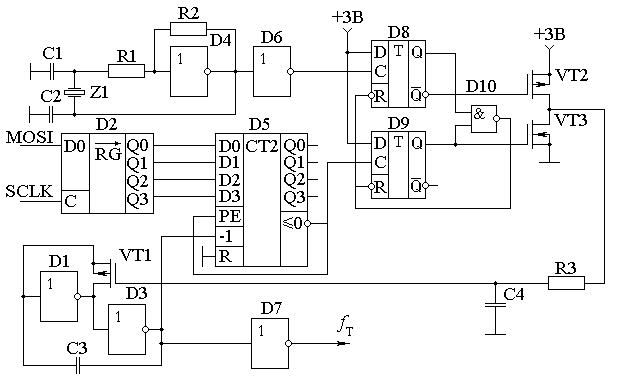

Пример принципиальной схемы аналогового умножителя тактовой частоты приведен на рисунке 4.1.

Рисунок 4.1. Принципиальная схема аналогового умножителя частоты.

В этой схеме опорный генератор с кварцевой стабилизацией частоты реализован на логических элементах D4 и D6. Генератор, управляемый напряжением, реализован на элементах D1 и D3. В качестве регулировочного элемента использован полевой транзистор VT1. Фазовый компаратор реализован на микросхемах D7, D8 и D10. Полосу захвата цепи фазовой автоподстройки определяет фильтр низкой частоты, реализованный на конденсаторе C4.

Данный умножитель частоты допускает только шестнадцать ступеней регулировки тактовой частоты. Код, определяющий коэффициент умножения вводится через упрощенный последовательный порт, собранный на сдвиговом регистре D2.

В более сложных схемах умножителей частоты вводятся делители между опорным генератором и фазовым компаратором. Это позволяет реализовывать дробные коэффициенты умножения частоты.

Глава 5 Частотный детектор, построенный на основе фапч

Частотные детекторы, построенные на основе элементов задержки, обычно реализуют широкую полосу детекторной характеристики. Однако используемые в реальных радиосистемах частотно-модулированные колебания обычно являются узкополосными. Поэтому для приема частотно-модулированных радиосигналов чаще используют частотные детекторы, построенные на основе схемы фазовой автоподстройки частоты.

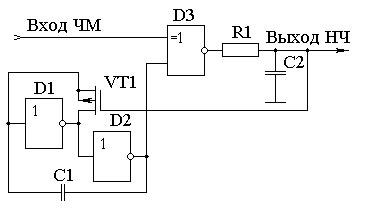

В схеме частотного детектора не используется фазовый компаратор. Здесь лучше подходит схема фазового детектора, так как на ее выходе сигнал пропорционален фазе принимаемого колебания. Пример схемы частотного детектора, построенного на основе схемы фазовой автоподстройки частоты, приведен на рисунке 5.1.

Рисунок

5.1. Пример схемы частотного детектора,

построенного на основе схемы фазовой

автоподстройки частоты

Рисунок

5.1. Пример схемы частотного детектора,

построенного на основе схемы фазовой

автоподстройки частоты

В данной схеме частотный детектор реализован на основе цифрового фазового детектора. Как мы уже определили ранее, функции фазового детектора может выполнять логический элемент "исключающее ИЛИ". Генератор управляемый напряжением собран на инверторах D1 и D2, а подстройку его частоты осуществляет транзистор VT1.

При изменении частоты входного сигнала схема фазовой автоподстройки вынуждена подстраивать ГУН на эту же частоту. При этом естественно изменяется напряжение на затворе транзистора VT1. То есть напряжение в этой точке будет соответствовать отклонению частоты входного сигнала от своего номинального значения, а значит, вся схема в целом будет осуществлять детектирование частотно-модулированного сигнала.

Полоса детектируемого сигнала в приведенной схеме будет зависеть от крутизны регулировочной характеристики генератора, управляемого напряжением и коэффициента усиления фазового детектора, выполненного на логическом элементе D3.