- •Глава1 Что такое цифровые микросхемы. Виды цифровых микросхем

- •Глава 2 Области применения цифровых микросхем

- •Глава 3 Условные графические изображения цифровых микросхем (гост)

- •Параметры цифровых микросхем

- •Уровни логического нуля и единицы

- •Входные и выходные токи цифровых микросхем

- •Параметры, определяющие быстродействие цифровых микросхем

- •Описание логической функции цифровых схем

- •Раздел 2

- •Логический элемент "и"

- •Логический элемент "или"

- •Глава 2 Диодно-транзисторная логика (дтл)

- •Глава 3 Транзисторно-транзисторная логика (ттл)

- •Логические уровни ттл микросхем

- •Семейства ттл микросхем

- •Глава 4 Цифровые логические микросхемы, выполненные на комплементарных моп транзисторах (кмоп) Логические кмоп (кмдп) инверторы

- •Логические кмоп (кмдп) элементы "и"

- •Логические кмоп (кмдп) элементы "или"

- •Особенности применения кмоп микросхем

- •Логические уровни кмоп микросхем

- •Семейства кмоп микросхем

- •Глава 5 Согласование цифровых микросхем различных серий между

- •Согласование микросхем из различных серий между собой

- •Согласование по току

- •Согласование микросхем с различным напряжением питания

- •Глава 6 Регенерация цифрового сигнала (Триггер Шмитта)

- •Раздел 3 Арифметические основы цифровой техники.

- •Глава 1

- •Арифметические основы цифровой техники

- •Системы счисления

- •Десятичная система счисления

- •Двоичная система счисления

- •Восьмеричная система счисления

- •Шестнадцатеричная система счисления

- •Глава 2 Преобразование чисел из одной системы счисления в другую

- •Преобразование целых чисел

- •Глава 3 Преобразование дробной части числа

- •Раздел 4

- •2. Законы отрицания a. Закон дополнительных элементов

- •B. Двойное отрицание

- •C. Закон отрицательной логики

- •3. Комбинационные законы

- •A. Закон тавтологии (многократное повторение)

- •B. Закон переместительности

- •Совершенная дизъюктивная нормальная форма (сднф)

- •Совершенная конъюктивная нормальная форма (скнф)

- •Глава 3 Дешифраторы (декодеры)

- •Десятичный дешифратор (декодер)

- •Семисегментный дешифратор

- •Глава 4 Шифраторы (кодеры)

- •Глава 5 Мультиплексоры

- •Особенности построения мультиплексоров на ттл элементах

- •Особенности построения мультиплексоров на кмоп элементах

- •Глава 6 Демультиплексоры

- •Раздел 5 Генераторы

- •Глава 1

- •Генераторы периодических сигналов

- •Усилительные параметры кмоп инвертора

- •Глава 2 Осцилляторные схемы генераторов

- •Глава 3 Мультивибраторы

- •Глава 4 Особенности кварцевой стабилизации частоты цифровых генераторов

- •Глава 5 Одновибраторы (ждущие мультивибраторы)

- •Укорачивающие одновибраторы

- •Расширяющие одновибраторы (ждущие мультивибраторы)

- •Раздел 6 Последовательностные устройства (цифровые устройства с памятью)

- •Глава 1

- •Триггеры

- •Глава 2 rs триггер

- •Синхронный rs триггер

- •Глава 3 d триггеры, работающие по потенциалу (статические d триггеры)

- •Глава 4 Явление метастабильности

- •Глава 5 d триггеры, работающие по фронту (динамические d триггеры)

- •Глава 6 t триггеры

- •Глава 7 jk триггер

- •Глава 8 Регистры

- •Параллельные регистры

- •Глава 9 Последовательные (сдвиговые) регистры

- •Глава 10 Универсальные регистры

- •Глава 11 Счётчики

- •Двоичные асинхронные счётчики

- •Двоичные вычитающие асинхронные счётчики

- •Глава 12 Недвоичные счётчики с обратной связью

- •Глава 13 Недвоичные счётчики с предварительной записью

- •Глава 14 Синхронные счётчики

- •Глава 15 Синхронные двоичные счётчики

- •Раздел 7

- •Современные виды цифровых микросхем.

- •Глава 1

- •Микросхемы малой степени интеграции (малая логика)

- •Глава 2 Программируемые логические интегральные схемы (плис).

- •Классификация плис

- •Глава 3 Программируемые логические матрицы.

- •Глава 4 Программируемые матрицы логики (pal).

- •Глава 5 Сложные программируемые логические устройства (cpld).

- •Внутреннее устройство cpld

- •Разработка цифровых устройств на cpld

- •Глава 6 Программируемые пользователем вентильные матрицы (fpga).

- •Раздел 8

- •Индикаторы.

- •Глава 1

- •Виды индикаторов.

- •Малогабаритные лампочки накаливания

- •Расчет транзисторного ключа

- •Глава 2 Газоразрядные индикаторы.

- •Глава 3 Светодиодные индикаторы.

- •Глава 4 Жидкокристаллические индикаторы.

- •Принципы работы жидкокристаллических индикаторов

- •Режимы работы жидкокристаллических индикаторов

- •Параметры жидкокристаллических индикаторов

- •Формирование цветного изображения

- •Формирование напряжения для работы жидкокристаллического индикатора

- •Глава 5 Динамическая индикация.

- •Раздел 9

- •Синтезаторы частоты.

- •Глава 1

- •Цифровой фазовый детектор.

- •Глава 2 Фазовый компаратор.

- •Глава 3 Цепи фазовой автоподстройки частоты.

- •Глава 4 Умножители частоты

- •Глава 5 Частотный детектор, построенный на основе фапч

- •Раздел 10

- •Особенности аналого-цифрового и цифро-аналогового преобразования.

- •Глава 1

- •Квантование аналогового сигнала по времени

- •Глава 2 Погрешности дискретизатора

- •Погрешность хранения

- •Погрешность выборки

- •Глава 3 Фильтры устранения эффекта наложения спектров (Антиалайзинговые фильтры)

- •Глава 4 Дискретизация сигнала на промежуточной частоте (субдискретизация)

- •Глава 5 Параллельные ацп (flash adc)

- •Глава 6 Последовательно-параллельные ацп

- •Глава 7 ацп последовательного приближения (sar adc)

- •Глава 8 Сигма-дельта ацп

- •Глава 9 Цифроаналоговые преобразователи (цап) с суммированием токов

- •Глава 10 Цифроаналоговые преобразователи r-2r

- •Раздел 11

- •11.1 Основные блоки цифровой обработки сигналов

- •Глава 1 Двоичные сумматоры

- •Глава 2 Умножители

- •Глава 3 Постоянные запоминающие устройства.

- •Глава 4 Цифровые фильтры.

- •11.2 Микросхемы прямого цифрового синтеза радиосигналов.

- •Глава 5 Фазовые аккумуляторы

- •Глава 6 Полярные модуляторы

- •Глава 7 Квадратурные модуляторы.

- •Глава 8 Интерполирующие цифровые фильтры.

- •Глава 9 Однородные интерполирующие цифровые фильтры.

- •Микросхемы цифрового приема радиосигналов

- •Глава 10 Квадратурные демодуляторы.

- •Глава 11 Децимирующие цифровые фильтры.

- •Децимирующий фильтр с конечной импульсной характеристикой

- •Глава 12 Однородные децимирующие цифровые фильтры.

- •Раздел 12 Примеры реализации цифровых устройств

- •12.1 Электронные часы

- •Разработка структурной схемы

- •Глава 2 Разработка принципиальной схемы

- •Глава 3 Разработка принципиальной схемы индикации часов

- •12.2 Последовательные порты

- •Глава 4

- •Глава 5

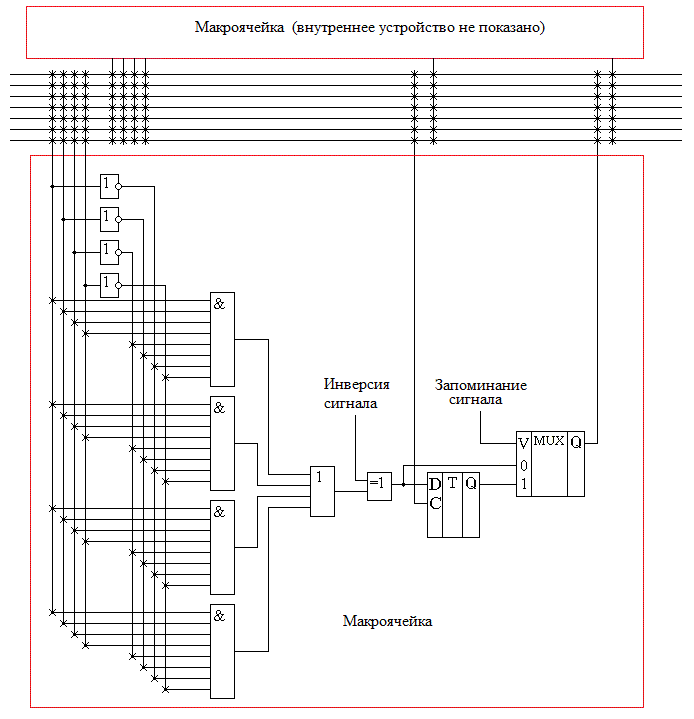

Внутреннее устройство cpld

Программируемая логическая интегральная схема CPLD состоит из нескольких макроячеек, расположенных на одном кристалле. Каждая макроячейка соединена с блоками ввода-вывода, осуществляющими формирование необходимого вида входов или выходов для работы с внешними схемами. Кроме того, все макроячейки и блоки ввода-вывода связаны между собой внутренними параллельными шинами. Пример внутренней схемы CPLD приведен на рисунке 5.1.

Рисунок 5.1.

Пример внутренней схемы CPLD

Рисунок 5.1.

Пример внутренней схемы CPLD

Приведенная на рисунке 5.1 микросхема CPLD состоит из четырех макроячеек, которые связаны между собой внутренними шинами и соединяются с блоками ввода-вывода. Макроячейка построена подобно ПЛМ микросхеме, к которой на выходе подключен D-триггер. На рисунке 5.2 приведен пример внутренней схемы макроячейки и ее подключение к шине межсоединений.

Рисунок 5.2.

Внутренняя схема макроячейки микросхемы

CPLD

Рисунок 5.2.

Внутренняя схема макроячейки микросхемы

CPLD

В состав приведенной на рисунке 5.2 макроячейки входят четыре шестивходовых логических элемента "6-И" и 4-входовый логический элемент "4-ИЛИ". Его выход соединен со входом логического элемента "ИСКЛЮЧАЮЩЕЕ ИЛИ". Этот логический элемент предназначен для реализации инверсии логической функции, реализованной ПЛМ-подобной схемой макроячейки. Для этого на его второй вход может подаваться логический ноль или логическая единица. Если этот вход запрограммирован на подачу логической единицы, то логический элемент "ИСКЛЮЧАЮЩЕЕ ИЛИ" будет инвертировать значение, поступающее с выхода логического элемента "4-ИЛИ". Если же на него поступает логический ноль, то схема "ИСКЛЮЧАЮЩЕЕ ИЛИ" будет передавать на выход сигнал без изменения.

На выходе макроячейки поставлен двухвходовый мультиплексор, который позволяет передавать на выход текущее значение сигнала с выхода ПЛМ-схемы, или сохраненное в D-триггере.

Блок ввода-вывода состоит из элементов с тремя состояниями (буферов). Буфер позволяет настраивать выводы микросхемы на ввод или и на вывод сигналов. Чтобы вывод микросхемы настроить на ввод информации, достаточно перевести буфер, подключенный к данному выводу, в высокоимпедансное состояние. Дальнейший путь прохождения сигнала по микросхеме может быть запрограммирован МОП-ключами, размещенными на пересечениях вертикальных проводников и горизонтальных проводников шинымежсоединений. На схеме это соединение помечается символом 'x'. Необходимо отметить, что если вывод запрограммирован на прием информации, то он не может быть использован в качестве выхода микросхемы. Обычно фирмы-изготовители указывают максимально возможное число входных и выходных линий.

Разработка цифровых устройств на cpld

Разработка цифровых устройств на программируемых логических интегральных схемах CPLD практически не отличается от разработки обычных цифровых устройств. Для этого не требуется разбираться в особенностях внутренней структуры микросхемы или проектировать матрицу межсоединений. Разработчики ПЛИС предоставляют пакет САПР в составе которого можно вести разработку цифрового устройства в виде обычных схем в схемном редакторе, а затем транслировать эту схему в файл коммутаций внутренней матрицы межсоединений CPLD. Этот файл загружается в ПЗУ микросхемы CPLD и микросхема превращается в разработанное нами цифровое устройство, фактически в заказную СБИС.

В настоящее время разработка цифровых устройств чаще ведется с применением языков программирования схем, таких как AHDL или VHDL. Применение языков программирования вместо примитивов, являющихся аналогами микросхем средней интеграции, позволяет значительно оптимизировать внутреннюю структуру прошивки микросхемы.

В качестве примера системы автоматизированного проектирования (САПР) программируемых логических интегральных схем можно привести пакет Quartus II, предлагаемый фирмой Alterra. С работой программного пакета Quartus II можно познакомиться в лабораторной работе 1 " Исследование цифровых устройств на основе программируемых логических интегральных схем (ПЛИС) в среде Quartus II"