- •Глава1 Что такое цифровые микросхемы. Виды цифровых микросхем

- •Глава 2 Области применения цифровых микросхем

- •Глава 3 Условные графические изображения цифровых микросхем (гост)

- •Параметры цифровых микросхем

- •Уровни логического нуля и единицы

- •Входные и выходные токи цифровых микросхем

- •Параметры, определяющие быстродействие цифровых микросхем

- •Описание логической функции цифровых схем

- •Раздел 2

- •Логический элемент "и"

- •Логический элемент "или"

- •Глава 2 Диодно-транзисторная логика (дтл)

- •Глава 3 Транзисторно-транзисторная логика (ттл)

- •Логические уровни ттл микросхем

- •Семейства ттл микросхем

- •Глава 4 Цифровые логические микросхемы, выполненные на комплементарных моп транзисторах (кмоп) Логические кмоп (кмдп) инверторы

- •Логические кмоп (кмдп) элементы "и"

- •Логические кмоп (кмдп) элементы "или"

- •Особенности применения кмоп микросхем

- •Логические уровни кмоп микросхем

- •Семейства кмоп микросхем

- •Глава 5 Согласование цифровых микросхем различных серий между

- •Согласование микросхем из различных серий между собой

- •Согласование по току

- •Согласование микросхем с различным напряжением питания

- •Глава 6 Регенерация цифрового сигнала (Триггер Шмитта)

- •Раздел 3 Арифметические основы цифровой техники.

- •Глава 1

- •Арифметические основы цифровой техники

- •Системы счисления

- •Десятичная система счисления

- •Двоичная система счисления

- •Восьмеричная система счисления

- •Шестнадцатеричная система счисления

- •Глава 2 Преобразование чисел из одной системы счисления в другую

- •Преобразование целых чисел

- •Глава 3 Преобразование дробной части числа

- •Раздел 4

- •2. Законы отрицания a. Закон дополнительных элементов

- •B. Двойное отрицание

- •C. Закон отрицательной логики

- •3. Комбинационные законы

- •A. Закон тавтологии (многократное повторение)

- •B. Закон переместительности

- •Совершенная дизъюктивная нормальная форма (сднф)

- •Совершенная конъюктивная нормальная форма (скнф)

- •Глава 3 Дешифраторы (декодеры)

- •Десятичный дешифратор (декодер)

- •Семисегментный дешифратор

- •Глава 4 Шифраторы (кодеры)

- •Глава 5 Мультиплексоры

- •Особенности построения мультиплексоров на ттл элементах

- •Особенности построения мультиплексоров на кмоп элементах

- •Глава 6 Демультиплексоры

- •Раздел 5 Генераторы

- •Глава 1

- •Генераторы периодических сигналов

- •Усилительные параметры кмоп инвертора

- •Глава 2 Осцилляторные схемы генераторов

- •Глава 3 Мультивибраторы

- •Глава 4 Особенности кварцевой стабилизации частоты цифровых генераторов

- •Глава 5 Одновибраторы (ждущие мультивибраторы)

- •Укорачивающие одновибраторы

- •Расширяющие одновибраторы (ждущие мультивибраторы)

- •Раздел 6 Последовательностные устройства (цифровые устройства с памятью)

- •Глава 1

- •Триггеры

- •Глава 2 rs триггер

- •Синхронный rs триггер

- •Глава 3 d триггеры, работающие по потенциалу (статические d триггеры)

- •Глава 4 Явление метастабильности

- •Глава 5 d триггеры, работающие по фронту (динамические d триггеры)

- •Глава 6 t триггеры

- •Глава 7 jk триггер

- •Глава 8 Регистры

- •Параллельные регистры

- •Глава 9 Последовательные (сдвиговые) регистры

- •Глава 10 Универсальные регистры

- •Глава 11 Счётчики

- •Двоичные асинхронные счётчики

- •Двоичные вычитающие асинхронные счётчики

- •Глава 12 Недвоичные счётчики с обратной связью

- •Глава 13 Недвоичные счётчики с предварительной записью

- •Глава 14 Синхронные счётчики

- •Глава 15 Синхронные двоичные счётчики

- •Раздел 7

- •Современные виды цифровых микросхем.

- •Глава 1

- •Микросхемы малой степени интеграции (малая логика)

- •Глава 2 Программируемые логические интегральные схемы (плис).

- •Классификация плис

- •Глава 3 Программируемые логические матрицы.

- •Глава 4 Программируемые матрицы логики (pal).

- •Глава 5 Сложные программируемые логические устройства (cpld).

- •Внутреннее устройство cpld

- •Разработка цифровых устройств на cpld

- •Глава 6 Программируемые пользователем вентильные матрицы (fpga).

- •Раздел 8

- •Индикаторы.

- •Глава 1

- •Виды индикаторов.

- •Малогабаритные лампочки накаливания

- •Расчет транзисторного ключа

- •Глава 2 Газоразрядные индикаторы.

- •Глава 3 Светодиодные индикаторы.

- •Глава 4 Жидкокристаллические индикаторы.

- •Принципы работы жидкокристаллических индикаторов

- •Режимы работы жидкокристаллических индикаторов

- •Параметры жидкокристаллических индикаторов

- •Формирование цветного изображения

- •Формирование напряжения для работы жидкокристаллического индикатора

- •Глава 5 Динамическая индикация.

- •Раздел 9

- •Синтезаторы частоты.

- •Глава 1

- •Цифровой фазовый детектор.

- •Глава 2 Фазовый компаратор.

- •Глава 3 Цепи фазовой автоподстройки частоты.

- •Глава 4 Умножители частоты

- •Глава 5 Частотный детектор, построенный на основе фапч

- •Раздел 10

- •Особенности аналого-цифрового и цифро-аналогового преобразования.

- •Глава 1

- •Квантование аналогового сигнала по времени

- •Глава 2 Погрешности дискретизатора

- •Погрешность хранения

- •Погрешность выборки

- •Глава 3 Фильтры устранения эффекта наложения спектров (Антиалайзинговые фильтры)

- •Глава 4 Дискретизация сигнала на промежуточной частоте (субдискретизация)

- •Глава 5 Параллельные ацп (flash adc)

- •Глава 6 Последовательно-параллельные ацп

- •Глава 7 ацп последовательного приближения (sar adc)

- •Глава 8 Сигма-дельта ацп

- •Глава 9 Цифроаналоговые преобразователи (цап) с суммированием токов

- •Глава 10 Цифроаналоговые преобразователи r-2r

- •Раздел 11

- •11.1 Основные блоки цифровой обработки сигналов

- •Глава 1 Двоичные сумматоры

- •Глава 2 Умножители

- •Глава 3 Постоянные запоминающие устройства.

- •Глава 4 Цифровые фильтры.

- •11.2 Микросхемы прямого цифрового синтеза радиосигналов.

- •Глава 5 Фазовые аккумуляторы

- •Глава 6 Полярные модуляторы

- •Глава 7 Квадратурные модуляторы.

- •Глава 8 Интерполирующие цифровые фильтры.

- •Глава 9 Однородные интерполирующие цифровые фильтры.

- •Микросхемы цифрового приема радиосигналов

- •Глава 10 Квадратурные демодуляторы.

- •Глава 11 Децимирующие цифровые фильтры.

- •Децимирующий фильтр с конечной импульсной характеристикой

- •Глава 12 Однородные децимирующие цифровые фильтры.

- •Раздел 12 Примеры реализации цифровых устройств

- •12.1 Электронные часы

- •Разработка структурной схемы

- •Глава 2 Разработка принципиальной схемы

- •Глава 3 Разработка принципиальной схемы индикации часов

- •12.2 Последовательные порты

- •Глава 4

- •Глава 5

Глава 14 Синхронные счётчики

В рассмотренных схемах делителей частоты быстродействие всей схемы определяется временем распространения сигнала от входа до выхода самого старшего разряда. При этом получается, что чем больше требуемый коэффициент деления, тем больше двоичных разрядов счётчика требуется для реализации этого делителя. Тем большее время требуется для распространения сигнала от входа синхронизации счётчика, до его выхода, и тем меньше будет предельная частота, которую можно подавать на вход этого делителя.

Можно ли обойти такую неприятную особенность недвоичных счётчиков? Да можно! Нужно, чтобы счётчик подготавливал своё новое состояние в промежутках между тактовыми импульсами и только записывал его по приходу нового импульса.

Первая схема, которую мы рассмотрим - это схема кольцевого счётчика. Такой счётчик можно построить на основе сдвигового регистра. Схема кольцевого счётчика приведена на рисунке 14.1.

Рисунок 14.1. Схема кольцевого счетчика.

Рассмотрим работу этой схемы. Пусть первоначально в счетчике записано число 002. После первого же тактового импульса состояние счётчика станет равным 102, после второго - 112. Временные диаграммы этой схемы приведены на рисунке 14.2.

В результате анализа временных диаграмм можно определить, что коэффициент деления схемы кольцевого счётчика будет равен:

Кд = 2*n.

В качестве преимущества схемы кольцевого счётчика можно отметить то, что её быстродействие зависит только от времени задержки одного триггера. Это означает, что на кольцевых счётчиках можно реализовывать самые быстродействующие делители частоты.

То, что коэффициент деления пропорционален не степени количества триггеров, а только сумме является недостатком данной схемы. Это означает, что при увеличении коэффициента деления сложность схемы неоправданно возрастает по сравнению со схемой двоичного счётчика. Ещё одним недостатком схемы является то, что в результате воздействия помехи в регистр может быт записано число 012. В результате коэффициент деления схемы изменится, а это является недопустимым.

Ещё одним недостатком схемы кольцевого счётчика является то, что при количестве триггеров большем трёх, в результате воздействия помехи в регистр может быт записано число, содержащее несколько единиц. В результате коэффициент деления схемы изменится, а это является недопустимым. Временные диаграммы сигналов на входе и выходах 3-разрядного кольцевого счётчика при правильной и ошибочной работе приведены на рисунке 14.3.

а)

б)

Рисунок 14.3. Временные диаграммы сигналов 3-разрядного кольцевого синхронного счётчика при правильной (а) и ошибочной (б) работе.

Для того чтобы избежать неправильной работы счётчика в этот счётчик можно ввести схему контроля правильной работы. В простейшем случае это может быть обычный логический элемент “И-НЕ”. Этот элемент будет контролировать состояние счётчика, соответствующее единицам во всех его разрядах. Схема 2-разрядного счётчика со схемой проверки правильности его работы приведена на рисунке 14.4.

Рисунок 14.4. Схема 2-разрядного счетчика с проверкой правильности его работы.

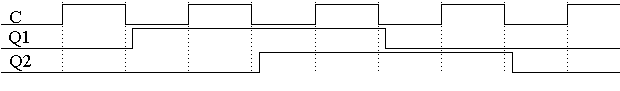

В этой схеме триггеры счётчика при поступлении импульсов на тактовый вход последовательно заполняются единицами. Как только все триггеры будут заполнены единицами, на выходе логического элемента “2И-НЕ” появится уровень логического нуля. При поступлении следующего тактового импульса этот ноль будет записан в первый триггер счётчика. В дальнейшем работа счётчика повторяется. Временные диаграммы сигналов на выходах этого счётчика приведены на рисунке 14.5.

Рисунок 14.5. Временные диаграммы сигналов на выходах 2-разрядного счетчика счётчика с проверкой правильности его работы.