- •Глава1 Что такое цифровые микросхемы. Виды цифровых микросхем

- •Глава 2 Области применения цифровых микросхем

- •Глава 3 Условные графические изображения цифровых микросхем (гост)

- •Параметры цифровых микросхем

- •Уровни логического нуля и единицы

- •Входные и выходные токи цифровых микросхем

- •Параметры, определяющие быстродействие цифровых микросхем

- •Описание логической функции цифровых схем

- •Раздел 2

- •Логический элемент "и"

- •Логический элемент "или"

- •Глава 2 Диодно-транзисторная логика (дтл)

- •Глава 3 Транзисторно-транзисторная логика (ттл)

- •Логические уровни ттл микросхем

- •Семейства ттл микросхем

- •Глава 4 Цифровые логические микросхемы, выполненные на комплементарных моп транзисторах (кмоп) Логические кмоп (кмдп) инверторы

- •Логические кмоп (кмдп) элементы "и"

- •Логические кмоп (кмдп) элементы "или"

- •Особенности применения кмоп микросхем

- •Логические уровни кмоп микросхем

- •Семейства кмоп микросхем

- •Глава 5 Согласование цифровых микросхем различных серий между

- •Согласование микросхем из различных серий между собой

- •Согласование по току

- •Согласование микросхем с различным напряжением питания

- •Глава 6 Регенерация цифрового сигнала (Триггер Шмитта)

- •Раздел 3 Арифметические основы цифровой техники.

- •Глава 1

- •Арифметические основы цифровой техники

- •Системы счисления

- •Десятичная система счисления

- •Двоичная система счисления

- •Восьмеричная система счисления

- •Шестнадцатеричная система счисления

- •Глава 2 Преобразование чисел из одной системы счисления в другую

- •Преобразование целых чисел

- •Глава 3 Преобразование дробной части числа

- •Раздел 4

- •2. Законы отрицания a. Закон дополнительных элементов

- •B. Двойное отрицание

- •C. Закон отрицательной логики

- •3. Комбинационные законы

- •A. Закон тавтологии (многократное повторение)

- •B. Закон переместительности

- •Совершенная дизъюктивная нормальная форма (сднф)

- •Совершенная конъюктивная нормальная форма (скнф)

- •Глава 3 Дешифраторы (декодеры)

- •Десятичный дешифратор (декодер)

- •Семисегментный дешифратор

- •Глава 4 Шифраторы (кодеры)

- •Глава 5 Мультиплексоры

- •Особенности построения мультиплексоров на ттл элементах

- •Особенности построения мультиплексоров на кмоп элементах

- •Глава 6 Демультиплексоры

- •Раздел 5 Генераторы

- •Глава 1

- •Генераторы периодических сигналов

- •Усилительные параметры кмоп инвертора

- •Глава 2 Осцилляторные схемы генераторов

- •Глава 3 Мультивибраторы

- •Глава 4 Особенности кварцевой стабилизации частоты цифровых генераторов

- •Глава 5 Одновибраторы (ждущие мультивибраторы)

- •Укорачивающие одновибраторы

- •Расширяющие одновибраторы (ждущие мультивибраторы)

- •Раздел 6 Последовательностные устройства (цифровые устройства с памятью)

- •Глава 1

- •Триггеры

- •Глава 2 rs триггер

- •Синхронный rs триггер

- •Глава 3 d триггеры, работающие по потенциалу (статические d триггеры)

- •Глава 4 Явление метастабильности

- •Глава 5 d триггеры, работающие по фронту (динамические d триггеры)

- •Глава 6 t триггеры

- •Глава 7 jk триггер

- •Глава 8 Регистры

- •Параллельные регистры

- •Глава 9 Последовательные (сдвиговые) регистры

- •Глава 10 Универсальные регистры

- •Глава 11 Счётчики

- •Двоичные асинхронные счётчики

- •Двоичные вычитающие асинхронные счётчики

- •Глава 12 Недвоичные счётчики с обратной связью

- •Глава 13 Недвоичные счётчики с предварительной записью

- •Глава 14 Синхронные счётчики

- •Глава 15 Синхронные двоичные счётчики

- •Раздел 7

- •Современные виды цифровых микросхем.

- •Глава 1

- •Микросхемы малой степени интеграции (малая логика)

- •Глава 2 Программируемые логические интегральные схемы (плис).

- •Классификация плис

- •Глава 3 Программируемые логические матрицы.

- •Глава 4 Программируемые матрицы логики (pal).

- •Глава 5 Сложные программируемые логические устройства (cpld).

- •Внутреннее устройство cpld

- •Разработка цифровых устройств на cpld

- •Глава 6 Программируемые пользователем вентильные матрицы (fpga).

- •Раздел 8

- •Индикаторы.

- •Глава 1

- •Виды индикаторов.

- •Малогабаритные лампочки накаливания

- •Расчет транзисторного ключа

- •Глава 2 Газоразрядные индикаторы.

- •Глава 3 Светодиодные индикаторы.

- •Глава 4 Жидкокристаллические индикаторы.

- •Принципы работы жидкокристаллических индикаторов

- •Режимы работы жидкокристаллических индикаторов

- •Параметры жидкокристаллических индикаторов

- •Формирование цветного изображения

- •Формирование напряжения для работы жидкокристаллического индикатора

- •Глава 5 Динамическая индикация.

- •Раздел 9

- •Синтезаторы частоты.

- •Глава 1

- •Цифровой фазовый детектор.

- •Глава 2 Фазовый компаратор.

- •Глава 3 Цепи фазовой автоподстройки частоты.

- •Глава 4 Умножители частоты

- •Глава 5 Частотный детектор, построенный на основе фапч

- •Раздел 10

- •Особенности аналого-цифрового и цифро-аналогового преобразования.

- •Глава 1

- •Квантование аналогового сигнала по времени

- •Глава 2 Погрешности дискретизатора

- •Погрешность хранения

- •Погрешность выборки

- •Глава 3 Фильтры устранения эффекта наложения спектров (Антиалайзинговые фильтры)

- •Глава 4 Дискретизация сигнала на промежуточной частоте (субдискретизация)

- •Глава 5 Параллельные ацп (flash adc)

- •Глава 6 Последовательно-параллельные ацп

- •Глава 7 ацп последовательного приближения (sar adc)

- •Глава 8 Сигма-дельта ацп

- •Глава 9 Цифроаналоговые преобразователи (цап) с суммированием токов

- •Глава 10 Цифроаналоговые преобразователи r-2r

- •Раздел 11

- •11.1 Основные блоки цифровой обработки сигналов

- •Глава 1 Двоичные сумматоры

- •Глава 2 Умножители

- •Глава 3 Постоянные запоминающие устройства.

- •Глава 4 Цифровые фильтры.

- •11.2 Микросхемы прямого цифрового синтеза радиосигналов.

- •Глава 5 Фазовые аккумуляторы

- •Глава 6 Полярные модуляторы

- •Глава 7 Квадратурные модуляторы.

- •Глава 8 Интерполирующие цифровые фильтры.

- •Глава 9 Однородные интерполирующие цифровые фильтры.

- •Микросхемы цифрового приема радиосигналов

- •Глава 10 Квадратурные демодуляторы.

- •Глава 11 Децимирующие цифровые фильтры.

- •Децимирующий фильтр с конечной импульсной характеристикой

- •Глава 12 Однородные децимирующие цифровые фильтры.

- •Раздел 12 Примеры реализации цифровых устройств

- •12.1 Электронные часы

- •Разработка структурной схемы

- •Глава 2 Разработка принципиальной схемы

- •Глава 3 Разработка принципиальной схемы индикации часов

- •12.2 Последовательные порты

- •Глава 4

- •Глава 5

Глава 8 Регистры

Регистром называется последовательное или параллельное соединение триггеров. Регистры обычно строятся на основе D триггеров. При этом для построения регистров могут использоваться как динамические (flip-flop), так и статические D-триггеры (защелки — lath).

Параллельные регистры

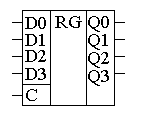

Параллельный регистр служит для запоминания многоразрядного двоичного (или недвоичного) слова. Количество триггеров, входящее в состав параллельного регистра определяет его разрядность. Схема четырёхразрядного параллельного регистра приведена на рисунке 8.1, а его условно-графическое обозначение — на рисунке 8.2.

Рисунок 8.1.

Схема параллельного регистра

Рисунок 8.1.

Схема параллельного регистра

В условно-графическом обозначении возле каждого входа D указывается степень двоичного разряда, который должен быть запомнен в этом триггере регистра. Точно таким же образом обозначаются и выходы регистра. То, что микросхема является регистром, указывается в центральном поле условно-графического обозначения символами RG.

В приведённом на рисунке 8.2 условно-графическом обозначении параллельного регистра инверсные выходы триггеров не показаны. В микросхемах параллельных регистров инверсные выходы триггеров часто не выводятся наружу для экономии количества выводов корпуса.

Рисунок 8.2.

Условно-графическое обозначение

параллельного регистра

Рисунок 8.2.

Условно-графическое обозначение

параллельного регистра

При записи информации в параллельный регистр все биты (двоичные разряды) должны быть записаны одновременно. Поэтому все тактовые входы триггеров, входящих в состав регистра, объединяются параллельно. Для уменьшения входного тока вывода синхронизации C на этом входе в качестве усилителя часто ставится инвертор.

Следует помнить, что назначение разрядов является условным. Если по каким либо причинам (например, с точки зрения разводки печатной платы) удобно изменить нумерацию разрядов, то это можно свободно сделать. При перенумерации входов регистров нужно не забывать, точно таким же образом, изменить номера выходов параллельного регистра.

Для реализации параллельного регистра можно использовать как триггеры с статическим, так и с динамическим входом синхронизации. В переводной литературе при использовании для построения параллельного регистра триггеров-защелок этот регистр, в свою очередь, называют регистром-защелкой.

При использовании регистров со статическим входом тактирования следует соблюдать осторожность, так как при единичном потенциале на входе синхронизации C. сигналы с входов регистра будут свободно проходить на его выходы. В таких случаях обычно используется двухтактная синхронизация, подобная рассмотренной в главе, посвященной использованию одновибраторов.

Промышленностью выпускаются четырёхразрядные и восьмиразрядные микросхемы параллельных регистров. Для построения восьмиразрядных микросхем обычно используются регистры со статическим входом синхронизации. В качестве примера можно назвать микросхемы К580ИР22 и 1533ИР33 (иностранный аналог 74ACT573).

При решении практических задач часто требуется разрядность параллельных регистров большая восьми. В таком случае можно увеличивать разрядность регистров параллельным соединением готовых микросхем. Принципиальная схема параллельного соединения четырёх регистров приведена на рисунке 8.3.

Рисунок 8.3.

Увеличение разрядности параллельного

регистра

Рисунок 8.3.

Увеличение разрядности параллельного

регистра

В настоящее время параллельные регистры обычно являются частью более сложных цифровых устройств, таких как цифровые фильтры, ОЗУ, синтезаторы частот или схемы прямого цифрового синтеза DDS. Подобные схемы не реализуются на микросхемах средней интеграции, а являются частью больших интегральных микросхем (БИС), таких как микропроцессоры, ASIC или FPGA.