- •Глава1 Что такое цифровые микросхемы. Виды цифровых микросхем

- •Глава 2 Области применения цифровых микросхем

- •Глава 3 Условные графические изображения цифровых микросхем (гост)

- •Параметры цифровых микросхем

- •Уровни логического нуля и единицы

- •Входные и выходные токи цифровых микросхем

- •Параметры, определяющие быстродействие цифровых микросхем

- •Описание логической функции цифровых схем

- •Раздел 2

- •Логический элемент "и"

- •Логический элемент "или"

- •Глава 2 Диодно-транзисторная логика (дтл)

- •Глава 3 Транзисторно-транзисторная логика (ттл)

- •Логические уровни ттл микросхем

- •Семейства ттл микросхем

- •Глава 4 Цифровые логические микросхемы, выполненные на комплементарных моп транзисторах (кмоп) Логические кмоп (кмдп) инверторы

- •Логические кмоп (кмдп) элементы "и"

- •Логические кмоп (кмдп) элементы "или"

- •Особенности применения кмоп микросхем

- •Логические уровни кмоп микросхем

- •Семейства кмоп микросхем

- •Глава 5 Согласование цифровых микросхем различных серий между

- •Согласование микросхем из различных серий между собой

- •Согласование по току

- •Согласование микросхем с различным напряжением питания

- •Глава 6 Регенерация цифрового сигнала (Триггер Шмитта)

- •Раздел 3 Арифметические основы цифровой техники.

- •Глава 1

- •Арифметические основы цифровой техники

- •Системы счисления

- •Десятичная система счисления

- •Двоичная система счисления

- •Восьмеричная система счисления

- •Шестнадцатеричная система счисления

- •Глава 2 Преобразование чисел из одной системы счисления в другую

- •Преобразование целых чисел

- •Глава 3 Преобразование дробной части числа

- •Раздел 4

- •2. Законы отрицания a. Закон дополнительных элементов

- •B. Двойное отрицание

- •C. Закон отрицательной логики

- •3. Комбинационные законы

- •A. Закон тавтологии (многократное повторение)

- •B. Закон переместительности

- •Совершенная дизъюктивная нормальная форма (сднф)

- •Совершенная конъюктивная нормальная форма (скнф)

- •Глава 3 Дешифраторы (декодеры)

- •Десятичный дешифратор (декодер)

- •Семисегментный дешифратор

- •Глава 4 Шифраторы (кодеры)

- •Глава 5 Мультиплексоры

- •Особенности построения мультиплексоров на ттл элементах

- •Особенности построения мультиплексоров на кмоп элементах

- •Глава 6 Демультиплексоры

- •Раздел 5 Генераторы

- •Глава 1

- •Генераторы периодических сигналов

- •Усилительные параметры кмоп инвертора

- •Глава 2 Осцилляторные схемы генераторов

- •Глава 3 Мультивибраторы

- •Глава 4 Особенности кварцевой стабилизации частоты цифровых генераторов

- •Глава 5 Одновибраторы (ждущие мультивибраторы)

- •Укорачивающие одновибраторы

- •Расширяющие одновибраторы (ждущие мультивибраторы)

- •Раздел 6 Последовательностные устройства (цифровые устройства с памятью)

- •Глава 1

- •Триггеры

- •Глава 2 rs триггер

- •Синхронный rs триггер

- •Глава 3 d триггеры, работающие по потенциалу (статические d триггеры)

- •Глава 4 Явление метастабильности

- •Глава 5 d триггеры, работающие по фронту (динамические d триггеры)

- •Глава 6 t триггеры

- •Глава 7 jk триггер

- •Глава 8 Регистры

- •Параллельные регистры

- •Глава 9 Последовательные (сдвиговые) регистры

- •Глава 10 Универсальные регистры

- •Глава 11 Счётчики

- •Двоичные асинхронные счётчики

- •Двоичные вычитающие асинхронные счётчики

- •Глава 12 Недвоичные счётчики с обратной связью

- •Глава 13 Недвоичные счётчики с предварительной записью

- •Глава 14 Синхронные счётчики

- •Глава 15 Синхронные двоичные счётчики

- •Раздел 7

- •Современные виды цифровых микросхем.

- •Глава 1

- •Микросхемы малой степени интеграции (малая логика)

- •Глава 2 Программируемые логические интегральные схемы (плис).

- •Классификация плис

- •Глава 3 Программируемые логические матрицы.

- •Глава 4 Программируемые матрицы логики (pal).

- •Глава 5 Сложные программируемые логические устройства (cpld).

- •Внутреннее устройство cpld

- •Разработка цифровых устройств на cpld

- •Глава 6 Программируемые пользователем вентильные матрицы (fpga).

- •Раздел 8

- •Индикаторы.

- •Глава 1

- •Виды индикаторов.

- •Малогабаритные лампочки накаливания

- •Расчет транзисторного ключа

- •Глава 2 Газоразрядные индикаторы.

- •Глава 3 Светодиодные индикаторы.

- •Глава 4 Жидкокристаллические индикаторы.

- •Принципы работы жидкокристаллических индикаторов

- •Режимы работы жидкокристаллических индикаторов

- •Параметры жидкокристаллических индикаторов

- •Формирование цветного изображения

- •Формирование напряжения для работы жидкокристаллического индикатора

- •Глава 5 Динамическая индикация.

- •Раздел 9

- •Синтезаторы частоты.

- •Глава 1

- •Цифровой фазовый детектор.

- •Глава 2 Фазовый компаратор.

- •Глава 3 Цепи фазовой автоподстройки частоты.

- •Глава 4 Умножители частоты

- •Глава 5 Частотный детектор, построенный на основе фапч

- •Раздел 10

- •Особенности аналого-цифрового и цифро-аналогового преобразования.

- •Глава 1

- •Квантование аналогового сигнала по времени

- •Глава 2 Погрешности дискретизатора

- •Погрешность хранения

- •Погрешность выборки

- •Глава 3 Фильтры устранения эффекта наложения спектров (Антиалайзинговые фильтры)

- •Глава 4 Дискретизация сигнала на промежуточной частоте (субдискретизация)

- •Глава 5 Параллельные ацп (flash adc)

- •Глава 6 Последовательно-параллельные ацп

- •Глава 7 ацп последовательного приближения (sar adc)

- •Глава 8 Сигма-дельта ацп

- •Глава 9 Цифроаналоговые преобразователи (цап) с суммированием токов

- •Глава 10 Цифроаналоговые преобразователи r-2r

- •Раздел 11

- •11.1 Основные блоки цифровой обработки сигналов

- •Глава 1 Двоичные сумматоры

- •Глава 2 Умножители

- •Глава 3 Постоянные запоминающие устройства.

- •Глава 4 Цифровые фильтры.

- •11.2 Микросхемы прямого цифрового синтеза радиосигналов.

- •Глава 5 Фазовые аккумуляторы

- •Глава 6 Полярные модуляторы

- •Глава 7 Квадратурные модуляторы.

- •Глава 8 Интерполирующие цифровые фильтры.

- •Глава 9 Однородные интерполирующие цифровые фильтры.

- •Микросхемы цифрового приема радиосигналов

- •Глава 10 Квадратурные демодуляторы.

- •Глава 11 Децимирующие цифровые фильтры.

- •Децимирующий фильтр с конечной импульсной характеристикой

- •Глава 12 Однородные децимирующие цифровые фильтры.

- •Раздел 12 Примеры реализации цифровых устройств

- •12.1 Электронные часы

- •Разработка структурной схемы

- •Глава 2 Разработка принципиальной схемы

- •Глава 3 Разработка принципиальной схемы индикации часов

- •12.2 Последовательные порты

- •Глава 4

- •Глава 5

Глава 4 Явление метастабильности

До сих пор мы предполагали, что сигнал на входе триггера может принимать только два состояния: логический ноль и логическая единица. Однако синхроимпульс может прийти в любой момент времени, в том числе и в момент смены состояния сигнала на входе триггера.

Если синхросигнал попадёт точно на момент перехода входным сигналом порогового уровня, то триггер на некоторое время может попасть в неустойчивое метастабильное состояние, при котором напряжение на его выходе будет находиться между уровнем логического нуля и логической единицы. Это может привести к нарушению правильной работы цифрового устройства.

Состояние метастабильности триггера подобно неустойчивому состоянию шарика, находящегося на вершине конического холма. Такая ситуация иллюстрируется рисунком 4.1. Обычно триггер не может долго находиться в состоянии метастабильности и быстро возвращается в одно из стабильных состояний. Время нахождения в метастабильном состоянии зависит от уровня шумов схемы и использованной технологии изготовления микросхем.

Рисунок 4.1.

Иллюстрация явления метастабильности

Рисунок 4.1.

Иллюстрация явления метастабильности

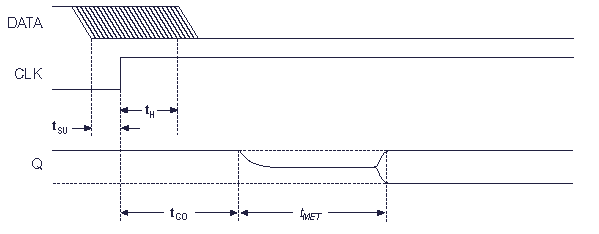

Временные параметры триггера в момент возникновения состояния метастабильности и выхода из этого состояния приведены на рисунке 2. Время tSU (register setup time or tSU) на этом рисунке это минимальное время перед синхроимпульсом, в течение которого логический уровень сигнала должен оставаться стабильным для того, чтобы избежать метастабильности выхода триггера. Время tH (register hold time or tH) это минимально необходимое время удержания стабильного сигнала на входе триггера для того, чтобы избежать метастабильности его выхода. Время состояния метатастабильности случайно и зависит от многих параметров. На рисунке 4.2 оно обозначено tMET.

Рисунок 4.2.

Временные параметры триггера в момент

возникновения состояния метастабильности

Рисунок 4.2.

Временные параметры триггера в момент

возникновения состояния метастабильности

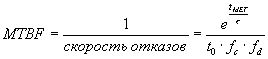

Вероятность того, что время метастабильности превысит заданную величину, экспоненциально уменьшается с ростом времени, в течение которого выход триггера находится в метастабильном состояние.

![]()

где t – это коэффициент обратно пропорциональный коэффициенту усиления и полосе пропускания элементов, входящих в состав триггера.

Склонность триггеров к метастабильности обычно оценивается величиной, обратной скорости отказов. Это значение выражается как интервал времени между отказами. Его можно определить по формуле:

где t0 = tSU – tH

fс – тактовая частота

fd – частота с которой меняются входные данные

Для того чтобы можно было оценить эту величину, приведём таблицу для двух микросхем. Последняя строчка этой таблицы эквивалентна времени метастабильности tMET = 5 нс.

Таблица 4.3. Сравнительные характеристики КМОП и Bi-КМОП триггеров

|

Условия измерения |

SN74ACT |

SN74ABT |

|

fc = 33МГц, fd = 8МГц |

8400 лет |

8.1*109 лет |

|

fc = 40МГц, fd = 10МГц |

92 дня |

1400 лет |

|

fc = 50МГц, fd = 12МГц |

- |

2 часа |

Метастабильное состояние не всегда приводит к неправильной работе цифрового устройства. Если время ожидания устройства после прихода импульса синхронизации достаточно велико, то триггер может успеть перейти в устойчивое состояние, и мы даже ничего не заметим. То есть если мы будем учитывать время метастабильности tmet то метастабильность никак не скажется на работе остальной цифровой схемы.

Если же это время будет неприемлемым для работы схемы, то можно поставить два триггера последовательно, как это показано на рисунке 4.3. Это снизит вероятность возникновения метастабильного состояния.

Рисунок 4.3.

Схема снижения вероятности возникновения

метастабильного состояния на выходе

триггера

Рисунок 4.3.

Схема снижения вероятности возникновения

метастабильного состояния на выходе

триггера

Для сравнения приведем MBTF для новой схемы. Сравнение производится тех же самых микросхем, что и в предыдущем примере. Время метастабильности tMET = 5 нс для 50 МГц,tMET = 5 нс для 67 МГц, tMET = 5 нс для 80 МГц.

Таблица 4.4 Сравнительные характеристики КМОП и Bi-КМОП триггеров

|

Условия измерения |

SN74ACT |

SN74ABT |

|

fc = 33МГц, fd = 8МГц |

2.62*1028 лет |

4.77*1047 лет |

|

fc = 40МГц, fd = 10МГц |

3,56*1019 дня |

2.18*1034 лет |

|

fc = 50МГц, fd = 12МГц |

4.9*1010 |

1*1021 лет |

|

fc = 67МГц, fd = 16МГц |

417 лет |

1.28*109 лет |

|

fc = 80МГц, fd = 20МГц |

- |

2900 лет |