- •Глава1 Что такое цифровые микросхемы. Виды цифровых микросхем

- •Глава 2 Области применения цифровых микросхем

- •Глава 3 Условные графические изображения цифровых микросхем (гост)

- •Параметры цифровых микросхем

- •Уровни логического нуля и единицы

- •Входные и выходные токи цифровых микросхем

- •Параметры, определяющие быстродействие цифровых микросхем

- •Описание логической функции цифровых схем

- •Раздел 2

- •Логический элемент "и"

- •Логический элемент "или"

- •Глава 2 Диодно-транзисторная логика (дтл)

- •Глава 3 Транзисторно-транзисторная логика (ттл)

- •Логические уровни ттл микросхем

- •Семейства ттл микросхем

- •Глава 4 Цифровые логические микросхемы, выполненные на комплементарных моп транзисторах (кмоп) Логические кмоп (кмдп) инверторы

- •Логические кмоп (кмдп) элементы "и"

- •Логические кмоп (кмдп) элементы "или"

- •Особенности применения кмоп микросхем

- •Логические уровни кмоп микросхем

- •Семейства кмоп микросхем

- •Глава 5 Согласование цифровых микросхем различных серий между

- •Согласование микросхем из различных серий между собой

- •Согласование по току

- •Согласование микросхем с различным напряжением питания

- •Глава 6 Регенерация цифрового сигнала (Триггер Шмитта)

- •Раздел 3 Арифметические основы цифровой техники.

- •Глава 1

- •Арифметические основы цифровой техники

- •Системы счисления

- •Десятичная система счисления

- •Двоичная система счисления

- •Восьмеричная система счисления

- •Шестнадцатеричная система счисления

- •Глава 2 Преобразование чисел из одной системы счисления в другую

- •Преобразование целых чисел

- •Глава 3 Преобразование дробной части числа

- •Раздел 4

- •2. Законы отрицания a. Закон дополнительных элементов

- •B. Двойное отрицание

- •C. Закон отрицательной логики

- •3. Комбинационные законы

- •A. Закон тавтологии (многократное повторение)

- •B. Закон переместительности

- •Совершенная дизъюктивная нормальная форма (сднф)

- •Совершенная конъюктивная нормальная форма (скнф)

- •Глава 3 Дешифраторы (декодеры)

- •Десятичный дешифратор (декодер)

- •Семисегментный дешифратор

- •Глава 4 Шифраторы (кодеры)

- •Глава 5 Мультиплексоры

- •Особенности построения мультиплексоров на ттл элементах

- •Особенности построения мультиплексоров на кмоп элементах

- •Глава 6 Демультиплексоры

- •Раздел 5 Генераторы

- •Глава 1

- •Генераторы периодических сигналов

- •Усилительные параметры кмоп инвертора

- •Глава 2 Осцилляторные схемы генераторов

- •Глава 3 Мультивибраторы

- •Глава 4 Особенности кварцевой стабилизации частоты цифровых генераторов

- •Глава 5 Одновибраторы (ждущие мультивибраторы)

- •Укорачивающие одновибраторы

- •Расширяющие одновибраторы (ждущие мультивибраторы)

- •Раздел 6 Последовательностные устройства (цифровые устройства с памятью)

- •Глава 1

- •Триггеры

- •Глава 2 rs триггер

- •Синхронный rs триггер

- •Глава 3 d триггеры, работающие по потенциалу (статические d триггеры)

- •Глава 4 Явление метастабильности

- •Глава 5 d триггеры, работающие по фронту (динамические d триггеры)

- •Глава 6 t триггеры

- •Глава 7 jk триггер

- •Глава 8 Регистры

- •Параллельные регистры

- •Глава 9 Последовательные (сдвиговые) регистры

- •Глава 10 Универсальные регистры

- •Глава 11 Счётчики

- •Двоичные асинхронные счётчики

- •Двоичные вычитающие асинхронные счётчики

- •Глава 12 Недвоичные счётчики с обратной связью

- •Глава 13 Недвоичные счётчики с предварительной записью

- •Глава 14 Синхронные счётчики

- •Глава 15 Синхронные двоичные счётчики

- •Раздел 7

- •Современные виды цифровых микросхем.

- •Глава 1

- •Микросхемы малой степени интеграции (малая логика)

- •Глава 2 Программируемые логические интегральные схемы (плис).

- •Классификация плис

- •Глава 3 Программируемые логические матрицы.

- •Глава 4 Программируемые матрицы логики (pal).

- •Глава 5 Сложные программируемые логические устройства (cpld).

- •Внутреннее устройство cpld

- •Разработка цифровых устройств на cpld

- •Глава 6 Программируемые пользователем вентильные матрицы (fpga).

- •Раздел 8

- •Индикаторы.

- •Глава 1

- •Виды индикаторов.

- •Малогабаритные лампочки накаливания

- •Расчет транзисторного ключа

- •Глава 2 Газоразрядные индикаторы.

- •Глава 3 Светодиодные индикаторы.

- •Глава 4 Жидкокристаллические индикаторы.

- •Принципы работы жидкокристаллических индикаторов

- •Режимы работы жидкокристаллических индикаторов

- •Параметры жидкокристаллических индикаторов

- •Формирование цветного изображения

- •Формирование напряжения для работы жидкокристаллического индикатора

- •Глава 5 Динамическая индикация.

- •Раздел 9

- •Синтезаторы частоты.

- •Глава 1

- •Цифровой фазовый детектор.

- •Глава 2 Фазовый компаратор.

- •Глава 3 Цепи фазовой автоподстройки частоты.

- •Глава 4 Умножители частоты

- •Глава 5 Частотный детектор, построенный на основе фапч

- •Раздел 10

- •Особенности аналого-цифрового и цифро-аналогового преобразования.

- •Глава 1

- •Квантование аналогового сигнала по времени

- •Глава 2 Погрешности дискретизатора

- •Погрешность хранения

- •Погрешность выборки

- •Глава 3 Фильтры устранения эффекта наложения спектров (Антиалайзинговые фильтры)

- •Глава 4 Дискретизация сигнала на промежуточной частоте (субдискретизация)

- •Глава 5 Параллельные ацп (flash adc)

- •Глава 6 Последовательно-параллельные ацп

- •Глава 7 ацп последовательного приближения (sar adc)

- •Глава 8 Сигма-дельта ацп

- •Глава 9 Цифроаналоговые преобразователи (цап) с суммированием токов

- •Глава 10 Цифроаналоговые преобразователи r-2r

- •Раздел 11

- •11.1 Основные блоки цифровой обработки сигналов

- •Глава 1 Двоичные сумматоры

- •Глава 2 Умножители

- •Глава 3 Постоянные запоминающие устройства.

- •Глава 4 Цифровые фильтры.

- •11.2 Микросхемы прямого цифрового синтеза радиосигналов.

- •Глава 5 Фазовые аккумуляторы

- •Глава 6 Полярные модуляторы

- •Глава 7 Квадратурные модуляторы.

- •Глава 8 Интерполирующие цифровые фильтры.

- •Глава 9 Однородные интерполирующие цифровые фильтры.

- •Микросхемы цифрового приема радиосигналов

- •Глава 10 Квадратурные демодуляторы.

- •Глава 11 Децимирующие цифровые фильтры.

- •Децимирующий фильтр с конечной импульсной характеристикой

- •Глава 12 Однородные децимирующие цифровые фильтры.

- •Раздел 12 Примеры реализации цифровых устройств

- •12.1 Электронные часы

- •Разработка структурной схемы

- •Глава 2 Разработка принципиальной схемы

- •Глава 3 Разработка принципиальной схемы индикации часов

- •12.2 Последовательные порты

- •Глава 4

- •Глава 5

Укорачивающие одновибраторы

Рассмотрим схему, приведённую на рисунке 5.1.

Рисунок 5.1.

Схема укорачивающего одновибратора

(ждущего мультивибратора).

Рисунок 5.1.

Схема укорачивающего одновибратора

(ждущего мультивибратора).

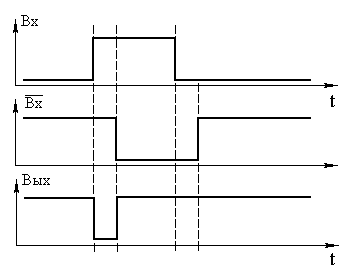

Если бы логические элементы не обладали задержкой, то на выходе такой схемы постоянно присутствовал единичный логический уровень. Однако это не так. Сигнал на выходе инвертора задержан по отношению к его входу. Временные диаграммы сигналов на входе и выходе инвертора, а также на выходе схемы логического элемента "И" приведены на рисунке 5.2.

Рисунок 5.2.

Временные диаграммы укорачивающего

одновибратора.

Рисунок 5.2.

Временные диаграммы укорачивающего

одновибратора.

Как видно из этих временных диаграмм, одновибратор, схема которого приведена на рисунке 5.1, вырабатывает одиночный импульс по переднему фронту входного сигнала. Длительность импульса на выходе такой схемы будет равна времени задержки инвертора.

Если требуется длительность выходного импульса, большая времени задержки одиночного инвертора, то можно применить дополнительные элементы задержки на пассивных RC элементах. Пример подобной схемы одновибратора приведён на рисунке 5.3, а временные диаграммы этой схемы — на рисунке 5.4.

Рисунок 5.3.

Схема укорачивающего одновибратора с

использованием RC элементов задержки.

Рисунок 5.3.

Схема укорачивающего одновибратора с

использованием RC элементов задержки.

Длительность выработанного формирователем импульса можно вычислить исходя из условия разряда конденсатора С. Действительно, пока конденсатор С разряжается до уровня порогового напряжения U, напряжение U2 воспринимается логическим элементом "2И-НЕ" как уровень логической единицы и на его выходе поддерживается уровень логического нуля. С течением времени напряжение на конденсаторе C становится равным Uпор и на выходе логического элемента "2И-НЕ" появится уровень логической единицы. Если считать, что напряжение до начала разряда на конденсаторе было равно напряжению уровня уровень логической единицы U1, то изменение напряжения UC с течением времени можно представить как:

![]() ,

,

следовательно

![]() .

.

Длительность импульса равна времени разряда конденсатора до порогового значения Uпор

![]()

Рисунок 5.4. Временные диаграммы укорачивающего одновибратора с использованием RC элементов задержки.

Расширяющие одновибраторы (ждущие мультивибраторы)

В расширяющих одновибраторах (ждущих мультивибраторах) длительность входного (запускающего) импульса должна быть короче длительности формируемого импульса.

Схема расширяющего одновибратора приведена на рисунке 5. Он выполнен на двух логических элементах. Схема охвачена положительной обратной связью, так как выход второго элемента соединен с входом первого.

Рисунок 5.5.

Схема расширяющего одновибратора

(ждущего мультивибратора).

Рисунок 5.5.

Схема расширяющего одновибратора

(ждущего мультивибратора).

В исходном состоянии на выходе элемента D2 имеется уровень логической единицы, а на выходе элемента D1 — уровень логического нуля, так как на обоих его входах присутствуют логические единицы. При поступлении на вход запускающего импульса с нулевым потенциалом, на выходе первого логического элемента появится уровень логической единицы, который через конденсатор С поступит на вход второго логического элемента. Логический элемент D2 инвертирует этот сигнал и уровень «0» по цепи обратной связи подается на второй вход логического элемента D1. Теперь даже если на входе снова появится уровень логической единицы, на выходе логического элемента D1 будет сохраняться высокое напряжение.

На выходе элемента D2 уровень логического нуля будет присутствовать до тех пор, пока конденсатор C не зарядится до уровня Uc = U1 – Uпор, а напряжение на резисторе R не достигнет порогового уровня Uпор(рисунок 4).

Длительность выходного импульса одновибратора может быть определена с помощью выражения

![]()

где Rвых — выходное сопротивление первого элемента. Uпор — пороговое напряжение логического элемента.