Раздел 12

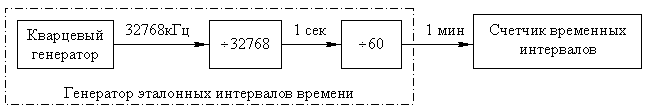

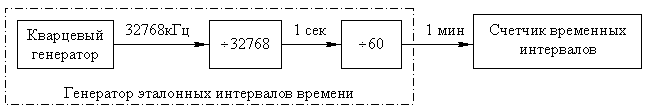

Рисунок

12.1.1 Структурная схема устройства

измерения времени

Рисунок

12.1.1 Структурная схема устройства

измерения времени

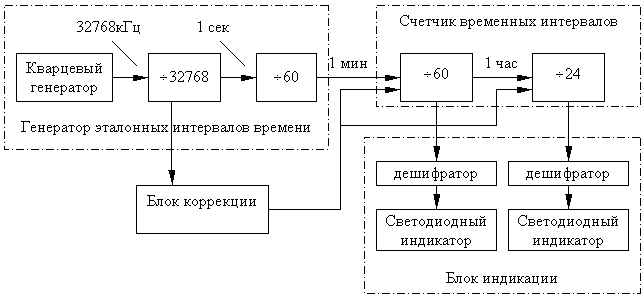

Рисунок 12.1.2.

Уточнённая структурная схема устройства

измерения времени

Рисунок 12.1.2.

Уточнённая структурная схема устройства

измерения времени

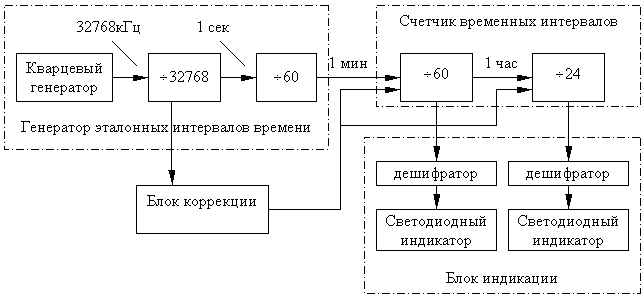

Рисунок 12.1.3.

Структурная схема часов

Рисунок 12.1.3.

Структурная схема часов

Рисунок 12.1.4.

Уточнённая структурная схема часов

Рисунок 12.1.4.

Уточнённая структурная схема часов

Рисунок 12.1.5

Схема кварцевого генератора, выполненная

на логическом инверторе

Рисунок 12.1.5

Схема кварцевого генератора, выполненная

на логическом инверторе

Рисунок 12.1.6.

Схема делителя на 32768 генератора секундных

импульсов

Рисунок 12.1.6.

Схема делителя на 32768 генератора секундных

импульсов

Рисунок

12.1.7. Схема делителя на 60 генератора

минутных импульсов

Рисунок

12.1.7. Схема делителя на 60 генератора

минутных импульсов

Рисунок 12.1.8.

Схема счётчика часовых импульсов

Рисунок 12.1.8.

Схема счётчика часовых импульсов

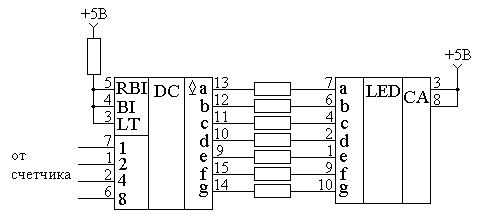

Рисунок 12.1.8.

Схема подключения одного сегмента

светодиодного индикатора к выходному

каскаду микросхемы SN74LS247D.

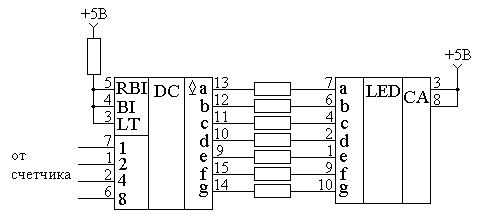

Рисунок 12.1.9.

Схема подключения светодиодного

индикатора ACSA56‑41SRWA‑F01 к микросхеме

семисегментного дешифратора SN74LS247D.

Рисунок

12.2.10 Схема последовательного DSP-порта

Рисунок

12.2.10 Схема последовательного DSP-порта

Рисунок

12.2.11 Временные диаграммы сигналов на

выходе синхронного последовательного

DSP-порта

Рисунок

12.2.11 Временные диаграммы сигналов на

выходе синхронного последовательного

DSP-порта

Рисунок

12.2.12. Упрощённая схема соединения

микросхемы АЦП с последовательным

выходом и сигнального процессора

Рисунок

12.2.12. Упрощённая схема соединения

микросхемы АЦП с последовательным

выходом и сигнального процессора

Рисунок

12.2.13. Временные диаграммы сигналов на

выводах синхронного последовательного

интерфейса SPI

Рисунок

12.2.13. Временные диаграммы сигналов на

выводах синхронного последовательного

интерфейса SPI

Рисунок

12.2.14 Схема master SPI-порта

Рисунок

12.2.14 Схема master SPI-порта

Рисунок

12.2.15. Временные диаграммы схемы

формирования сигнала выбора подчиненного

SS

Рисунок

12.2.15. Временные диаграммы схемы

формирования сигнала выбора подчиненного

SS

Рисунок

12.2.16. Схема подчиненного SPI-порта

Рисунок

12.2.16. Схема подчиненного SPI-порта

Рисунок

12.1.1 Структурная схема устройства

измерения времени

Рисунок

12.1.1 Структурная схема устройства

измерения времени

Рисунок 12.1.2.

Уточнённая структурная схема устройства

измерения времени

Рисунок 12.1.2.

Уточнённая структурная схема устройства

измерения времени Рисунок 12.1.3.

Структурная схема часов

Рисунок 12.1.3.

Структурная схема часов Рисунок 12.1.4.

Уточнённая структурная схема часов

Рисунок 12.1.4.

Уточнённая структурная схема часов Рисунок 12.1.5

Схема кварцевого генератора, выполненная

на логическом инверторе

Рисунок 12.1.5

Схема кварцевого генератора, выполненная

на логическом инверторе Рисунок 12.1.6.

Схема делителя на 32768 генератора секундных

импульсов

Рисунок 12.1.6.

Схема делителя на 32768 генератора секундных

импульсов Рисунок

12.1.7. Схема делителя на 60 генератора

минутных импульсов

Рисунок

12.1.7. Схема делителя на 60 генератора

минутных импульсов Рисунок 12.1.8.

Схема счётчика часовых импульсов

Рисунок 12.1.8.

Схема счётчика часовых импульсов

Рисунок

12.2.10 Схема последовательного DSP-порта

Рисунок

12.2.10 Схема последовательного DSP-порта Рисунок

12.2.11 Временные диаграммы сигналов на

выходе синхронного последовательного

DSP-порта

Рисунок

12.2.11 Временные диаграммы сигналов на

выходе синхронного последовательного

DSP-порта Рисунок

12.2.12. Упрощённая схема соединения

микросхемы АЦП с последовательным

выходом и сигнального процессора

Рисунок

12.2.12. Упрощённая схема соединения

микросхемы АЦП с последовательным

выходом и сигнального процессора Рисунок

12.2.13. Временные диаграммы сигналов на

выводах синхронного последовательного

интерфейса SPI

Рисунок

12.2.13. Временные диаграммы сигналов на

выводах синхронного последовательного

интерфейса SPI Рисунок

12.2.14 Схема master SPI-порта

Рисунок

12.2.14 Схема master SPI-порта Рисунок

12.2.15. Временные диаграммы схемы

формирования сигнала выбора подчиненного

SS

Рисунок

12.2.15. Временные диаграммы схемы

формирования сигнала выбора подчиненного

SS Рисунок

12.2.16. Схема подчиненного SPI-порта

Рисунок

12.2.16. Схема подчиненного SPI-порта