Раздел 7

Рисунок 1.1.

Внешний вид цифровой микросхемы малой

степени интеграции в DIP-корпусе

Рисунок 1.1.

Внешний вид цифровой микросхемы малой

степени интеграции в DIP-корпусе

Рисунок 1.2.

Внешний вид цифровой микросхемы малой

степени интеграции в SOT-23 корпусе

Рисунок 1.2.

Внешний вид цифровой микросхемы малой

степени интеграции в SOT-23 корпусе

Рисунок 1.3.

Цоколевка инвертора 1G04 в корпусе SC-70

Рисунок 1.3.

Цоколевка инвертора 1G04 в корпусе SC-70

Рисунок 1.4.

Цоколевка логического элемента ""И-НЕ"

1G00 в корпусе SC-70

Рисунок 1.4.

Цоколевка логического элемента ""И-НЕ"

1G00 в корпусе SC-70

Рисунок 1.5.

Цоколевка D-триггера 1G79 в корпусе SC-70

Рисунок 1.5.

Цоколевка D-триггера 1G79 в корпусе SC-70

Рисунок 2.1.

Классификация программируемых логических

интегральных схем (ПЛИС)

Рисунок 2.1.

Классификация программируемых логических

интегральных схем (ПЛИС)

Рисунок 3.1.

Обобщенная структура программируемых

логических матриц (ПЛМ)

Рисунок 3.1.

Обобщенная структура программируемых

логических матриц (ПЛМ)

Рисунок 3.2.

Представление внутренней структуры

схем ПЛМ, принятое в зарубежной литературе

Рисунок 3.2.

Представление внутренней структуры

схем ПЛМ, принятое в зарубежной литературе

Рисунок 4.1.

Обобщенная структура программируемых

матриц логики (ПМЛ)

Рисунок 4.1.

Обобщенная структура программируемых

матриц логики (ПМЛ)

Рисунок 5.1.

Пример внутренней схемы CPLD

Рисунок 5.1.

Пример внутренней схемы CPLD

Рисунок 5.2.

Внутренняя схема макроячейки микросхемы

CPLD

Рисунок 5.2.

Внутренняя схема макроячейки микросхемы

CPLD

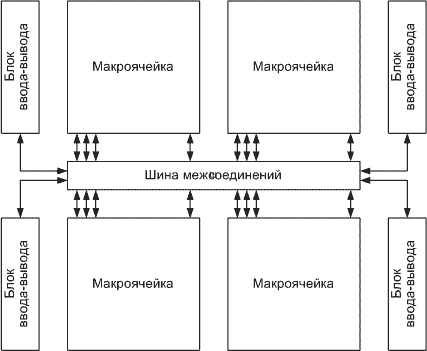

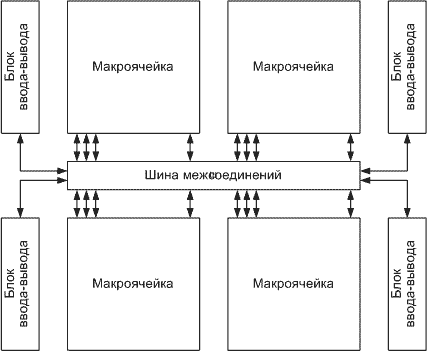

Рисунок 6.1.

Обобщенная структура микросхем FPGA

Рисунок 6.1.

Обобщенная структура микросхем FPGA

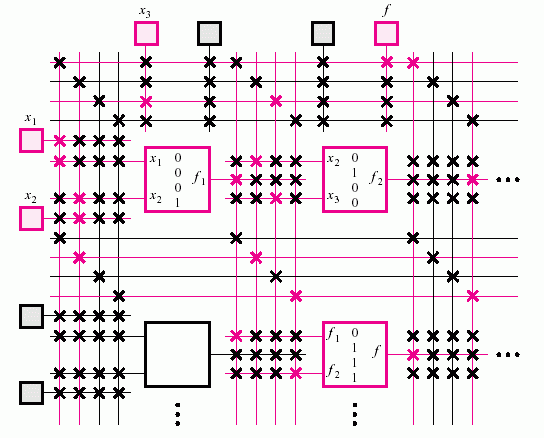

Рисунок 6.2.

Пример внутреннего устройства LUT ПЗУ

Рисунок 6.2.

Пример внутреннего устройства LUT ПЗУ

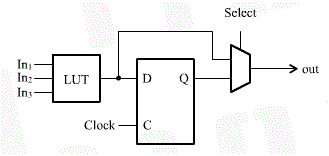

Рисунок 6.3.

Пример схемы логического блока FPGA

микросхемы

Рисунок 6.3.

Пример схемы логического блока FPGA

микросхемы

Рисунок 6.4.

Пример запрограммированного участка

FPGA

Рисунок 6.4.

Пример запрограммированного участка

FPGA

Раздел 8

Рисунок 1.1.

Внешний вид цифровой микросхемы малой

степени интеграции в DIP-корпусе

Рисунок 1.1.

Внешний вид цифровой микросхемы малой

степени интеграции в DIP-корпусе

Рисунок 1.2.

Внешний вид цифровой микросхемы малой

степени интеграции в SOT-23 корпусе

Рисунок 1.2.

Внешний вид цифровой микросхемы малой

степени интеграции в SOT-23 корпусе

Рисунок 1.3.

Цоколевка инвертора 1G04 в корпусе SC-70

Рисунок 1.3.

Цоколевка инвертора 1G04 в корпусе SC-70

Рисунок 1.4.

Цоколевка логического элемента ""И-НЕ"

1G00 в корпусе SC-70

Рисунок 1.4.

Цоколевка логического элемента ""И-НЕ"

1G00 в корпусе SC-70

Рисунок 1.5.

Цоколевка D-триггера 1G79 в корпусе SC-70

Рисунок 1.5.

Цоколевка D-триггера 1G79 в корпусе SC-70

Рисунок 2.1.

Классификация программируемых логических

интегральных схем (ПЛИС)

Рисунок 2.1.

Классификация программируемых логических

интегральных схем (ПЛИС)

Рисунок 3.1.

Обобщенная структура программируемых

логических матриц (ПЛМ)

Рисунок 3.1.

Обобщенная структура программируемых

логических матриц (ПЛМ)

Рисунок 3.2.

Представление внутренней структуры

схем ПЛМ, принятое в зарубежной литературе

Рисунок 3.2.

Представление внутренней структуры

схем ПЛМ, принятое в зарубежной литературе

Рисунок 4.1.

Обобщенная структура программируемых

матриц логики (ПМЛ)

Рисунок 4.1.

Обобщенная структура программируемых

матриц логики (ПМЛ)

Рисунок 5.1.

Пример внутренней схемы CPLD

Рисунок 5.1.

Пример внутренней схемы CPLD

Рисунок 5.2.

Внутренняя схема макроячейки микросхемы

CPLD

Рисунок 5.2.

Внутренняя схема макроячейки микросхемы

CPLD

Рисунок 6.1.

Обобщенная структура микросхем FPGA

Рисунок 6.1.

Обобщенная структура микросхем FPGA

Рисунок 6.2.

Пример внутреннего устройства LUT ПЗУ

Рисунок 6.2.

Пример внутреннего устройства LUT ПЗУ

Рисунок 6.3.

Пример схемы логического блока FPGA

микросхемы

Рисунок 6.3.

Пример схемы логического блока FPGA

микросхемы

Рисунок 6.4.

Пример запрограммированного участка

FPGA

Рисунок 6.4.

Пример запрограммированного участка

FPGA

Рисунок 1.1.

Внешний вид цифровой микросхемы малой

степени интеграции в DIP-корпусе

Рисунок 1.1.

Внешний вид цифровой микросхемы малой

степени интеграции в DIP-корпусе

Рисунок 1.2.

Внешний вид цифровой микросхемы малой

степени интеграции в SOT-23 корпусе

Рисунок 1.2.

Внешний вид цифровой микросхемы малой

степени интеграции в SOT-23 корпусе

Рисунок 1.3.

Цоколевка инвертора 1G04 в корпусе SC-70

Рисунок 1.3.

Цоколевка инвертора 1G04 в корпусе SC-70

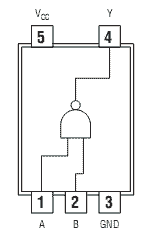

Рисунок 1.4.

Цоколевка логического элемента ""И-НЕ"

1G00 в корпусе SC-70

Рисунок 1.4.

Цоколевка логического элемента ""И-НЕ"

1G00 в корпусе SC-70

Рисунок 1.5.

Цоколевка D-триггера 1G79 в корпусе SC-70

Рисунок 1.5.

Цоколевка D-триггера 1G79 в корпусе SC-70

Рисунок 2.1.

Классификация программируемых логических

интегральных схем (ПЛИС)

Рисунок 2.1.

Классификация программируемых логических

интегральных схем (ПЛИС)

Рисунок 3.1.

Обобщенная структура программируемых

логических матриц (ПЛМ)

Рисунок 3.1.

Обобщенная структура программируемых

логических матриц (ПЛМ)

Рисунок 3.2.

Представление внутренней структуры

схем ПЛМ, принятое в зарубежной литературе

Рисунок 3.2.

Представление внутренней структуры

схем ПЛМ, принятое в зарубежной литературе

Рисунок 4.1.

Обобщенная структура программируемых

матриц логики (ПМЛ)

Рисунок 4.1.

Обобщенная структура программируемых

матриц логики (ПМЛ)

Рисунок 5.1.

Пример внутренней схемы CPLD

Рисунок 5.1.

Пример внутренней схемы CPLD

Рисунок 5.2.

Внутренняя схема макроячейки микросхемы

CPLD

Рисунок 5.2.

Внутренняя схема макроячейки микросхемы

CPLD

Рисунок 6.1.

Обобщенная структура микросхем FPGA

Рисунок 6.1.

Обобщенная структура микросхем FPGA

Рисунок 6.2.

Пример внутреннего устройства LUT ПЗУ

Рисунок 6.2.

Пример внутреннего устройства LUT ПЗУ

Рисунок 6.3.

Пример схемы логического блока FPGA

микросхемы

Рисунок 6.3.

Пример схемы логического блока FPGA

микросхемы

Рисунок 6.4.

Пример запрограммированного участка

FPGA

Рисунок 6.4.

Пример запрограммированного участка

FPGA

Рисунок 1.1

Пример пиктограмм.

Рисунок 1.1

Пример пиктограмм.

Рисунок 1.2.

Пример десятичного индикатора

Рисунок 1.2.

Пример десятичного индикатора

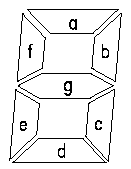

Рисунок 1.3.

Изображение семисегментного индикатора

и название его сегментов

Рисунок 1.3.

Изображение семисегментного индикатора

и название его сегментов

Рисунок 1.4.

Пример изображения буквы S на матричном

индикаторе 5*7

Рисунок 1.4.

Пример изображения буквы S на матричном

индикаторе 5*7

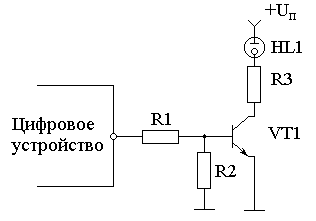

Рисунок 1.1.1

Схема подключения индикаторной лампы

накаливания к цифровой ТТЛ микросхеме

Рисунок 1.1.1

Схема подключения индикаторной лампы

накаливания к цифровой ТТЛ микросхеме

Рисунок 1.1.2.

Эквивалентная схема подключения

транзисторного ключа к цифровой ТТЛ

микросхеме

Рисунок 1.1.2.

Эквивалентная схема подключения

транзисторного ключа к цифровой ТТЛ

микросхеме

Рисунок 1.1.3. Эквивалентная схема цепи протекания обратного коллекторного тока.

Рисунок 1.1.4. Эквивалентная схема шунтирования цепи протекания обратного коллекторного тока транзисторного ключа резистором при формировании цифровой микросхемой нулевого потенциала.

Рисунок 2.1.

Схема подключения индикаторной

газоразрядной лампы к цифровой ТТЛ

микросхеме

Рисунок 2.1.

Схема подключения индикаторной

газоразрядной лампы к цифровой ТТЛ

микросхеме

Рисунок 2.2.

Внешний вид газоразрядного индикатора

ИН-1

Рисунок 2.2.

Внешний вид газоразрядного индикатора

ИН-1

Рисунок 2.3.

Внешний вид индикаторной панели на

газоразрядных лампах

Рисунок 2.3.

Внешний вид индикаторной панели на

газоразрядных лампах

Рисунок 2.4.

Схема подключения индикаторной

газоразрядной лампы к десятичному

дешифратору

Рисунок 2.4.

Схема подключения индикаторной

газоразрядной лампы к десятичному

дешифратору

Рисунок 2.5.

Внешний вид газоразрядного индикатора

с подогревным катодом

Рисунок 2.5.

Внешний вид газоразрядного индикатора

с подогревным катодом

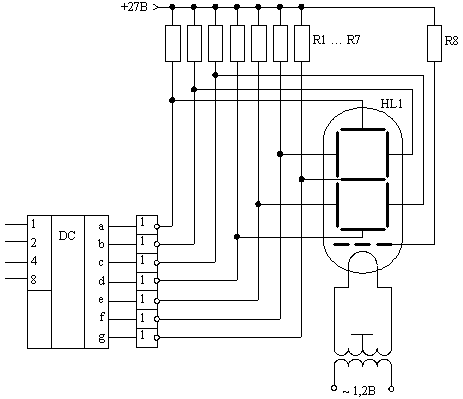

Рисунок 2.6.

Схема подключения семисегментного

газоразрядного индикатора к дешифратору

Рисунок 2.6.

Схема подключения семисегментного

газоразрядного индикатора к дешифратору

Рисунок 2.6.

Схема подключения семисегментного

газоразрядного индикатора к дешифратору

с вытекающим током

Рисунок 2.6.

Схема подключения семисегментного

газоразрядного индикатора к дешифратору

с вытекающим током

Рисунок 1.1

Пример пиктограмм.

Рисунок 1.1

Пример пиктограмм.

Рисунок 1.2.

Пример десятичного индикатора

Рисунок 1.2.

Пример десятичного индикатора

Рисунок 1.3.

Изображение семисегментного индикатора

и название его сегментов

Рисунок 1.3.

Изображение семисегментного индикатора

и название его сегментов

Рисунок 1.4.

Пример изображения буквы S на матричном

индикаторе 5*7

Рисунок 1.4.

Пример изображения буквы S на матричном

индикаторе 5*7

Рисунок 1.1.1

Схема подключения индикаторной лампы

накаливания к цифровой ТТЛ микросхеме

Рисунок 1.1.1

Схема подключения индикаторной лампы

накаливания к цифровой ТТЛ микросхеме

Рисунок 1.1.2.

Эквивалентная схема подключения

транзисторного ключа к цифровой ТТЛ

микросхеме

Рисунок 1.1.2.

Эквивалентная схема подключения

транзисторного ключа к цифровой ТТЛ

микросхеме

Рисунок 1.1.3. Эквивалентная схема цепи протекания обратного коллекторного тока.

Рисунок 1.1.4. Эквивалентная схема шунтирования цепи протекания обратного коллекторного тока транзисторного ключа резистором при формировании цифровой микросхемой нулевого потенциала.

Рисунок 2.1.

Схема подключения индикаторной

газоразрядной лампы к цифровой ТТЛ

микросхеме

Рисунок 2.1.

Схема подключения индикаторной

газоразрядной лампы к цифровой ТТЛ

микросхеме

Рисунок 2.2.

Внешний вид газоразрядного индикатора

ИН-1

Рисунок 2.2.

Внешний вид газоразрядного индикатора

ИН-1

Рисунок 2.3.

Внешний вид индикаторной панели на

газоразрядных лампах

Рисунок 2.3.

Внешний вид индикаторной панели на

газоразрядных лампах

Рисунок 2.4.

Схема подключения индикаторной

газоразрядной лампы к десятичному

дешифратору

Рисунок 2.4.

Схема подключения индикаторной

газоразрядной лампы к десятичному

дешифратору

Рисунок 2.5.

Внешний вид газоразрядного индикатора

с подогревным катодом

Рисунок 2.5.

Внешний вид газоразрядного индикатора

с подогревным катодом

Рисунок 2.6.

Схема подключения семисегментного

газоразрядного индикатора к дешифратору

Рисунок 2.6.

Схема подключения семисегментного

газоразрядного индикатора к дешифратору

Рисунок 2.6.

Схема подключения семисегментного

газоразрядного индикатора к дешифратору

с вытекающим током

Рисунок 2.6.

Схема подключения семисегментного

газоразрядного индикатора к дешифратору

с вытекающим током

Рисунок 1.1

Пример пиктограмм.

Рисунок 1.1

Пример пиктограмм.

Рисунок 1.2.

Пример десятичного индикатора

Рисунок 1.2.

Пример десятичного индикатора

Рисунок 1.3.

Изображение семисегментного индикатора

и название его сегментов

Рисунок 1.3.

Изображение семисегментного индикатора

и название его сегментов

Рисунок 1.4.

Пример изображения буквы S на матричном

индикаторе 5*7

Рисунок 1.4.

Пример изображения буквы S на матричном

индикаторе 5*7

Рисунок 1.1.1

Схема подключения индикаторной лампы

накаливания к цифровой ТТЛ микросхеме

Рисунок 1.1.1

Схема подключения индикаторной лампы

накаливания к цифровой ТТЛ микросхеме

Рисунок 1.1.2.

Эквивалентная схема подключения

транзисторного ключа к цифровой ТТЛ

микросхеме

Рисунок 1.1.2.

Эквивалентная схема подключения

транзисторного ключа к цифровой ТТЛ

микросхеме

Рисунок 1.1.3. Эквивалентная схема цепи протекания обратного коллекторного тока.

Рисунок 1.1.4. Эквивалентная схема шунтирования цепи протекания обратного коллекторного тока транзисторного ключа резистором при формировании цифровой микросхемой нулевого потенциала.

Рисунок 2.1.

Схема подключения индикаторной

газоразрядной лампы к цифровой ТТЛ

микросхеме

Рисунок 2.1.

Схема подключения индикаторной

газоразрядной лампы к цифровой ТТЛ

микросхеме

Рисунок 2.2.

Внешний вид газоразрядного индикатора

ИН-1

Рисунок 2.2.

Внешний вид газоразрядного индикатора

ИН-1

Рисунок 2.3.

Внешний вид индикаторной панели на

газоразрядных лампах

Рисунок 2.3.

Внешний вид индикаторной панели на

газоразрядных лампах

Рисунок 2.4.

Схема подключения индикаторной

газоразрядной лампы к десятичному

дешифратору

Рисунок 2.4.

Схема подключения индикаторной

газоразрядной лампы к десятичному

дешифратору

Рисунок 2.5.

Внешний вид газоразрядного индикатора

с подогревным катодом

Рисунок 2.5.

Внешний вид газоразрядного индикатора

с подогревным катодом

Рисунок 2.6.

Схема подключения семисегментного

газоразрядного индикатора к дешифратору

Рисунок 2.6.

Схема подключения семисегментного

газоразрядного индикатора к дешифратору

Рисунок 2.6.

Схема подключения семисегментного

газоразрядного индикатора к дешифратору

с вытекающим током

Рисунок 2.6.

Схема подключения семисегментного

газоразрядного индикатора к дешифратору

с вытекающим током

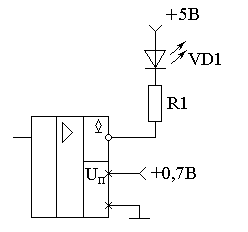

Рисунок 3.6. Схема подключения светодиодного индикатора к цифровой ТТЛ микросхеме.

Рисунок 3.7. Схема подключения светодиодного индикатора к цифровой микросхеме с пятивольтовым питанием.

Рисунок 3.8. Использование тока единицы для зажигания светодиодного индикатора.

Рисунок 3.9. Схема подключения светодиодного индикатора к цифровой микросхеме с открытым коллектором.

Рисунок 4.1.

Вращение поляризации света жидким

кристаллом

Рисунок 4.1.

Вращение поляризации света жидким

кристаллом

Рисунок 4.2.

Вращение поляризации света жидким

кристаллом

Рисунок 4.2.

Вращение поляризации света жидким

кристаллом

Рисунок 4.4.

Принципиальная схема контроллера

семисегментного жидкокристаллического

индикатора

Рисунок 4.4.

Принципиальная схема контроллера

семисегментного жидкокристаллического

индикатора

Рисунок 5.1.

Структурная схема динамической индикации

Рисунок 5.1.

Структурная схема динамической индикации

Рисунок 5.2 схема протекания тока по одному из сегментов индикатора.

Рисунок 5.3.

Принципиальная схема блока динамической

индикации.

Рисунок 5.3.

Принципиальная схема блока динамической

индикации.