Раздел 5 Рисунок 1.1 Схема генератора.

Рисунок 1.2.

Схема измерения усилительных свойств

логического инвертора.

Рисунок 1.2.

Схема измерения усилительных свойств

логического инвертора.

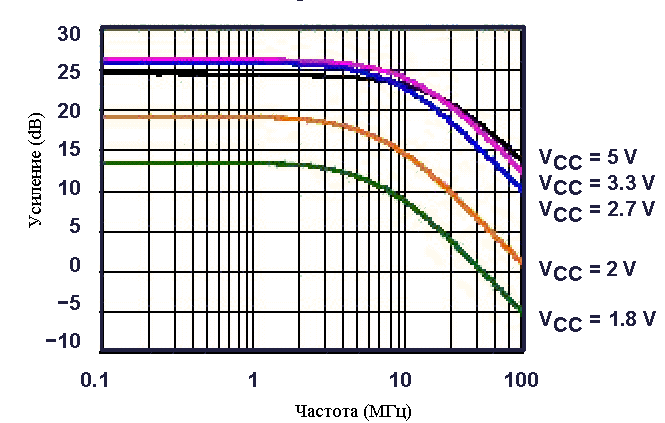

Рисунок 1.3.

Амплитудно-частотная характеристика

инвертора 74LVC1GU04.

Рисунок 1.3.

Амплитудно-частотная характеристика

инвертора 74LVC1GU04.

Рисунок 2.1.

Ёмкостная трёхточка, выполненная на

биполярном транзисторе.

Рисунок 2.1.

Ёмкостная трёхточка, выполненная на

биполярном транзисторе.

Рисунок 2.2.

Ёмкостная трёхточка, выполненная на

логическом инверторе.

Рисунок 2.2.

Ёмкостная трёхточка, выполненная на

логическом инверторе.

Рисунок 2.3.

Схема кварцевого генератора, выполненная

на логическом инверторе.

Рисунок 2.3.

Схема кварцевого генератора, выполненная

на логическом инверторе.

Рисунок 2.4.

Схема кварцевого генератора, выполненная

на элементе логического "И".

Рисунок 2.4.

Схема кварцевого генератора, выполненная

на элементе логического "И".

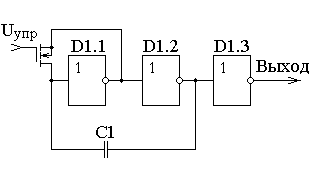

Рисунок 3.1.

Схема мультивибратора, выполненная на

двух логических инверторах.

Рисунок 3.1.

Схема мультивибратора, выполненная на

двух логических инверторах.

Рисунок 3.2.

Упрощённая схема мультивибратора.

Рисунок 3.2.

Упрощённая схема мультивибратора.

Рисунок 3.3.

Схема генератора, управляемого

напряжением.

Рисунок 3.3.

Схема генератора, управляемого

напряжением.

Рисунок 3.4.

Схема мультивибратора с кварцевой

стабилизацией частоты.

Рисунок 3.4.

Схема мультивибратора с кварцевой

стабилизацией частоты.

Рисунок

4.9.

а - эквивалентная схема кварцевого

резонатора;

б - зависимость сопротивления

кварцевого резонатора от частоты.

Рисунок

4.9.

а - эквивалентная схема кварцевого

резонатора;

б - зависимость сопротивления

кварцевого резонатора от частоты.

Рисунок 5.1.

Схема укорачивающего одновибратора

(ждущего мультивибратора).

Рисунок 5.1.

Схема укорачивающего одновибратора

(ждущего мультивибратора).

Рисунок 5.2.

Временные диаграммы укорачивающего

одновибратора.

Рисунок 5.2.

Временные диаграммы укорачивающего

одновибратора.

Рисунок 5.3.

Схема укорачивающего одновибратора с

использованием RC элементов задержки.

Рисунок 5.3.

Схема укорачивающего одновибратора с

использованием RC элементов задержки.

Рисунок 5.4. Временные диаграммы укорачивающего одновибратора с использованием RC элементов задержки.

Рисунок 5.5.

Схема расширяющего одновибратора

(ждущего мультивибратора).

Рисунок 5.5.

Схема расширяющего одновибратора

(ждущего мультивибратора).

Раздел 6

Рисунок 1.1

Схема простейшего триггера, построенного

на инверторах.

Рисунок 1.1

Схема простейшего триггера, построенного

на инверторах.

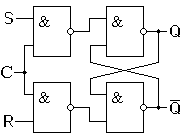

Рисунок 2.2

Схема простейшего rs триггера на

схемах "2И-НЕ". Входы R и S инверсные

(активный уровень'0').

Рисунок 2.2

Схема простейшего rs триггера на

схемах "2И-НЕ". Входы R и S инверсные

(активный уровень'0').

Таблица 2.1. Таблица истинности RS триггера.

|

R |

S |

Q(t) |

Q(t+1) |

Пояснения |

|

0 |

0 |

0 |

0 |

Режим хранения информации R=S=0 |

|

0 |

0 |

1 |

1 | |

|

0 |

1 |

0 |

1 |

Режим установки единицы S=1 |

|

0 |

1 |

1 |

1 | |

|

1 |

0 |

0 |

0 |

Режим записи нуля R=1 |

|

1 |

0 |

1 |

0 | |

|

1 |

1 |

0 |

* |

R=S=1 запрещенная комбинация |

|

1 |

1 |

1 |

* |

Рисунок 2.3.

Схема простейшего RS триггера на

схемах "ИЛИ". Входы R и S прямые

(активный уровень '1').

Рисунок 2.3.

Схема простейшего RS триггера на

схемах "ИЛИ". Входы R и S прямые

(активный уровень '1').

Рисунок 2.4.

Условно-графическое обозначение

RS триггера.

Рисунок 2.4.

Условно-графическое обозначение

RS триггера.

Рисунок 2.5.

Схема синхронного RS триггера,

построенного на элементах "И-НЕ".

Рисунок 2.5.

Схема синхронного RS триггера,

построенного на элементах "И-НЕ".

Таблица 2.2 Таблица истинности синхронного RS триггера.

|

С |

R |

S |

Q(t) |

Q(t+1) |

Пояснения |

|

0 |

x |

x |

0 |

0 |

Режим хранения информации |

|

0 |

x |

x |

1 |

1 | |

|

1 |

0 |

0 |

0 |

0 |

Режим хранения информации |

|

1 |

0 |

0 |

1 |

1 | |

|

1 |

0 |

1 |

0 |

1 |

Режим установки единицы S=1 |

|

1 |

0 |

1 |

1 |

1 | |

|

1 |

1 |

0 |

0 |

0 |

Режим записи нуля R=1 |

|

1 |

1 |

0 |

1 |

0 | |

|

1 |

1 |

1 |

0 |

* |

R=S=1 запрещенная комбинация |

|

1 |

1 |

1 |

1 |

* |

Рисунок 2.6.

Условно-графическое обозначение

синхронного RS триггера.

Рисунок 2.6.

Условно-графическое обозначение

синхронного RS триггера.

Рисунок 3.1.

Схема D триггера (защелки).

Рисунок 3.1.

Схема D триггера (защелки).

Рисунок 3.2.

Условно-графическое обозначение

D триггера (защелки).

Рисунок 3.2.

Условно-графическое обозначение

D триггера (защелки).

Таблица 3.1. Таблица истинности D триггера.

|

С |

D |

Q(t) |

Q(t+1) |

Пояснения |

|

0 |

x |

0 |

0 |

Режим хранения информации |

|

0 |

x |

1 |

1 | |

|

1 |

0 |

x |

0 |

Режим записи информации |

|

1 |

1 |

x |

1 |

Рисунок 3.3

Принципиальная схема D триггера на

элементах "2И-НЕ".

Рисунок 3.3

Принципиальная схема D триггера на

элементах "2И-НЕ".

Рисунок 3.4.

Цоколевка 4-х статических D-триггеров

1533ТМ7 (74ALS75).

Рисунок 3.4.

Цоколевка 4-х статических D-триггеров

1533ТМ7 (74ALS75).

Рисунок 3.5.

Схема статического D-триггера с

дополнительными входами R и S.

Рисунок 3.5.

Схема статического D-триггера с

дополнительными входами R и S.

Рисунок 3.6.

Условно-графическое статического

D-триггера с дополнительными входами R

и S.

Рисунок 3.6.

Условно-графическое статического

D-триггера с дополнительными входами R

и S.

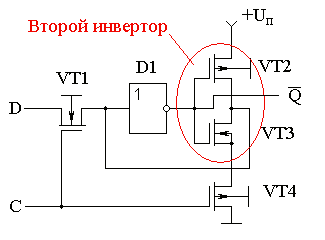

Рисунок 3.7.

Схема D триггера, реализованная на

КМОП элементах.

Рисунок 3.7.

Схема D триггера, реализованная на

КМОП элементах.

Рисунок 3.8.

Временная диаграмма статического

D триггера (защелки).

Рисунок 3.8.

Временная диаграмма статического

D триггера (защелки).

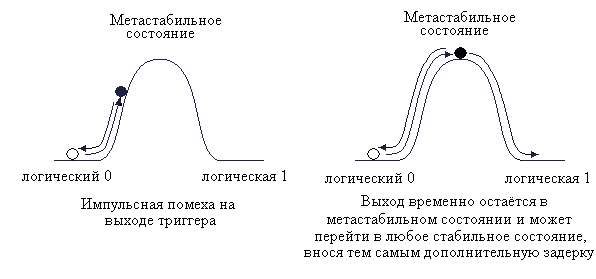

Рисунок 4.1.

Иллюстрация явления метастабильности

Рисунок 4.1.

Иллюстрация явления метастабильности

В

Рисунок 4.2.

Временные параметры триггера в момент

возникновения состояния метастабильности

Рисунок 4.2.

Временные параметры триггера в момент

возникновения состояния метастабильности

Таблица 4.3. Сравнительные характеристики КМОП и Bi-КМОП триггеров

|

Условия измерения |

SN74ACT |

SN74ABT |

|

fc = 33МГц, fd = 8МГц |

8400 лет |

8.1*109 лет |

|

fc = 40МГц, fd = 10МГц |

92 дня |

1400 лет |

|

fc = 50МГц, fd = 12МГц |

- |

2 часа |

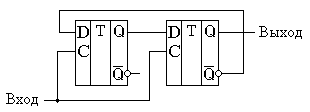

Рисунок 4.3.

Схема снижения вероятности возникновения

метастабильного состояния на выходе

триггера

Рисунок 4.3.

Схема снижения вероятности возникновения

метастабильного состояния на выходе

триггера

Таблица 4.4 Сравнительные характеристики КМОП и Bi-КМОП триггеров

|

Условия измерения |

SN74ACT |

SN74ABT |

|

fc = 33МГц, fd = 8МГц |

2.62*1028 лет |

4.77*1047 лет |

|

fc = 40МГц, fd = 10МГц |

3,56*1019 дня |

2.18*1034 лет |

|

fc = 50МГц, fd = 12МГц |

4.9*1010 |

1*1021 лет |

|

fc = 67МГц, fd = 16МГц |

417 лет |

1.28*109 лет |

|

fc = 80МГц, fd = 20МГц |

- |

2900 лет |

Рисунок 5.1.

Схема динамического D триггера,

работающего по фронту

Рисунок 5.1.

Схема динамического D триггера,

работающего по фронту

Рисунок 5.2.

Временные диаграммы D триггера

Рисунок 5.2.

Временные диаграммы D триггера

Рисунок 5.3.

Условно-графическое обозначение

динамического D триггера

Рисунок 5.3.

Условно-графическое обозначение

динамического D триггера

Рисунок 5.4.

Обозначение динамических входов

Рисунок 5.4.

Обозначение динамических входов

Рисунок 5.5

Принципиальная схема одного триггера

микросхемы 1533ТМ2

Рисунок 5.5

Принципиальная схема одного триггера

микросхемы 1533ТМ2

Рисунок 6.1.

Схема T триггера, построенная на

основе D триггера

Рисунок 6.1.

Схема T триггера, построенная на

основе D триггера

Рисунок 6.2.

Временные диаграммы T триггера

Рисунок 6.2.

Временные диаграммы T триггера

Рисунок 6.3.

Условно-графическое обозначение

T триггера

Рисунок 6.3.

Условно-графическое обозначение

T триггера

Рисунок 6.4.

Схема синхронного T триггера,

построенная на основе D триггера

Рисунок 6.4.

Схема синхронного T триггера,

построенная на основе D триггера

Рисунок 6.5.

Временные диаграммы синхронного

T триггера

Рисунок 6.5.

Временные диаграммы синхронного

T триггера

Рисунок 6.6.

Условно-графическое обозначение

синхронного T триггера

Рисунок 6.6.

Условно-графическое обозначение

синхронного T триггера

Таблица 7.1. Таблица истинности jk триггера.

|

С |

K |

J |

Q(t) |

Q(t+1) |

Пояснения |

|

0 |

x |

x |

0 |

0 |

Режим хранения информации |

|

0 |

x |

x |

1 |

1 | |

|

1 |

0 |

0 |

0 |

0 |

Режим хранения информации |

|

1 |

0 |

0 |

1 |

1 | |

|

1 |

0 |

1 |

0 |

1 |

Режим установки единицы J=1 |

|

1 |

0 |

1 |

1 |

1 | |

|

1 |

1 |

0 |

0 |

0 |

Режим записи нуля K=1 |

|

1 |

1 |

0 |

1 |

0 | |

|

1 |

1 |

1 |

0 |

1 |

K=J=1 счетный режим триггера |

|

1 |

1 |

1 |

1 |

0 |

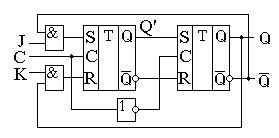

Рисунок 7.1.

Внутренняя схема jk триггера

Рисунок 7.1.

Внутренняя схема jk триггера

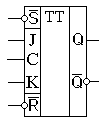

Рисунок 7.2.

Условно-графическое обозначение

jk триггера

Рисунок 7.2.

Условно-графическое обозначение

jk триггера

Рисунок 7.3.

Схема обнаружения короткого импульса

на jk триггере

Рисунок 7.3.

Схема обнаружения короткого импульса

на jk триггере

Рисунок 7.4.

Схема ждущего мультивибратора, собранного

на jk триггере

Рисунок 7.4.

Схема ждущего мультивибратора, собранного

на jk триггере

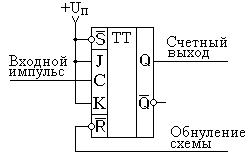

Рисунок 7.5.

Схема счетного триггера, построенного

на jk триггере

Рисунок 7.5.

Схема счетного триггера, построенного

на jk триггере

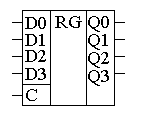

Рисунок 8.1.

Схема параллельного регистра

Рисунок 8.1.

Схема параллельного регистра

Рисунок 8.2.

Условно-графическое обозначение

параллельного регистра

Рисунок 8.2.

Условно-графическое обозначение

параллельного регистра

Рисунок 8.3.

Увеличение разрядности параллельного

регистра

Рисунок 8.3.

Увеличение разрядности параллельного

регистра

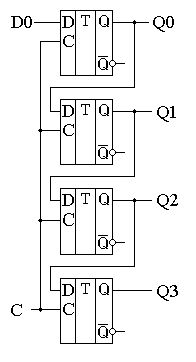

Рисунок 9.1.

Схема последовательного (сдвигового)

регистра

Рисунок 9.1.

Схема последовательного (сдвигового)

регистра

Рисунок 9.2.

Условно-графическое обозначение

последовательного (сдвигового) регистра

Рисунок 9.2.

Условно-графическое обозначение

последовательного (сдвигового) регистра

Рисунок 9.3.

Временная диаграмма работы сдвигового

регистра

Рисунок 9.3.

Временная диаграмма работы сдвигового

регистра

Рисунок 10.1.

Принципиальная схема универсального

регистра

Рисунок 10.1.

Принципиальная схема универсального

регистра

Рисунок 10.2.

Обозначение универсального регистра

на принципиальных схемах

Рисунок 10.2.

Обозначение универсального регистра

на принципиальных схемах

Рисунок 11.1.

Реализация счетного T-триггера на

универсальном D-триггере

Рисунок 11.1.

Реализация счетного T-триггера на

универсальном D-триггере

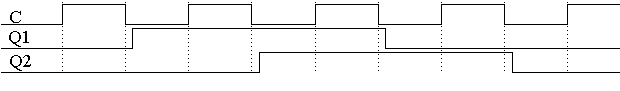

Рисунок 11.2 Временные диаграммы сигналов на входе и выходах T-триггера.

Рисунок 11.3.

Схема четырёхразрядного счётчика,

построенного на универсальных D-триггерах

Рисунок 11.3.

Схема четырёхразрядного счётчика,

построенного на универсальных D-триггерах

Рисунок 11.4

Временная диаграмма четырёхразрядного

счётчика

Рисунок 11.4

Временная диаграмма четырёхразрядного

счётчика

Таблица 11.1. Изменение уровней на выходе суммирующего счётчика при поступлении на его вход импульсов.

|

номер входного импульса |

Q3 |

Q2 |

Q1 |

Q0 |

|

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

0 |

1 |

|

2 |

0 |

0 |

1 |

0 |

|

3 |

0 |

0 |

1 |

1 |

|

4 |

0 |

1 |

0 |

0 |

|

5 |

0 |

1 |

0 |

1 |

|

6 |

0 |

1 |

1 |

0 |

|

7 |

0 |

1 |

1 |

1 |

|

8 |

1 |

0 |

0 |

0 |

|

9 |

1 |

0 |

0 |

1 |

|

10 |

1 |

0 |

1 |

0 |

|

11 |

1 |

0 |

1 |

1 |

|

12 |

1 |

1 |

0 |

0 |

|

13 |

1 |

1 |

0 |

1 |

|

14 |

1 |

1 |

1 |

0 |

|

15 |

1 |

1 |

1 |

1 |

Рисунок 11.5. Четырёхразрядный двоичный счётчик.

Рисунок 11.6 Схема четырёхразрядного двоичного вычитающего счётчика, построенного на универсальных D-триггерах.

Рисунок 11.7. Временная диаграмма четырёхразрядного вычитающего счётчика.

Таблица 11.2. Изменение уровней на выходе вычитающего счётчика при поступлении на его вход импульсов.

|

номер входного импульса |

Q3 |

Q2 |

Q1 |

Q0 |

|

0 |

0 |

0 |

0 |

0 |

|

1 |

1 |

1 |

1 |

1 |

|

2 |

1 |

1 |

1 |

0 |

|

3 |

1 |

1 |

0 |

1 |

|

4 |

1 |

1 |

0 |

0 |

|

5 |

1 |

0 |

1 |

1 |

|

6 |

1 |

0 |

1 |

0 |

|

7 |

1 |

0 |

0 |

1 |

|

8 |

1 |

0 |

0 |

0 |

|

9 |

0 |

1 |

1 |

1 |

|

10 |

0 |

1 |

1 |

0 |

|

11 |

0 |

1 |

0 |

1 |

|

12 |

0 |

1 |

0 |

0 |

|

13 |

0 |

0 |

1 |

1 |

|

14 |

0 |

0 |

1 |

0 |

|

15 |

0 |

0 |

0 |

1 |

Рисунок 12.1. Временная диаграмма четырёхразрядного счётчика

Рисунок 12.2

Схема десятичного счётчика, построенного

на основе двоичного счётчика

Рисунок 12.2

Схема десятичного счётчика, построенного

на основе двоичного счётчика

Рисунок 12.3

Принципиальная схема делителя на 1000,

построенного на основе трёх двоичных

счётчиков

Рисунок 12.3

Принципиальная схема делителя на 1000,

построенного на основе трёх двоичных

счётчиков

Рисунок 12.4.

Схема делителя с переменным коэффициентом

деления с максимальным коэффициентом

деления 100, построенного на основе двух

десятичных счётчиков

Рисунок 12.4.

Схема делителя с переменным коэффициентом

деления с максимальным коэффициентом

деления 100, построенного на основе двух

десятичных счётчиков

Рисунок 13.1.

Схема счётчика с возможностью параллельной

записи

Рисунок 13.1.

Схема счётчика с возможностью параллельной

записи

Рисунок 13.2.

Условно-графическое обозначение счётчика

с возможностью параллельной записи

Рисунок 13.2.

Условно-графическое обозначение счётчика

с возможностью параллельной записи

Рисунок 13.3

Схема делителя на 1000, построенного на

основе трёх двоичных счётчиков с

предварительной записью

Рисунок 13.3

Схема делителя на 1000, построенного на

основе трёх двоичных счётчиков с

предварительной записью

Рисунок 14.1. Схема кольцевого счетчика.

Временные диаграммы этой схемы приведены на рисунке 14.2.

а)

б)

Рисунок 14.3. Временные диаграммы сигналов 3-разрядного кольцевого синхронного счётчика при правильной (а) и ошибочной (б) работе.

Рисунок 14.4. Схема 2-разрядного счетчика с проверкой правильности его работы.

Рисунок 14.5. Временные диаграммы сигналов на выходах 2-разрядного счетчика счётчика с проверкой правильности его работы.

Рисунок 15.1.

Принципиальная схема четырёхразрядного

синхронного двоичного счётчика

Рисунок 15.1.

Принципиальная схема четырёхразрядного

синхронного двоичного счётчика

Рисунок 15.2.

Условно-графическое обозначение

синхронного счётчика с возможностью

параллельной записи

Рисунок 15.2.

Условно-графическое обозначение

синхронного счётчика с возможностью

параллельной записи

Рисунок 15.3.

Принципиальная схема 32-х разрядного

синхронного двоичного счётчика

Рисунок 15.3.

Принципиальная схема 32-х разрядного

синхронного двоичного счётчика