metoda_2013

.pdf

АРХИТЕКТУРА ВЫЧИСЛИТЕЛЬНЫХ СИСТЕМ

Средняя длина программы;

LСР |

|

1 |

* |

mk |

lk |

|

rk |

|

|

S k |

S k |

||||||

|

|

r |

( k ) |

Sk 1 |

|

|

||

|

|

|

|

|

|

|

|

число классов объектов; r – ранг задачи.

– количество объектов, которые к-ом шаге относ-ся к Sk классу. m –

Величина расхождения задачи- D L Lñð

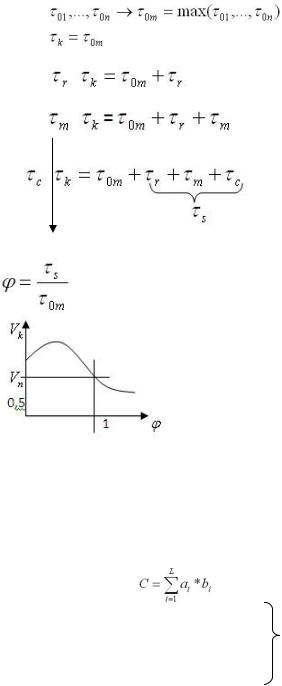

Параллелизм независимых ветвей:

Суть состоит в том, что в программе могут быть выделены независимые части, которые называются ветвями. ветвями. Ветвь Х не зависит от ветви У, если выполняются следующие условия:

ветви не зависят от данных, т.е. ни одна из входных переменных на ветви Х не является выходной переменной на ветви У; ветви выполняются по разным программам; ветви независимы по управлению.

Отличие параллелизма независимых ветвей от естественного параллелизма состоит в том, что выходные результаты ветвей используются для выполнения следующих операций.

Отличие параллелизма независимых ветвей от множества объектов состоит в том, что в параллелизме множества объектов для всех объектов используются копии одной и той же программы.

Параллелизм смежных операций или локальный параллелизм.

Параллелизм смежных операций имеет место тогда, когда входные данные текущих операций получены на более ранних этапах и выполнение этих операций можно совместить во времени.

Характеристики:

Показатель связности смежных операций (αlpha) – вероятность того, что результат некоторой операции будет использован в следующей за ней операции. Чем меньше alpha, тем больше глубина параллелизма смежных операций; Вероятность того, что начиная от данной операции имеется

цепочка длиной не менее l операций, которые можно выполнять одновременно.

Gamma – вероятность того, что |

начиная от |

данной операции |

|||||||

|

|

|

(l 1)*l |

|

(l 1)*l |

имеется |

цепочка из |

||

|

|

|

|

|

|

|

ровно |

l |

операций, |

|

|

(1 ) 2 |

(1 ) |

2 |

|||||

l |

которые |

можно |

|||||||

|

|

|

|

|

|

|

|

|

|

450

АРХИТЕКТУРА ВЫЧИСЛИТЕЛЬНЫХ СИСТЕМ |

|

|

||

выполнять одновременно; |

|

|

|

|

Глубина параллелизма смежных операций, |

|

|||

|

(l 1)*l |

т.е. |

математическое |

|

ожидание длины цепочки |

||||

|

|

|||

LnCO |

(1 ) |

2 |

операций, которые можно |

|

|||

|

выполнять одновременно. |

||

|

l 1 |

|

|

|

|

|

Какой из видов параллелизма реализуется в современных универсальных процессорах (например, в процессоре Pentium)? Ответ обоснуйте.

Разделяя вычислительную работу, выполняемую в традиционных микропроцессорах одним ядром Pentium, между несколькими исполнительными ядрами Pentium, многоядерный процессор может выполнять больше работы за конкретный интервал времени и улучшать таким образом впечатления пользователей от работы с системой. Чтобы это улучшение стало возможным, ПО должно поддерживать распределение нагрузки между несколькими исполнительными ядрами. Эта функциональность называется параллелизмом на уровне потоков или организацией поточной обработки, а поддерживающие ее приложения и операционные системы (такие, как Microsoft Windows* XP) называются многопоточными.

Процессор, поддерживающий параллелизм на уровне потоков, может выполнять полностью обособленные потоки кода, например, поток приложения и поток операционной системы или два потока одного приложения (особенно большую выгоду извлекают из параллелизма на уровне потоков мультимедийные приложения, потому что многие их операции могут выполняться параллельно).

Можно ожидать, что по мере увеличения числа многопоточных приложений, использующих достоинства этой архитектуры, многоядерные процессоры будут обеспечивать все новые и новые преимущества пользователям ПК как дома, так и на работе. Многоядерные процессоры могут также улучшить впечатления пользователей от работы в многозадачных средах, а именно при выполнении нескольких приложений переднего плана одновременно с несколькими фоновыми приложениями, такими, как антивирусное и защитное ПО, утилиты для беспроводной связи, управляющие программы и приложения, служащие для сжатия файлов, шифрования и синхронизации.

Как и другие аппаратные способы реализации многопоточности, разработанные и совершенствуемые в Intel, многоядерная архитектура отражает переход к параллельной обработке -

451

АРХИТЕКТУРА ВЫЧИСЛИТЕЛЬНЫХ СИСТЕМ

концепции, зародившейся в мире суперкомпьютеров. Например, технология Hyper-Threading (HT), представленная корпорацией Intel в 2002 году, обеспечивает возможность параллельного выполнения задач, объединяя несколько "потоков" в одноядерном процессоре. Но технология HT ограничена одним ядром, более эффективно использующим имеющиеся ресурсы для обеспечения лучшей поддержки многопоточности, тогда как многоядерная архитектура включает два (или более) полных набора исполнительных ресурсов.

Специалисты корпорации Intel считают, что многоядерная архитектура способна обеспечить несколько важных возможностей, улучшающих впечатления пользователей, в том числе увеличение числа выполняемых одновременно задач, выполнение требовательных к вычислительной мощности приложений и увеличение числа пользователей, работающих с одним ПК.

4.Подсистема памяти. Методы повышения быстродействия памяти. Виды ЗУ. Иерархическая организация памяти. Какие вычислительные системы, на каком уровне иерархической организации требуют организации пакетного доступа к памяти. Ответ поясните.

Память любой ЭВМ состоит из нескольких видов памяти (оперативная, постоянная и внешняя - различные накопители). Память является одним из важнейших ресурсов. Поэтому операционная система управляет процессами выделения объемов памяти для размещения информации пользователей. В любых ЭВМ память строится по иерархическому принципу. Это обуславливается следующим:

Оперативная память предназначена для хранения переменной информации, так как она допускает изменение своего содержимого в ходе выполнения микропроцессором соответствующих операций. Поскольку в любой момент времени доступ может осуществляться к произвольно выбранной ячейке, то этот вид памяти называют также памятью с произвольной выборкой - RAM (Random Access Memory).

Все программы, в том числе и игровые, выполняются именно в оперативной памяти. Постоянная память обычно содержит такую информацию, которая не должна меняться в течение длительного времени. Постоянная память имеет собственное название - ROM (Read Only Memory), которое указывает на то, что ею обеспечиваются только режимы считывания и хранения.

452

АРХИТЕКТУРА ВЫЧИСЛИТЕЛЬНЫХ СИСТЕМ

С точки зрения пользователей желательно было бы иметь в ЭВМ единую сверх большую память большой производительности, однако емкость памяти и время обращения связаны между собой (чем больше объем тем больше время обращения к ней). Для упрощения все пересылки информации осуществляется не по вертикали, а через оперативную память. Кое-какие процедуры планирования теперь осуществляются компиляторами языков высокого уровня.

Существует противоречие, связанное с организацией ЗУ. Соблюдается тенденция увеличения объёма памяти при медленном росте её быстродействия. Требуется, чтобы скоростные характеристики процессора и памяти были одинаковы. Поэтому структура памяти имеет иерархическую организацию. Она бывает оперативной и внешней. Оперативная память делится на сверхоперативную и главную. Быстродействие сверхоперативной памяти соизмеримо или превышает быстродействие процессора. Обмен между каскадами оперативной памяти может осуществляться через ЦП или специальное устройство обмена. Сверхоперативная память имеет специальную организацию со своей внутренней схемой управления. Сверхоперативная память может строится по принципу многовходовой или ассоциативной памяти. Сверхоперативная память построенная по буферному принципу и называется кэш-памятью. Кэш память, как правило, строится по многоблочной архитектуре. с использованием алгоритмов ассоциативной обработки.

Различают 4 типа ЗУ:

–адресные;

–ассоциативные (информация отыскивается по

признаку);

–ортогональные (можно считывать данные как по ячейкам, так и по разрядам);

–стековая.

Функции системы памяти организуются (ограничиваются)

1.процессором

2.системным интерфейсом (он позволяет осуществить доступ к громадному адресному пространству)

3.Основанная память (Оперативная память)

4.ВЗУ (внешняя ЗУ)

453

АРХИТЕКТУРА ВЫЧИСЛИТЕЛЬНЫХ СИСТЕМ

ЦП (регистры)

СО сверхоперативная

ОП оперативная

ОП оперативная

Нвнешняя

НМЛ НО архивная

Уровни памяти:

Существуют структурные и алгоритмические методы повышения быстродействия памяти:

Структурные:

1.метод иерархической памяти

2.создание новых технологий и организации микросхем памяти.

Алгоритмические:

1.Пакетный доступ

2.Расслоение памяти

3.Метод блочной пересылки.

См (рис 6.1.)

Пакетный доступ Выборка широким словом. На входе порции данных

одинакового объема. На выходе n-слов. За одно обращение к ОП производится запись и чтение нескольких команд и слов. Сложность организации.

Расслоение памяти Используется для организации попеременного

обращения к разным физическим модулям при одновременной сокращении числа обращении к каждому модулю

Способы:

1.Расслоение с соответствием младшими адресами (конвейерный способ) рис. 6.4

2.Разделение памяти на память данных и память программ. Используется в системах управления и обработки сигналов. (Гавардская архитектура)

Метод блочной пересылки За один сеанс обмена передается не одна порция данных.

Используется при обращении к ВЗУ, а также подкачки

454

АРХИТЕКТУРА ВЫЧИСЛИТЕЛЬНЫХ СИСТЕМ

данных в кэш-память или локальную память процессора и данных.

Виды ЗУ

Структура адресного ЗУ.

Существует 2 вида адресов запоминающих устройств: статический и динамический.

Динамические ЗУ используют цикл регенерации, т.е. подзарядка ЗУ. Чем больше объём ЗУ, тем сложнее дешифрация адреса. Основное время записи:

t0зап=tc+tд+tзап; t0чтен=tд+tчт+tр tc – время стирания

tд – время дешифрации tзап – время записи

tчт – время чтения

tр – время регенерации

Время записи и чтения определяется технологией изготовления кристалла памяти. А время дешифрации как технологически, так и особенностями организации блока памяти, поэтому время дешифрации можно уменьшить.

Структура ассоциативной памяти.

Поиск информации осуществляется не по адресу, а по ассоциативному признаку. При этом поиск по ассоциативному признаку происходит парам. во времени для всех ячеек памяти. Ассоциативный поиск позволяет упростить и ускорить обработку информации. Это достигается за счёт того, что одновременно с выборкой происходит некоторая логическая обработка.

Запоминающий массив содержит N ячеек разрядностью N+1. Для указания занятости ячейки используется N-ный разряд. Если он установлен в 0 – ячейка свободна. По входной шине на регистр ассоциативного признака поступает N-разрядный ассоциативный запрос, а на регистр маски – код маски поиска. N- ный разряд регистра маски устанавливается в 0. Ассоциативный поиск производится для совокупности разрядов регистра ассоциативного признака, у которого регистр маски установлен в

1.

Для слов, у которых соответствующие разряды совпали с незамаскированными разрядами регистров ассоциативного признака, комбинационная схема устанавливает 1 в соответствующие разряды регистра совпадения. Регистр результата поиска просматривает содержимое регистра совпадения и формирует 3 выходных сигнала:

a0 – 0; a1 – 1; a2 – больше одного; (совпадения).

455

АРХИТЕКТУРА ВЫЧИСЛИТЕЛЬНЫХ СИСТЕМ

Обрабатывающее устройство, которое послало ассоциативный запрос на память по этим сигналам количество циклов чтения из памяти. Поиск данных в ассоциативной памяти может производиться с учётом различных методов индексации и адресации. Алгоритм индексации реализуется аппаратно или микропрограммно, и заменить его на другой нельзя.

Иерархическая организация памяти

Уровни иерархии памяти имеют каскадное включение. Обмен между каскадами осуществляется через ЦП (центральный процессор) или через специальное устройство обмена. Эффект повышения быстродействия от иерархической организации памяти будет больше, если данные, находящиеся на определенном уровне, будут многократно использоваться.

Пакетная организация требуется для взаимодействия между всеми уровнями памяти, за исключением регистры<->кэш процессора. Например, организация взаимодействия между оперативной память и внешней памятью идет через контроллер, который работает в пакетном режиме.

5. Организация кэш-памяти. Зарисуйте структуру памяти (ОЗУ и кэш) для секторированного наборноассоциативного кэша, состоящего из трех банков. Поясните её.

В современных процессорах используют 2 кэша: кэш команд, кэш данных.

Из всей памяти доступной процессору, кэшируется только динамическая память системной платы. И из этой памяти не кэшируется область, где хранятся общесистемные переменные и область для организации режима ПДП.

Рис. 6.3

Кэш память включает собственное буферное запоминающее устройство, в котором хранятся информационные блоки. Включает:

1.комбинационные схемы, необходимые для ассоциативного поиска признаков

2.запоминающие устройства для хранения таблиц адресов и таблиц активности

Процессор выполняет обмен только с оперативной памятью. Кэш контроллер перехватывает запрос и является посредником между процессором и оперативной памятью. Он должен обеспечивать обмен из кэш памяти данных когерентной памяти.

Рис 6.11

456

АРХИТЕКТУРА ВЫЧИСЛИТЕЛЬНЫХ СИСТЕМ

Если строка = блок, называется несекторированным.

Страницы ОП условно делятся на блоки. Кэш память разделена на строки. По системной шине данные передаются только блоками. Если размер строки = блоку, то кэш называется нескторированным. В каждой строке кэш памяти добавляется бит активности, который определяет занятость. Если строка КЭШа > блока, то кэш называют секторированным. Если строка КЭШа содержит несколько смежных блоков (секторов), такой кэш называют секторированным.

Существует 2 способа данных чтения из КЭШа.

1.Обращение к ОП начинается одновременно с кэш каталогом и в случае попадания прерывается.

2.Обращение к ОП начинается только после промаха.

15.3 стратегии:

1)Стратегия псевдослучайного выбора места

2)Стратегия наиболее редко используемого места

3)Стратегия не модифицируемого места

Современные кэш - контроллеры организуют стратегию упреждающего чтения, т.е. свободные циклы памяти будут записываться в кэш строки, которые вероятнее всего понадобятся процессору. При этом учитывается направление процесса данных процессора.

Записи данных:

1)Сквозная запись WT – выполнение каждой операции записи производится одновременно и в строку КЭШа и в ОП.

2)Буферная сквозная запись BWT – между кэш контроллером и ОП располагается кэш буфер имеющий

очередь на запись и на чтение (FIFO). Отложенная запись

457

АРХИТЕКТУРА ВЫЧИСЛИТЕЛЬНЫХ СИСТЕМ

выполняется во время свободных тактов шины. Если требуется прочитать блок который находится в буфере, то блок переписывается в очередь через чтение.

3)Данные заносятся в кэш и соответствующая строка помечается как модифицируемая. В ОП данные перемещаются только целой строкой в случае секторированного опроса или непосредственно перед её замещением новыми данными.

4)Буферная обратная запись.

В зависимости от способа определения, взаимного соответствия строки КЭШа и области основной памяти, выделяют 3 архитектуры кэш памяти:

1)КЭШ прямого отображения

2)Полностью ассоциативный КЭШ

3)Частично ассоциативный КЭШ (наборно - ассоциативный)

Наборно – ассоциативный КЭШ памяти

Рис. 6.14

Реализован компромисс между ассоциативным КЭШом и КЭШом прямого отображения. Здесь каждый блок памяти может претендовать на одну из нескольких строк КЭШа объединённых в набор. Номер набора в которм модет отображаться требуемый блок однозначно определяется адресом блока. С каждым набором связан признак определяющий строку набора подлежащего замещением в случае КЭШ-промаха.

Рис. 6.15

6. Операционный и командный конвейер. Необходимые условия организации конвейеров этих типов. Режимы работы конвейеров. Объясните, почему при организации конвейера команд не целесообразно использовать Принстонскую архитектуру ЭВМ?

Операционный конвейер (ОК) состоит из последовательности комбинационных схем, каждая из которых реализует определённый этап примитивной операции. Между комбинационными схемами располагаются регистры для хранения промежуточных результатов. Рис. 7.3 Такт работы определяется:

1)Задержка на распространение сигналов комбинационных схем.

458

АРХИТЕКТУРА ВЫЧИСЛИТЕЛЬНЫХ СИСТЕМ

2) |

Из |

задержки |

записи |

данных |

в |

регистр |

3) |

Время распространения сигнала по межсоединениям |

|||||

4) |

Время задержки синхроимпульса |

|

|

|||

Определяет коэффициент эффективности использования конвейера. Второстепенные операции.

В современных процессорах параллельно устанавливают от 2-32 операционных конвейеров. Комбинационные конвейера могут соединяться последовательно, образуя линейный конвейер или по схеме с обратными связями.

Рис. 7.6

Рассмотрим векторный конвейер системы рис. 7.7 в состав

которой входит векторный процессор рис. 7.8 |

|

||||

Пример: |

Пусть |

необходимо |

выполнить |

следующую |

|

последовательность |

|

|

|

||

1) |

LD |

L,A,V1 |

загрузка |

|

|

2) |

LD |

L,B,V2 |

загрузка |

|

скалярный |

регистр |

|

|

|

|

|

459