ВС для ГОС (ПИ) / Орлов, Цилькер - Организация ЭВМ (2004)

.pdf

3 3 8 Глава7. Операционныеустройства вычислительныхмашин

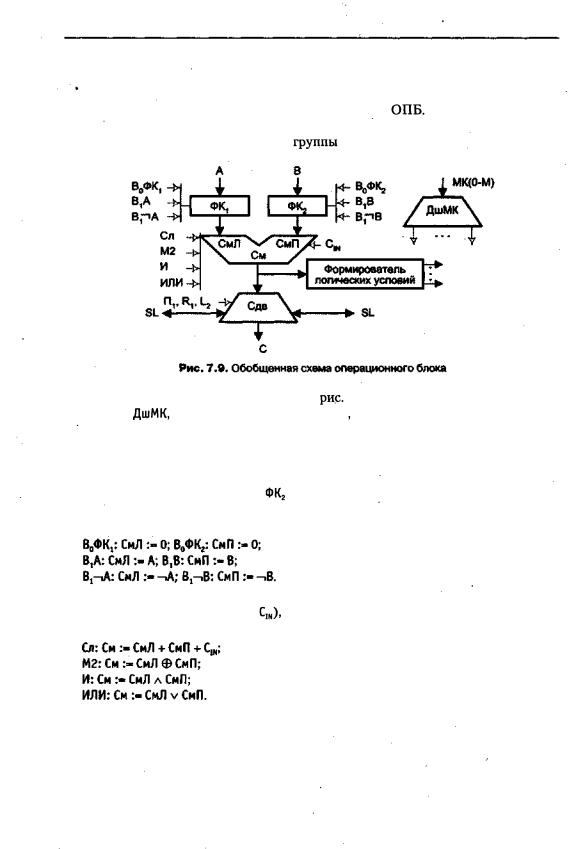

При сложении n-разрядных двоичных чисел (битзнака и п - 1 значащих цифр) возможен результат, содержащий п значащих цифр. Эта ситуация известна как переполнение. «Лишний» бит занимает позицию знака, что приводит к некорректности результата. Естественно, что ОПУ должно обнаруживать факт переполнения и сигнализировать о нем. Для этого используется следующее правило: если суммируютсядвачислаиониобаположительныеилиобаотрицательные, переполнениеимеетместотогдаатолькотогда,когдазнакрезультатапротивоположен знаку слагаемых. Рисунки 7.10, д и 7.10, е показывают примеры переполнения. Обратим внимание, что переполнение не всегда сопровождается переносом из знакового разряда.

Рис. 7 . 1 1 . Примеры выполнения операции вычитания вдополнительном коде: а,б,в, г— вычитание без возникновения переполнения; л, в — вычитание с переполнением

Вычитаниевыполняетсявсоответствиисправилом:длявычитанияодногочисда(вычитаемого)издругого(уменьшаемого)необходимовзятьдополнениевычитаемогоиприбавитьегокуменьшаемому.Поддополнениемздесьпонимаетсявычитаемое с противоположным знаком, представленное в дополнительном коде. Вычитание иллюстрируется примерами (рис. 7.11). Два последних примера (см. рис. 7.11, д и 7.1 \,е) демонстрируют ранее рассмотренное правило обнаружения переполнения.

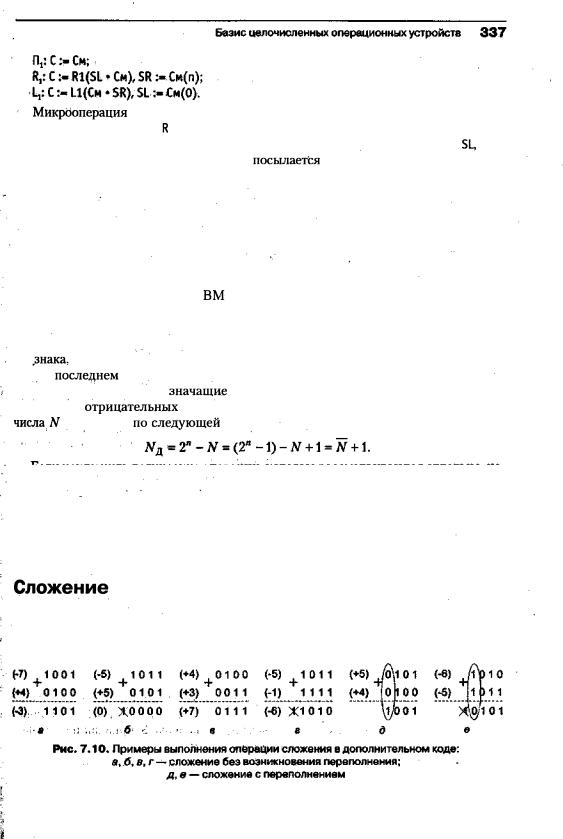

Чтобы упростить обнаружение ситуации переполнения, часто применяется так называемый модифицированный дополнительный код, когда для хранения знака отводятся два разряда, причем оба участвуют в арифметической операции наравне с цифровыми разрядами. В нормальной ситуации оба знаковых разрядах содержат одинаковые значения. Различие в содержимом знаковых разрядов служит признаком возникшего переполнения (рис. 7.12).

Рис. 7.12. Примеры выполненияоперациисложения вмодифицированномдополнительном коде: в, б — переполнения нет; в, г — возникло переполнение

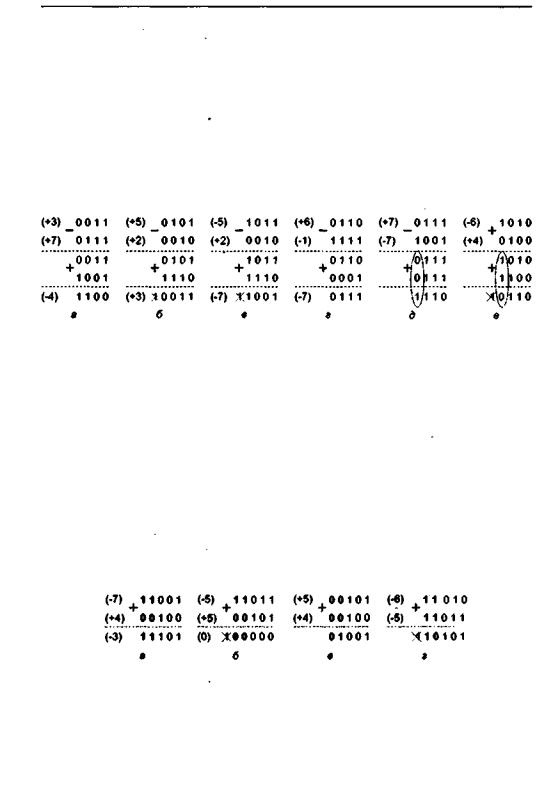

На рис. 7.13 показана возможная структура операционного блока для сложения и вычитания чисел сознаком в формате с фиксированной запятой. Центральным звеном устройства является n-разрядный двоичный сумматор. ОперандА поступает на вход сумматора без изменений. Операнд В предварительно пропускается

Целочисленное умножение 3 3 9

через схемы сложения по модулю 2, поэтому вид кода В, поступающего на другой вход сумматора, зависит от выполняемой операции. Если задана операция сложения (управляющий код 0), то результат на выходе ОПБ определяется выражением S.= А + В. При операции вычитания (управляющий код 1) на вход сумматора подаютсяинверсныезначения всехразрядовВ,и,крометого, навходпереносавмладший разряд сумматораСlN поступает 1. В итоге на выходе ОПБ будет S = А + В + 1, что соответствует прибавлению к А числа В с противоположным знаком, то есть вычитанию.

Рис.7.13.Структураоперационногоблокадлясложенияивычитания

На рис. 7.13 не показана схема формирования признака переполнения V, который согласно описанным ранее правилам определяется логическим выражением

Целочисленное умножение

По сравнению со сложением и вычитанием, умножение — более сложная операция, как при программном, так и при аппаратном воплощении. В ВМ применяются различные алгоритмы реализации операции умножения и, соответственно, несколько схем построения операционных блоков, обеспечивающих выполнение операции умножения.

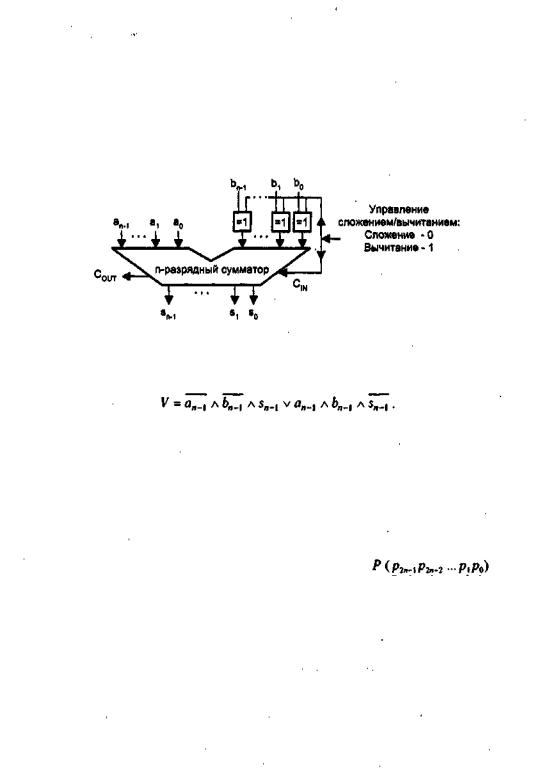

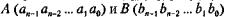

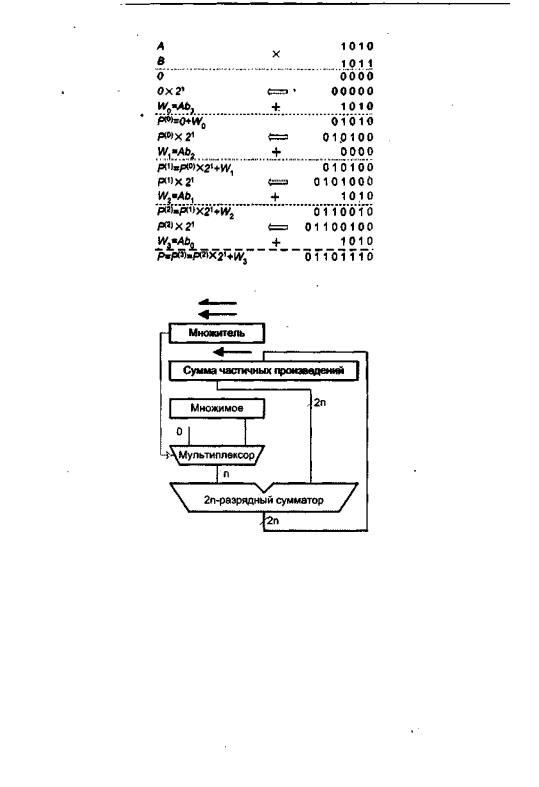

Традиционная схема умножения похожа на известную из школьного курса процедуру записи «в столбик». Вычисление произведения двух n-разрядных двоичных чисел без знака  сводится к формированию частичных произведений (ЧП) Wi по одному на каждую цифру множителя, с последующим суммированием полученных ЧП. Перед суммированием каждое частичное произведение должно быть сдвинуто наодин разряд относительно предыдущего согласно весу цифры множителя, которой это ЧП соответствует. Поскольку операндами являются двоичные числа, вычисление ЧП упрощается — если цифра множителя bi равна 0, то Wi тоже равно 0, а при bi - 1 частичное произведение равно множимому (Wi-A). Перемножение двух n-раз- рядных двоичных чисел Р - А х В приводит к получению результата, содержащего 2n битов. Таким образом, алгоритм умножения предполагает последовательное выполнение двух операций — сложения и сдвига (рис. 7.14). Суммирование ЧП обычно производится не на завершающем этапе, а по мере их получения. Это по-

сводится к формированию частичных произведений (ЧП) Wi по одному на каждую цифру множителя, с последующим суммированием полученных ЧП. Перед суммированием каждое частичное произведение должно быть сдвинуто наодин разряд относительно предыдущего согласно весу цифры множителя, которой это ЧП соответствует. Поскольку операндами являются двоичные числа, вычисление ЧП упрощается — если цифра множителя bi равна 0, то Wi тоже равно 0, а при bi - 1 частичное произведение равно множимому (Wi-A). Перемножение двух n-раз- рядных двоичных чисел Р - А х В приводит к получению результата, содержащего 2n битов. Таким образом, алгоритм умножения предполагает последовательное выполнение двух операций — сложения и сдвига (рис. 7.14). Суммирование ЧП обычно производится не на завершающем этапе, а по мере их получения. Это по-

3 4 0 Глава 7. Операционные устройства вычислительных машин

зволяет избежать необходимости хранения всех ЧП, то есть сокращает аппаратурные издержки. Согласно данной схеме, устройство умножения предполагает наличие регистров множимого, множителя и суммы частичных произведений, а также сумматора ЧП и, возможно, схем сдвига, если операция сдвига не реализована иным способом, например за счет «косой» передачи данных между узлами умножителя.

Рис. 7.14. Общаясхема умножениясосдвигом суммы частичных произведений влевоиливправо

В зависимости от способа получения суммы частичных произведений (СЧП) возможны четыре варианта реализации «традиционной» схемы умножения [10]:

1.Умножение, начиная с младших разрядов множителя, со сдвигом суммы частичных произведений вправо и при неподвижном множимом.

2.Умножение, начиная со старших разрядов множителя, при сдвиге суммы частичных произведений влево и неподвижном множимом.

3.Умножение, начиная с младших разрядов множителя, при сдвиге множимого влево и неподвижной сумме частичных произведений.

4.Умножение, начиная со старших разрядов множителя, со сдвигом множимого вправо и при неподвижной сумме частичных произведений.

Варианты со сдвигом множимого на практике не используются, поскольку для их реализации регистр множимого, регистр СЧП и сумматор должны иметь разрядность2n,поэтому остановимся на вариантах 1 и 2. Первый из них назовем алго- ритмомсдвигавправо,авторой—алгоритмомсдвигавлево.

Умножение чисел без знака

Общую процедуру традиционного умножения сначала рассмотрим применительно к числам без знака, то есть таким числам, в которых все п разрядов представляют значащие цифры.

Алгоритм сдвига вправо

Алгоритм сводится к следующим шагам:

1.Исходное значениесуммы частичных произведений принимается равным нулю.

2.Анализируется очередная цифра множителя (анализ начинается с младшей цифры). Если она равнаединице, то к СЧП прибавляется множимое, в противном случае (цифра равна нулю) прибавление не производится.

Целочисленное умножение 3 4 1

3.Выполняется сдвиг суммы частичных произведений вправо на один разряд,

4.Пункты 2 и 3 последовательно повторяются для всех цифровых разрядов множителя.

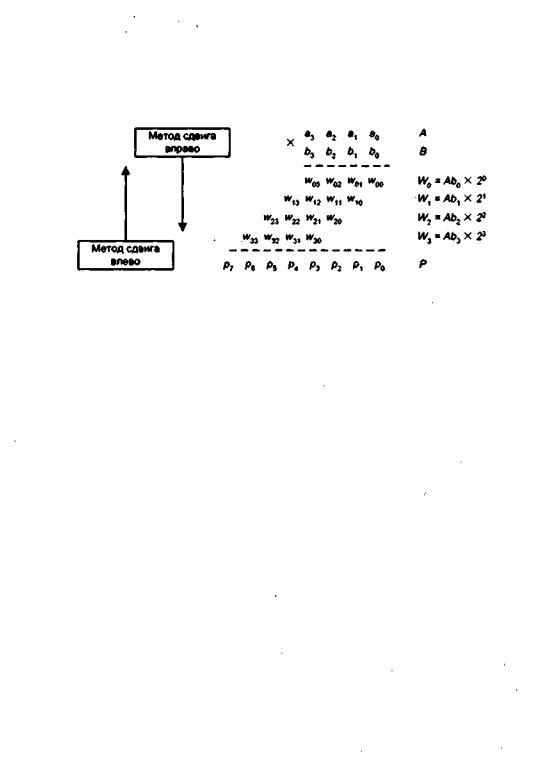

Процедура умножения иллюстрируется примером вычисления произведения 10x11 (рис. 7.15)

Рис. 7.15. Примерумножения сосдвигом суммы частичныхпроизведений вправо

Рис. 7.16. Схемаустройства умножения по алгоритмуправого сдвига

Первоначально множимое и множитель заносятся вn-разрядныерегистры множимого (РМт) и множителя (РМт) соответственно, а все разряды 2n-разрядного регистра суммы частичных произведений (РЧП) устанавливаются в 0. Умножение происходит за n шагов. На каждом шаге, в зависимости от состояния младшего разряда регистра множителя, управляющего мультиплексором, на один из входов

3 4 2 Глава7. Операционные устройства вычислительныхмашин

«-разрядного сумматора подается либо множимое, либо 0. На второй вход поступает содержимое п старших разрядов РЧП. Новое частичное произведение из сумматора пересылается в старшие разряды РЧП. Далее содержимое РЧП сдвигается на один разряд вправо, причем в освободившийся старший разряд регистра заносится значение переноса из старшего разряда сумматора. Поскольку мультиплексор управляется младшим разрядом РМт, тосодержимое этого регистра такжесдвигается на один разряд вправо. Описанная последовательность повторяется п раз. Более экономичным в плане аппаратуры является иное решение, когда вместодвух регистров — n-разрядного РМт и 2м-разрядного РЧП — используется один комбинированный 2л-разрядный регистр (показан на рис 7.16 справа). Множитель первоначально заносится в младшие п разрядов этого регистра, а старшие разряды обнуляются. По мере сдвигов вправо младшие, уже проанализированные разряды множителя выталкиваются из регистра, освобождая место для очередной цифры СЧП. Обычно такой регистр строится из двух n-разрядных регистров, объединенных цепями сдвига. Дополнительно отметим, что если очередная цифра множителя равна 1, то для вычисления суммы ЧП требуются операции сложения и сдвига, а при нулевой цифре множителя в принципе можно обойтись без сложения, ограничившись только сдвигом. Это, естественно, требует некоторого видоизменения схемы.

Алгоритм сдвига влево

Процедура традиционного умножения со сдвигом влево включает в себя следующие шаги:

1.Исходноезначение суммы частичных произведений принимается равным нулю.

2.Анализируется очередная цифра множителя (анализ начинается со старшей цифры). Если онаравна единице, то к СЧП прибавляется множимое, в противном случае (цифра равна нулю) прибавление не производится.

3.Выполняется сдвиг суммы частичных произведений влево на один разряд.

4.Пункты 2 и 3 последовательно повторяются для всех цифровых разрядов множителя.

На рис. 7.17 приведен пример умножения со сдвигом влево(10х 11).

Описанная процедура может быть реализована с помощью схемы, показанной на рис. 7.18.

К преимуществу алгоритма сдвига влево следует отнести то, что он позволяет совмещать во времени операции сложения и сдвига. Однако, по сравнению с алгоритмом сдвига вправо, он имеет и ряд недостатков. В первую очередь, СЧП и множитель не могут совместно использовать один и тот же регистр. Для реализации алгоритма требуется 2х-разрядный сумматор. Кроме того, схема со сдвигом влево неудобна при выполнении умножения над числами с разными знаками.

Тем не менее окончательный выбор между алгоритмами сдвига вправо или влево не однозначен. Так, если в результате умножения требуется результат только одинарной длины, то вариант со сдвигом влево может оказаться в аппаратурном плане выгоднее, поскольку не принуждает вводить дополнительные цепи сдвига. Конечный выбор определяется соотношением затрат оборудования на реализацию цепей сдвига и дополнительных разрядов сумматора.

Целочисленное умножение 3 4 3

Рис. 7.17. |

й влево |

Рис. 7.18. Схема устройства умножения по алгоритму левого сдвига

Умноженижнеко,Неск2рnуы.-йраВотличаютсяхчтз,дальнприведенноггдпятвселькболзнаковыйхжителчевидВМй—слйшемхфкаобщепакполттическусловчисларзсодечисемыслапинобтельноиучаствуезриняржадбезмся.о7значениакпрямодел.пред19,отделятсь —гд(вс.получитрзнакоммтавлятСправедлумнстаршпоказа.ьПчислазнаковыйложь,ьчислм.абсципрразрядтеВемтерицаодвлстьцессьныумнчиютныеоичнойряддзнакгслльчислзначениоства)моызнакцжчкой,рв фстезаписываютшениэтомормров-я1я,чисзнкогдямвидреефбывчларазрядами+13щуюкставлениnьдо-иря,трицфоприв+10днаанпеие-.

3 4 4 Глава 7, Операционные устройства вычислительных машин

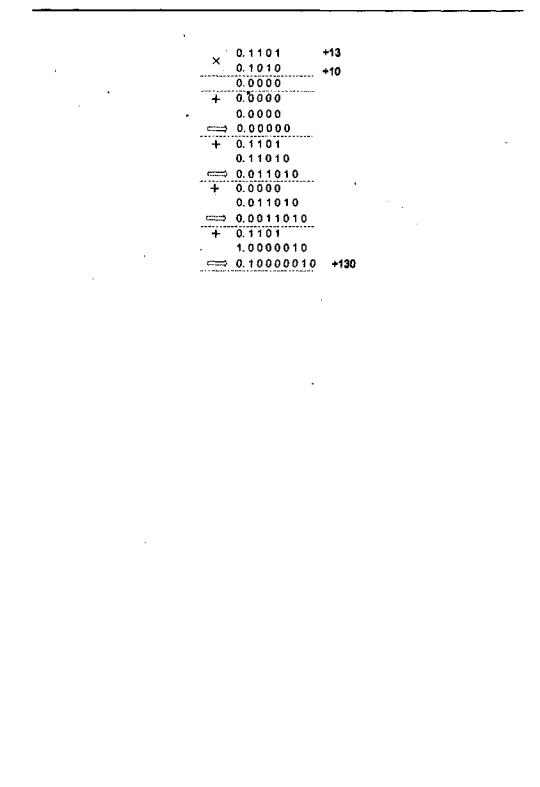

Рис. 7.19. Умножениечисел при положительныхсомножителях

тельного числа в дополнительном коде сводится к инвертированию всех цифровых разрядов числа, представленного в прямом коде, и прибавлению единицы к младшему разряду получившегося после инвертирования обратного кода. Поэтой причине более предпочтительны варианты, не требующие преобразования сомножителей и обеспечивающие вычисления непосредственно в дополнительном коде.

Задержимся на особенностях операции умножения при различных сочетаниях знаковсомножителей. Первая изнихпроявляется при выполненииоперации арифметического сдвига вправо для суммы частичных произведений — освободившиеся при сдвиге цифровые позиции должны заполняться не нулем, а значением знакового разряда сдвигаемого числа. Здесь, однако, следует учитывать, что это правило заполнения освободившихся цифровых разрядов начинает действовать лишь с момента, когда среди анализируемых разрядов множителя появляется первая единица.

Множимое произвольного знака, множитель положительный

Пример для положительных сомножителей (Л>=О, В>=0) уже был рассмотрен. Б случае отрицательного множимого процедура умножения протекает аналогично, с учетом сделанного замечания об арифметическом сдвиге СЧП, что подтверждает пример, приведенный на рис. 7.20.

Поскольку результат умножения отрицательный, он получается в дополнительном коде.

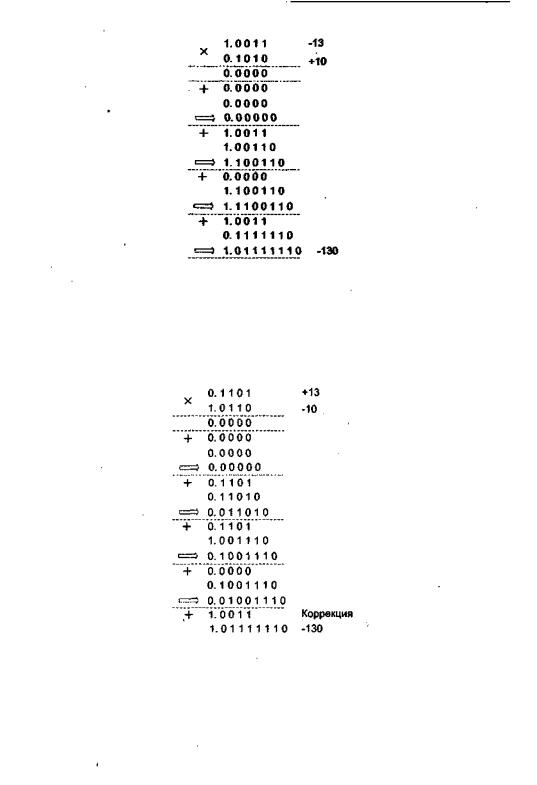

Множимое произвольного знака, множитель отрицательный

Так как множитель отрицателен, он записывается в дополнительном коде:

[В]л- 2n -|В|, и в цифровых разрядах кода будет представлено число |

2n-1 -|В|. |

При типовом умножении (как в случае В > 0) получим Р = А (2n-1 |

- |В||) - |

= -|В| *А + А *2n-1. ПсевдопроизведениеР больше истинного произведения Р на

Целочисленное умножение 3 4 5

Рис. 7.20, Умножение чисел приотрицательном множимом и положительном множителе

величину А х 2n-1, что и необходимо учитывать при формировании окончательного результата. Для этого перед последним сдвигом из полученного псевдопроизведения необходимо вычесть избыточный член. На рис. 7.21 и 7.22 приведены примеры умножения положительного и отрицательного множимого на отрицательный множитель, в которых видна упомянутая коррекция результата

Рис.7.21.Умножениечиселпри положительноммножимомиотрицательноммножителе

Рассмотренные процедуры умножения чисел со знаком в принципе могут быть реализованы с помощью ранее рассмотренного устройства (см. рис. 7,16). На практике для перемножения чисел со знаком применяют иные алгоритмы. Наиболее распространенным из них является алгоритм Бута, имеющий дополнительное преимущество, — он ускоряет процессумножения посравнению с рассмотренным ранее. Этот алгоритм будет рассмотрен ниже.