ВС для ГОС (ПИ) / Котельников - Вычислительные машины, системы и сети

.pdf

|

+Uпит |

|

+Uпит |

|

|

|

|

|

|

|

R |

|

|

Uвых |

Uвых |

|

|

|

|

U1 |

U2 |

U1 |

U2 |

|

а |

б |

Рис. 3.10. Вентиль ИЛИ-НЕ: а – схема на переключателях; б – схема на транзисторах

Чтобы понять, почему реализуются именно такие функции, можно воспользоваться известным нам правилом, что выходное напряжение является инверсным к току. Проанализируйте, для каких U1, U2 ток течет, а для каких нет.

Задание. Составить таблицы истинности для этих вентилей.

U1 |

U2 |

Uвых (И-НЕ) |

Uвых (ИЛИ-НЕ) |

|

|

|

|

0 |

0 |

|

|

|

|

|

|

0 |

1 |

|

|

|

|

|

|

1 |

0 |

|

|

|

|

|

|

1 |

1 |

|

|

|

|

|

|

Задание. Нарисовать схемы вентилей AND, OR и XOR.

Обозначения пяти основных вентилей на электрических схемах приведены на рис. 3.11а – российский стандарт (ГОСТ 2.743-91) и на рис. 3.11б –

зарубежный стандарт (ANSI/IEEE Std 91-1984).

71

НЕ (NOT) |

|

|

И-НЕ (NAND) |

|

ИЛИ-НЕ (NOR) |

И (AND) |

|

|

ИЛИ (OR) |

|

Исключающее |

||||||||||||

|

|

|

|

|

|

ИЛИ (XOR) |

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

& |

|

|

|

1 |

|

|

|

& |

|

|

1 |

|

|

|

=1 |

|

|

||

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

а

б

Рис. 3.11. Основные вентили:

а – российский стандарт; б – зарубежный стандарт

Вентили И и ИЛИ получаются путем подключения инверторов к выходам вентилей И-НЕ и ИЛИ-НЕ. Таким образом, вентили И-НЕ и ИЛИ-НЕ требуют по два транзистора, а вентили И и ИЛИ – по три. Поэтому в большинстве компьютеров используются вентили И-НЕ и ИЛИ-НЕ. (На практике все вентили выполняются несколько сложнее, но вентили И-НЕ и ИЛИ-НЕ все равно проще, чем вентили И и ИЛИ.) Вентили могут иметь более двух входов (до восьми) и в этом случае называются 3И-НЕ, 4И-НЕ и т. д.

3.3.2. Реализация булевых функций

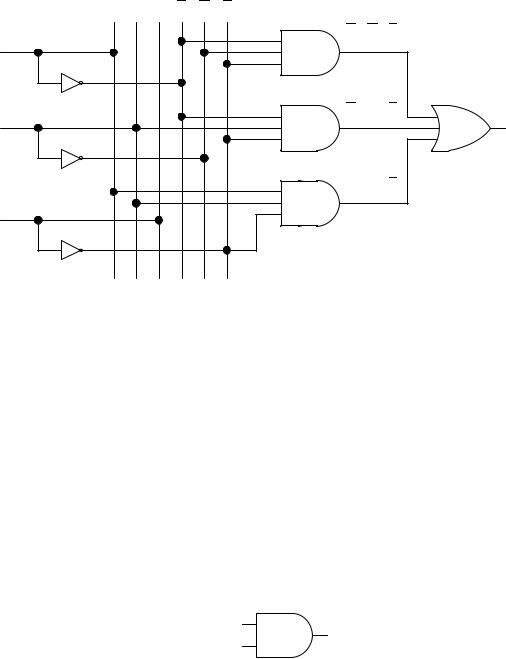

Чтобы реализовать булевы функции на вентилях, используют формульное задание функций.

Пример. Реализовать булеву функцию (см. пример в параграфе 2.3):

f x, y, z x y z x y z x y z .

72

x |

y |

z |

x |

y |

z |

|

|

|

|

|

|

x y z |

|

x |

|

|

|

|

|

|

|

|

|

|

|

x y z |

f x, y, z |

y |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

x y z |

|

z |

|

|

|

|

|

|

Рис. 3.12. Реализация функции f x, y, z (вертикальные линии проведены для удобства изображения)

В примере показана реализация функции с помощью вентилей НЕ, И, ИЛИ. Однако проще строить схемы, используя только один тип вентилей. Вентили И-НЕ и ИЛИ-НЕ считаются полными, так как можно построить любую булеву функцию, используя только вентили И-НЕ или только вентили ИЛИ-НЕ.

3.3.3. Использование вентиля AND в качестве ключа

Рассмотрим двухвходовой вентиль AND. Обозначим его входы так, как приведено на рис. 3.13.

Вход данных

Выход

Вход

управления

Рис. 3.13. Двухвходовой вентиль AND

Таблица истинности этого элемента:

Вход управления |

Вход данных |

Выход |

|

|

|

0 |

0 |

0 |

|

|

|

0 |

1 |

0 |

|

|

|

1 |

0 |

0 |

|

|

|

1 |

1 |

1 |

|

|

|

73

Анализируя таблицу, можно заметить, что при Управлении = 0 на выходе получается 0, независимо от входа данных, а при Управлении = 1 на выходе повторяется вход данных. Таким образом, вентиль AND можно использовать в роли ключа (переключателя), пропуская или не пропуская данные на выход схемы в зависимости от входа управления. Такая возможность окажется очень полезной в нескольких схемах, рассматриваемых далее.

Отметим, что входов у вентиля AND, используемого в качестве ключа, может быть не два, а больше. В этом случае все входы, кроме одного входа данных, будут являться управляющими.

3.3.4. Использование вентиля XOR в качестве управляемого инвертора

По аналогии с предыдущим параграфом рассмотрим двухвходовой вентиль XOR (рис. 3.14).

Вход данных

Выход

Вход

управления

Рис. 3.14. Двухвходовой вентиль XOR

Таблица истинности вентиля XOR:

Вход управления |

Вход данных |

Выход |

|

|

|

0 |

0 |

0 |

|

|

|

0 |

1 |

1 |

|

|

|

1 |

0 |

1 |

|

|

|

1 |

1 |

0 |

|

|

|

При Управлении = 0 на выходе повторяются входные данные, а при Управлении = 1 выход является инверсным ко входу. Таким образом, элемент XOR при нулевом сигнале управления работает как повторитель, а при единичном – как инвертор, т. е. является управляемым инвертором.

3.3.5. Преобразователи кодов

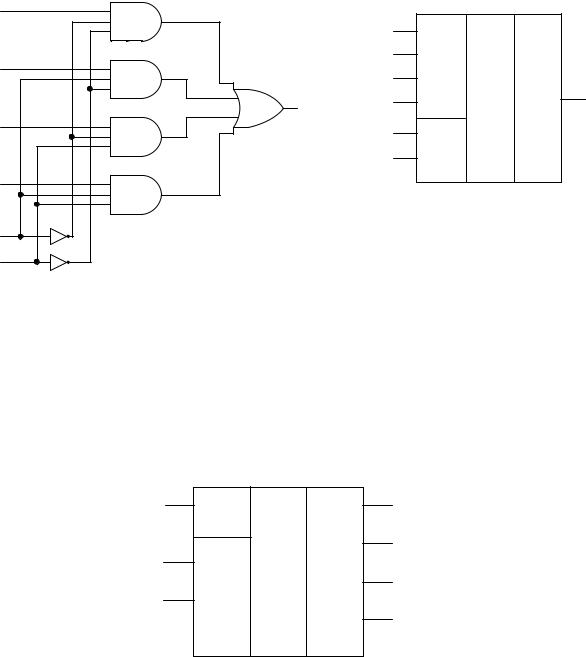

Шифратор (coder, CD) – преобразователь, в котором при подаче сигнала на один из входов на выходе появляется двоичный код этого входа (рис. 3.15).

Если в шифраторе n выходов, то он имеет 2n входов.

74

Таблица истинности шифратора:

Входы |

Y1 |

Y0 |

|

|

|

Х0 |

0 |

0 |

|

|

|

Х1 |

0 |

1 |

|

|

|

Х2 |

1 |

0 |

|

|

|

Х3 |

1 |

1 |

|

|

|

По таблице истинности можно вывести логические функции Y0 и Y1:

|

|

|

|

|

Y0 = X1 X3; |

|

Y1 = X2 X3 |

|

|

|

||||

X0 |

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|||||||

X1 |

|

|

|

|

Y0 |

|

|

X0 |

CD |

Y0 |

|

|||

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

X1 |

|

Y1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

||

X2 |

|

|

|

|

|

|

|

|

|

|

X2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

Y1 |

|

|

X3 |

|

|

|

||

|

|

|

|

|

|

|

|

|

||||||

X3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

а |

|

|

|

|

б |

|

||||||

|

|

|

|

|

|

|

|

|

|

|||||

Рис. 3.15. Шифратор 42 (4 входа 2 выхода):

а – реализация на вентилях; б – обозначение на схемах

Дешифратор (decoder, DC) – преобразователь, в котором при подаче двоичного кода на вход на соответствующей выходной линии появляется сигнал (рис. 3.16).

Таблица истинности дешифратора:

Входы |

|

Выходы |

|

||

|

|

|

|

|

|

Х1 |

Х0 |

Y3 |

Y2 |

Y1 |

Y0 |

|

|

|

|

|

|

0 |

0 |

0 |

0 |

0 |

1 |

|

|

|

|

|

|

0 |

1 |

0 |

0 |

1 |

0 |

|

|

|

|

|

|

1 |

0 |

0 |

1 |

0 |

0 |

|

|

|

|

|

|

1 |

1 |

1 |

0 |

0 |

0 |

|

|

|

|

|

|

75

Логические функции имеют вид: |

|

|

|

|

|

Y0 X 0 X1 ; |

Y1 X 0 X1 ; |

Y2 X 0 X1 ; |

Y3 X 0 X1 . |

||

X0 |

X0 X1 X1 |

|

|

|

|

|

|

Y0 |

|

|

|

|

|

|

X0 |

DC |

Y0 |

X0 |

|

Y1 |

X1 |

|

Y1 |

|

|

|

|

||

|

|

|

|

Y2 |

|

|

|

|

|

|

|

|

|

|

|

|

Y3 |

X1 |

|

Y2 |

|

|

|

|

|

|

|

|

|

|

|

Y3 |

|

|

|

|

а |

|

|

б |

|

|

Рис. 3.16. Дешифратор 24: |

|

|

|

|

а – реализация на вентилях; б – обозначение на схемах |

|

|

|||

3.3.6. Коммутаторы

Мультиплексор (multiplexer, MUX) – схема, обеспечивающая передачу информации, поступающей по нескольким входам на один выход. Выбор входной линии осуществляется при помощи адресных входов (рис. 3.17).

Если в мультиплексоре n адресных линий, то максимальное количество входов может быть 2n.

Четыре вентиля AND используются в этой схеме в качестве ключей. Сигналы на двух нижних входах каждого вентиля AND являются управляющими и определяют, будет ли проходить на выход сигнал данных с верхнего входа. Две адресные линии А0 и А1 кодируют 2-битное число (0..3), которое указывает, какая из четырех входных линий данных D0–D3 должна соединяться с выходом F. Каждый вентиль AND запускается определенной комбинацией адресных входов.

76

D0 |

|

|

|

|

|

D0 |

MUX |

|

|

D1 |

|

D1 |

|

D2 |

|

|

|

|

|

|

F |

D3 |

F |

|

|

||

|

|

|

|

D2 |

|

A0 |

|

|

|

|

|

|

|

A1 |

|

D3 |

|

|

|

A0 |

|

|

|

A1 |

|

|

|

|

а |

|

б |

Рис. 3.17. 4-входовой мультиплексор:

а – реализация на вентилях; б – обозначение на схемах

Демультиплексор (demultiplexer, DMX) – схема, обеспечивающая передачу информации, поступающей по одному входу на один из нескольких выходов. Выбор выходной линии осуществляется при помощи адресных вхо-

дов (рис. 3.18).

D DMX F0

F1

A0

F2

A1

F3

Рис. 3.18. Демультиплексор

Задание. Построить схему демультиплексора из вентилей самостоятельно (аналогично мультиплексору).

3.3.7. Двоичная арифметика

Переполнение и перенос

Основной проблемой при выполнении арифметических операций в компьютере является переполнение (overflow) – ситуация, когда ответ не помещается в отведенную для него ячейку памяти (выходит за пределы допу-

77

стимого диапазона). Переполнение нужно строго контролировать, иначе при вычислениях могут появиться неверные ответы.

Ситуации переполнения при арифметических операциях с беззнаковыми и со знаковыми типами данных принципиально отличаются.

За переполнение при операциях с беззнаковыми типами данных в процессоре отвечает специальная ячейка памяти размером 1 бит, которая называется флаг переноса (carry flag, CF). Если флаг переноса равен 1, значит в результате последней выполненной арифметической операции над беззнаковыми данными произошло переполнение.

Переполнение при операциях со знаковыми типами данных в процессоре контролируется флагом переполнения (overflow flag, OF)1. Если флаг переполнения равен 1, то в результате последней выполненной арифметической операции над знаковыми данными произошло переполнение.

Важно понимать, что в случае операций сложения и вычитания для процессора не имеет значения, над какими данными производятся эти операции – знаковыми или беззнаковыми. Процессор складывает и вычитает двоичные числа по единым правилам, и за счет использования дополнительного кода ответы получаются правильными как в случае беззнаковых типов, так и в случае знаковых.

Поэтому не существует разных машинных команд для сложения/вычитания знаковых и беззнаковых типов, команды в том и другом случае используются одинаковые – ADD (addition) для сложения и SUB (subtract) для вычитания. При этом в процессоре одновременно формируются оба флага CF и OF по разным правилам и программист может контролировать тот или другой флаг в зависимости от того, с каким типом данных в настоящий момент идет работа.

С другой стороны, умножение и деление выполняются по разным правилам для беззнаковых и знаковых данных, поэтому соответствующие машинные команды разные.

Флаг переноса CF отвечает за переполнение при операциях с беззнаковыми типами, флаг переполнения OF отвечает за переполнение при операциях со знаковыми типами; вычисляются эти флаги по-разному, одновременно и независимо друг от друга2.

1Реализуются флаги переноса и переполнения в виде разрядов специального регистра процессора – регистра флагов (о регистрах речь в пособии пойдет ниже). Хорошие отладчики в разных средах программирования обычно позволяют просматривать состояния флагов переноса и переполнения.

2Не должно вводить в заблуждение терминологическое несоответствие – флаг переполнения OF, несмотря на название, отвечает только за переполнение при работе со знаковыми типами данных. Флаг переноса CF не всегда равен переносу из старшего разряда и на самом деле отвечает за переполнение при действиях с беззнаковыми типами данных.

78

Сложение беззнаковых типов данных

Правило 1. При сложении чисел, представленных в беззнаковых типах

данных, переполнение возникает в том случае, если есть перенос из старше-

го разряда результата.

Рассмотрим различные варианты сложения на примере 4-разрядного беззнакового типа с диапазоном [0..15].

Сложение без переполнения (без выхода результата из диапазона):

(+4) |

+ |

0 |

1 |

0 |

0 |

(+5) |

+ |

0 |

1 |

0 |

1 |

|

(+3) |

0 |

0 |

1 |

1 |

|

(+10) |

1 |

0 |

1 |

0 |

||

(+7) |

|

0 |

1 |

1 |

1 |

(+15) |

|

1 |

1 |

1 |

1 |

|

|

CF = 0 |

|

|

|

|

CF = 0 |

|

|

||||

Поскольку перенос из старшего разряда результата отсутствует, то флаг переноса CF = 0 и беззнакового переполнения нет, поэтому ответы оказываются верными.

Сложение с переполнением:

(+4) |

+ 0 |

1 |

0 |

0 |

(+15) |

+ 1 |

1 |

1 |

1 |

|

(+12) |

1 |

1 |

0 |

0 |

|

(+15) |

1 |

1 |

1 |

1 |

(0) |

1 0 |

0 |

0 |

0 |

(+14) |

1 1 |

1 |

1 |

0 |

|

|

CF = 1 |

|

|

|

|

CF = 1 |

|

|

||

В этих примерах перенос из старшего разряда результата есть (зачеркнутая единица), но поскольку мы имеем всего 4 разряда, этот перенос в результате не остается, а уходит во флаг переноса CF. Таким образом, имеет место беззнаковое переполнение, и результаты сложения оказываются неверными (выход результатов за диапазон).

Сложение знаковых типов данных

Правило 2. При сложении чисел, представленных в знаковых типах

данных, переполнение возникает в том случае, если складываются два числа

с одинаковыми знаками, а знак результата противоположен знаку слагаемых.

79

Напомним, что за знак отвечает старший бит числа.

Следствие из правила 2: знаковое переполнение не может возникнуть при сложении чисел с разными знаками.

Примеры будем разбирать также в 4-разрядном, но уже знаковом типе данных с диапазоном [–8..+7].

Сложение без переполнения (жирным выделены старшие знаковые разряды чисел):

(+4) |

+ |

0 |

1 |

0 |

0 |

(+7) |

+ |

0 |

1 |

1 |

1 |

|

(–8) |

+ |

1 |

0 |

0 |

0 |

( 6) |

+ |

1 |

0 |

1 |

0 |

||

(+3) |

|

0 |

0 |

1 |

1 |

|

(–5) |

|

1 |

0 |

1 |

1 |

|

(+7) |

|

0 |

1 |

1 |

1 |

|

(–2) |

|

1 |

1 |

1 |

0 |

(+7) |

|

0 |

1 |

1 |

1 |

(+2) |

1 |

0 |

0 |

1 |

0 |

|

(–1) |

|

1 |

1 |

1 |

1 |

|

(–8) |

1 |

1 |

0 |

0 |

0 |

|

|

OF = 0 |

|

|

|

|

OF = 0 |

|

|

|

|

OF = 0 |

|

|

|

|

OF = 0 |

|

|

||||||||

Заметьте, что, несмотря на наличие во втором и четвертом примерах переноса из старшего разряда, результат знакового сложения оказывается правильным и флаг OF = 0. Это ещё раз подтверждает тот факт, что знаковое и беззнаковое переполнения возникают независимо друг от друга.

Сложение с переполнением:

(+4) |

+ |

0 |

1 |

0 |

0 |

(+7) |

+ |

0 |

1 |

1 |

1 |

|

(–8) |

+ |

1 |

0 |

0 |

0 |

|

(–5) |

+ |

1 |

0 |

1 |

1 |

|

(+4) |

|

0 |

1 |

0 |

0 |

|

(+2) |

|

0 |

0 |

1 |

0 |

|

(–2) |

|

1 |

1 |

1 |

0 |

|

(–4) |

|

1 |

1 |

0 |

0 |

(–8) |

|

1 |

0 |

0 |

0 |

|

(–7) |

|

1 |

0 |

0 |

1 |

(+6) |

1 |

0 |

1 |

1 |

0 |

(+7) |

1 |

0 |

1 |

1 |

1 |

||

|

OF = 1 |

|

|

|

|

OF = 1 |

|

|

|

|

OF = 1 |

|

|

|

|

OF = 1 |

|

|

||||||||

В каждом из последних примеров срабатывает Правило 2 и имеет место ситуация переполнения, следовательно, ответ получается неверным.

Замечание. При сложении чисел, представленных в знаковых типах данных, может применяться альтернативное правило переполнения: пере-

полнение возникает, когда перенос в старший разряд отличается от переноса из старшего разряда.

Примеры (с переполнением):

80